CD Uniformity Specs: JEDEC JESD89-3 Guidelines

JUL 28, 2025 |

Critical Dimension (CD) uniformity is a vital parameter in semiconductor manufacturing, ensuring that features across a wafer maintain consistent dimensions. The JEDEC JESD89-3 guidelines provide a framework for assessing and maintaining CD uniformity, critical in achieving high-yield production and reliable performance of semiconductor devices.

What is CD Uniformity?

CD uniformity refers to the consistency of feature sizes on a semiconductor wafer. As technology nodes shrink, maintaining uniform CD becomes increasingly challenging yet essential. Variations in CD can lead to performance discrepancies, increased power consumption, or even device failure. Therefore, achieving precise control over CD uniformity is crucial for manufacturers striving for efficiency and quality.

The Importance of CD Uniformity

Uniformity in CDs directly impacts the electrical characteristics of devices. Variations can result in differences in resistance, capacitance, and overall device performance, which can propagate through the entire system. In the context of nanometer-scale technologies, even minor discrepancies in CD can lead to significant differences in device behavior. Hence, maintaining stringent CD control is necessary for meeting the high-performance standards of modern applications.

JEDEC JESD89-3 Guidelines Overview

The JEDEC JESD89-3 guidelines provide an industry-standard approach to measuring and assessing CD uniformity. These guidelines serve as a benchmark for manufacturers to evaluate their processes and ensure compliance with industry standards. The document outlines specific methodologies for measuring CD, analyzing data, and interpreting results to facilitate more consistent production practices.

Measuring CD Uniformity

One of the key aspects of the JEDEC JESD89-3 guidelines is the emphasis on accurate measurement techniques. Advanced metrology tools, such as scanning electron microscopes (SEM) and atomic force microscopes (AFM), are commonly utilized to measure CD with high precision. The guidelines recommend comprehensive sampling across the wafer to capture variations and provide a reliable assessment of uniformity.

Data Analysis and Interpretation

After collecting measurement data, it is crucial to analyze and interpret it effectively. The JESD89-3 guidelines suggest statistical methods to evaluate CD uniformity, including calculating mean, standard deviation, and other pertinent statistical parameters. This analysis helps in identifying trends, variations, and potential issues in the manufacturing process.

Strategies for Improving CD Uniformity

Improving CD uniformity involves a combination of advanced process control techniques and robust equipment calibration. Manufacturers can implement real-time monitoring systems to detect variations early in the production process. Additionally, regular equipment maintenance and calibration contribute to minimizing process-induced variations, ensuring consistent CD across production runs.

Challenges in Maintaining CD Uniformity

Despite advancements in technology, maintaining CD uniformity poses several challenges. Variability in raw materials, equipment wear and tear, and environmental factors can all introduce inconsistencies. Manufacturers must continuously adapt their processes and incorporate feedback mechanisms to counteract these challenges and sustain uniformity.

Conclusion: The Path Forward

As semiconductor technology advances, the importance of CD uniformity cannot be overstated. The JEDEC JESD89-3 guidelines provide a valuable framework for manufacturers to achieve and maintain this critical parameter. By adhering to these guidelines and continuously refining their processes, manufacturers can enhance device reliability and performance, driving the continued innovation and growth of the semiconductor industry.

As photolithography continues to push the boundaries of nanoscale patterning, from EUV and DUV advancements to multi-patterning and maskless lithography, innovation cycles are accelerating—and the IP landscape is becoming more complex than ever.

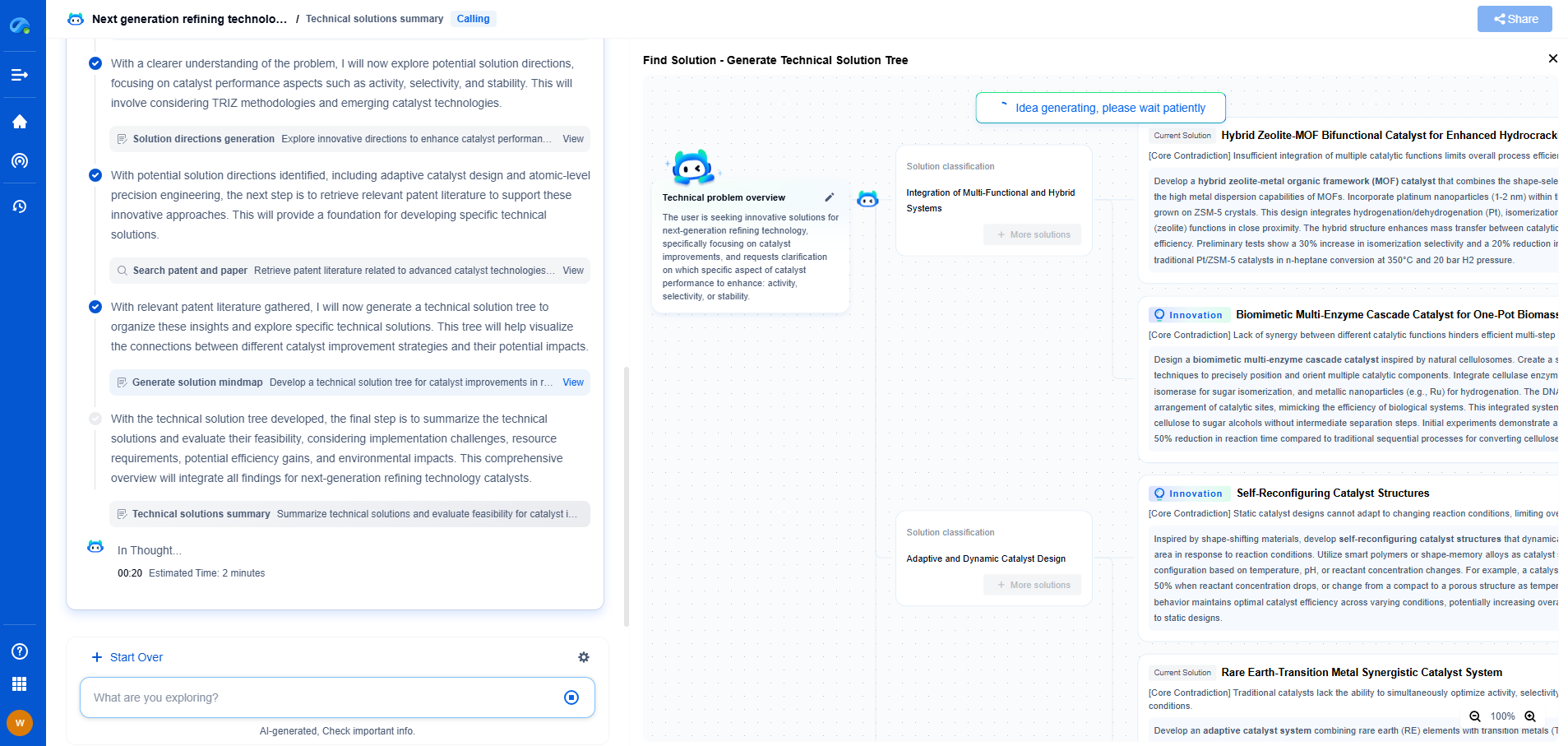

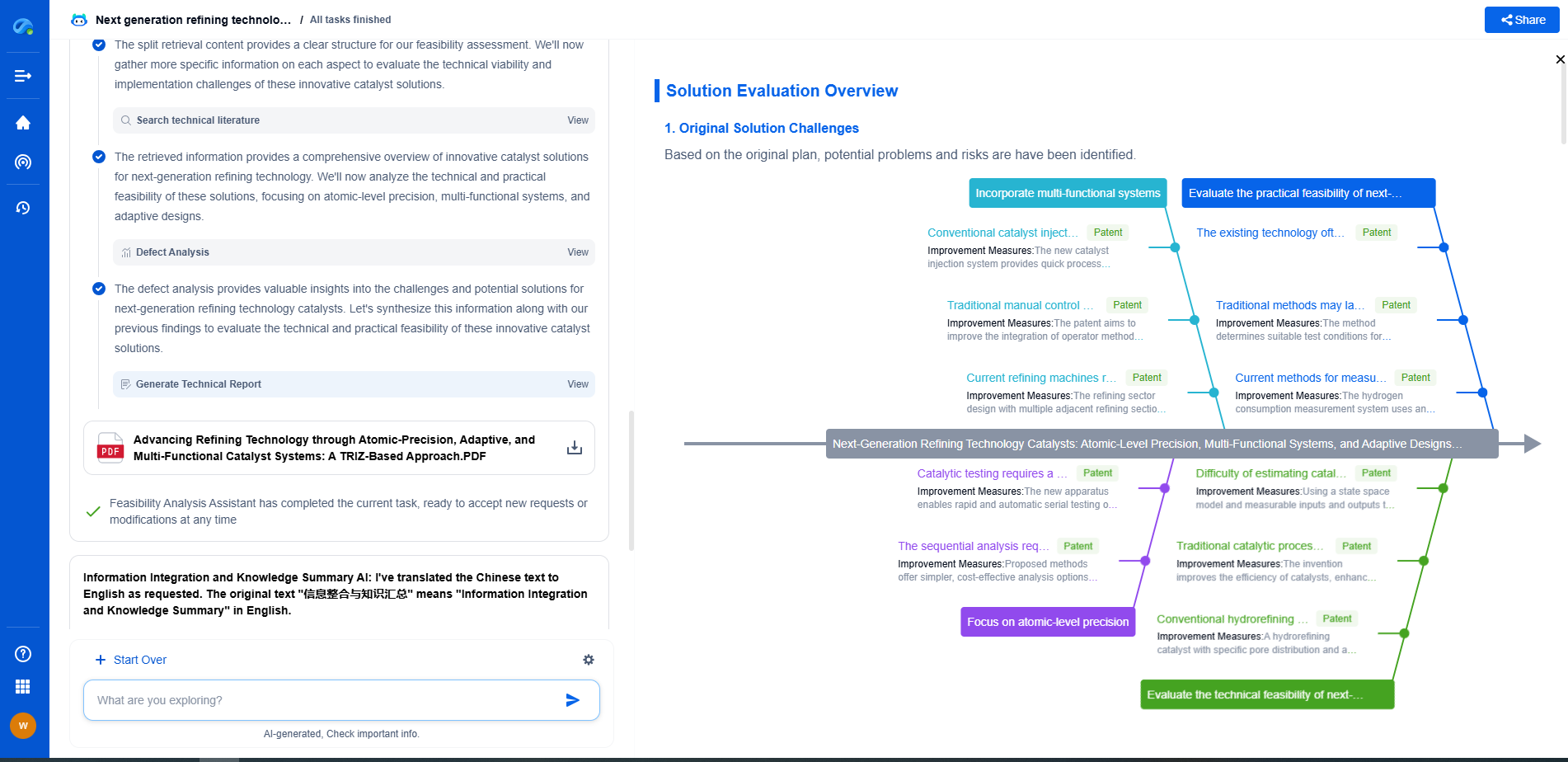

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Whether you're optimizing lithography depth of focus or exploring new materials for sub-3nm nodes, Patsnap Eureka empowers you to make smarter decisions, faster—combining AI efficiency with domain-specific insight.

💡 Start your free trial today and see how Eureka transforms how you discover, evaluate, and act on innovation in photolithography—from idea to impact.