Delamination in Stacked Capacitors: Causes and Prevention Methods

JUL 9, 2025 |

Stacked capacitors are critical components in modern electronics, contributing to the miniaturization and functionality of devices by offering high capacitance in compact spaces. However, one of the challenges inherent in their construction is the potential for delamination. This phenomenon can severely impact the performance and reliability of the capacitors. Thus, understanding the causes and implementing effective prevention methods for delamination is crucial for engineers and manufacturers.

Causes of Delamination

1. **Thermal Stress**: One of the primary causes of delamination in stacked capacitors is thermal stress. When capacitors undergo temperature fluctuations during operation or soldering processes, the differing expansion rates of the dielectric and conductive materials can lead to separation at the interfaces.

2. **Mechanical Stress**: Mechanical stress can occur during handling, assembly, or use of the electronic devices. Improper mounting techniques or shocks can induce stress that may lead to delamination. The materials used in the construction of stacked capacitors are often brittle and susceptible to cracking, which can propagate into layers separating.

3. **Moisture Ingress**: Moisture ingress is another significant cause of delamination. When moisture enters the capacitor, it can weaken the adhesive bonds between layers, leading to separation. This can be exacerbated by humidity cycles in the operating environment, which can repeatedly stress the bonds.

4. **Manufacturing Defects**: Imperfections introduced during the manufacturing process, such as uneven application of adhesive or contamination between layers, can also contribute to delamination. These defects can create weak points that are more susceptible to stress and environmental factors.

Prevention Methods

1. **Material Selection**: Choosing the right materials is crucial for minimizing the risk of delamination. Materials with similar thermal expansion coefficients should be used to reduce stress caused by temperature changes. Additionally, using moisture-resistant materials can help protect against environmental factors.

2. **Optimized Design**: An optimized design can mitigate mechanical stress by distributing forces more evenly across the capacitor. Incorporating buffers or flexible connections can help absorb shocks and reduce the impact on the layers.

3. **Improved Manufacturing Processes**: Enhancing manufacturing processes to ensure uniform application of adhesives and eliminating contaminants can significantly reduce the risk of delamination. Implementing rigorous quality control measures can help identify and rectify potential issues before they lead to failure.

4. **Environmental Controls**: Controlling the environment in which the capacitors are stored and operated can also help prevent delamination. Ensuring that devices are housed in environments with stable temperature and humidity levels can reduce thermal and moisture-induced stress on the capacitors.

5. **Testing and Monitoring**: Regular testing and monitoring of capacitors for signs of delamination can help detect issues early. Techniques such as acoustic microscopy or X-ray inspection can be used to identify delamination before it progresses to a critical failure.

Conclusion

Delamination in stacked capacitors poses significant challenges to the reliability and performance of electronic devices. By understanding the causes and implementing comprehensive prevention strategies, manufacturers can significantly enhance the durability and functionality of these components. Through careful material selection, optimized design, improved manufacturing processes, and rigorous testing, the integrity of stacked capacitors can be maintained, ensuring their continued contribution to the advancement of electronic technology.

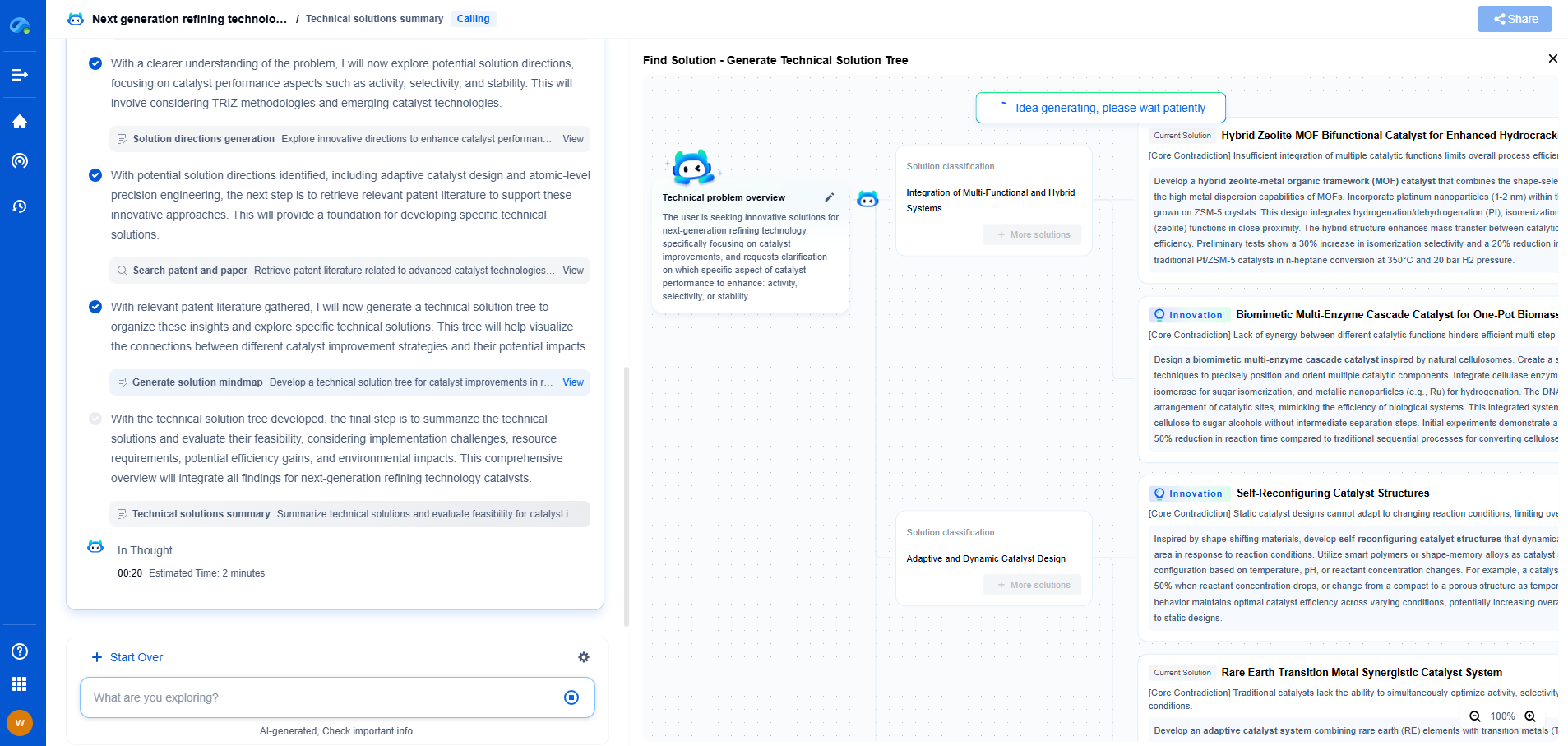

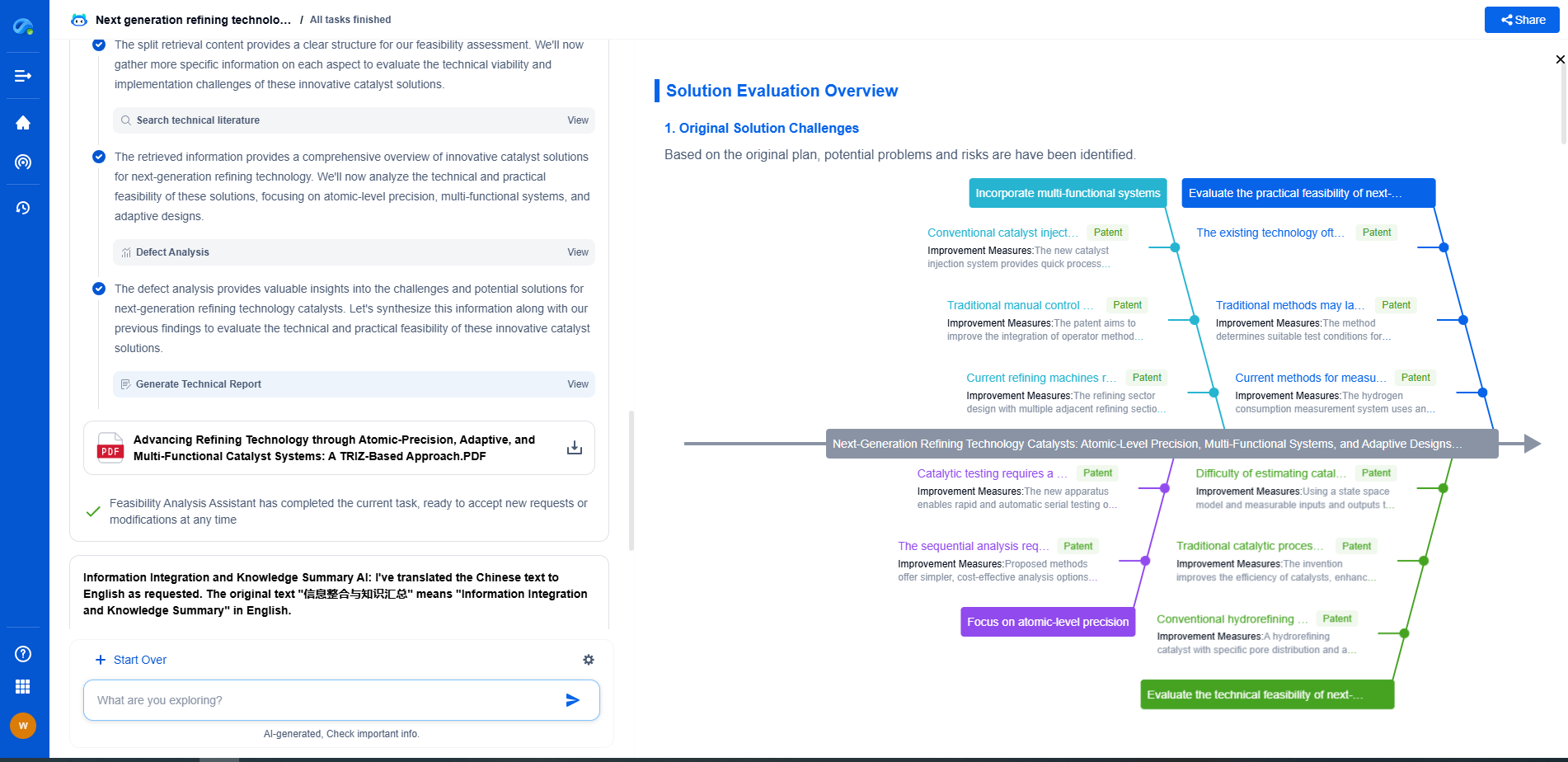

Looking to accelerate your capacitor innovation pipeline?

As capacitor technologies evolve—from miniaturized MLCCs for smartphones to grid-scale energy storage devices—so must the way your team accesses critical knowledge.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Try Patsnap Eureka now and discover a faster, smarter way to research and innovate in capacitor technology.