DRAM Manufacturing: LER Requirements for 1α Node Capacitors

JUL 28, 2025 |

Dynamic Random-Access Memory (DRAM) has been a cornerstone of semiconductor technology, serving as the primary memory component in countless electronic devices. As the demand for higher performance and lower power consumption increases, DRAM manufacturers continuously push the boundaries of technology nodes. The transition to the 1α node represents a significant leap, characterized by enhanced capabilities and increased complexity. Among the many challenges faced in this transition, the Line Edge Roughness (LER) requirements for capacitors stand out as a critical factor in ensuring the reliability and performance of DRAM.

Importance of LER in DRAM Capacitors

Line Edge Roughness refers to the deviations and fluctuations observed at the edges of lines in semiconductor patterns. These variations can have profound implications on the electrical properties and performance of the devices. In DRAM, capacitors are essential components that store data in the form of electrical charge. The integrity and efficiency of these capacitors are paramount, making LER a critical parameter to control.

As DRAM scales down to the 1α node, the dimensions of these capacitors shrink, amplifying the impact of LER. A rougher line edge can lead to inconsistencies in capacitance, increased leakage currents, and reduced dielectric strength. Consequently, achieving stringent LER control is vital for maintaining the high standards of performance and reliability expected from DRAM at this advanced node.

Challenges in Achieving Optimal LER

The pursuit of optimal LER at the 1α node involves several technical challenges. The complexity arises from the need to balance various factors that influence LER, including lithography techniques, etching processes, and material properties.

Lithography, the process of patterning semiconductor wafers, is particularly crucial. As feature sizes shrink, the limitations of conventional optical lithography become more pronounced, necessitating advanced techniques such as Extreme Ultraviolet (EUV) lithography. EUV lithography offers improved resolution capabilities, but it also introduces new challenges in maintaining LER at acceptable levels.

Etching processes, which define the final dimensions of the capacitor structures, must be meticulously controlled to minimize LER. Variations in etching can exacerbate line roughness, further complicating the task of achieving uniform and smooth capacitor edges. Innovations in etching technology and process optimization are essential to address these issues.

Material selection also plays a pivotal role. The choice of dielectric materials and conductive layers can influence LER, requiring careful consideration to ensure compatibility with other process steps and the overall DRAM architecture.

Strategies for LER Control

To address the challenges associated with LER in the 1α node, manufacturers are employing several strategies. Advanced metrology tools are used to accurately measure and characterize LER, providing critical data necessary for process optimization. These measurements guide adjustments in lithography and etching parameters to achieve the desired line edge smoothness.

Process integration is another key strategy. By coordinating various fabrication steps, manufacturers can reduce cumulative LER effects. This holistic approach ensures that each stage of the manufacturing process contributes positively to the final outcome.

Research and development efforts continue to explore novel materials and techniques that can offer better LER control. From new photoresists that improve pattern fidelity to etching gases that minimize line edge deviations, innovation is at the heart of overcoming LER challenges.

Conclusion: The Path Forward for 1α Node DRAM

The transition to the 1α node in DRAM manufacturing represents a pivotal moment in semiconductor technology, promising greater efficiency and performance. However, the stringent LER requirements for capacitors underscore the complexity and precision needed to realize these advancements. By leveraging cutting-edge lithography, refining etching processes, and exploring new materials, the industry is poised to meet these challenges head-on.

As DRAM technology continues to evolve, the lessons learned in managing LER at the 1α node will undoubtedly inform future innovations, setting the stage for even more advanced memory solutions. The journey is fraught with challenges, but the pursuit of excellence continues to drive the semiconductor industry forward.

As photolithography continues to push the boundaries of nanoscale patterning, from EUV and DUV advancements to multi-patterning and maskless lithography, innovation cycles are accelerating—and the IP landscape is becoming more complex than ever.

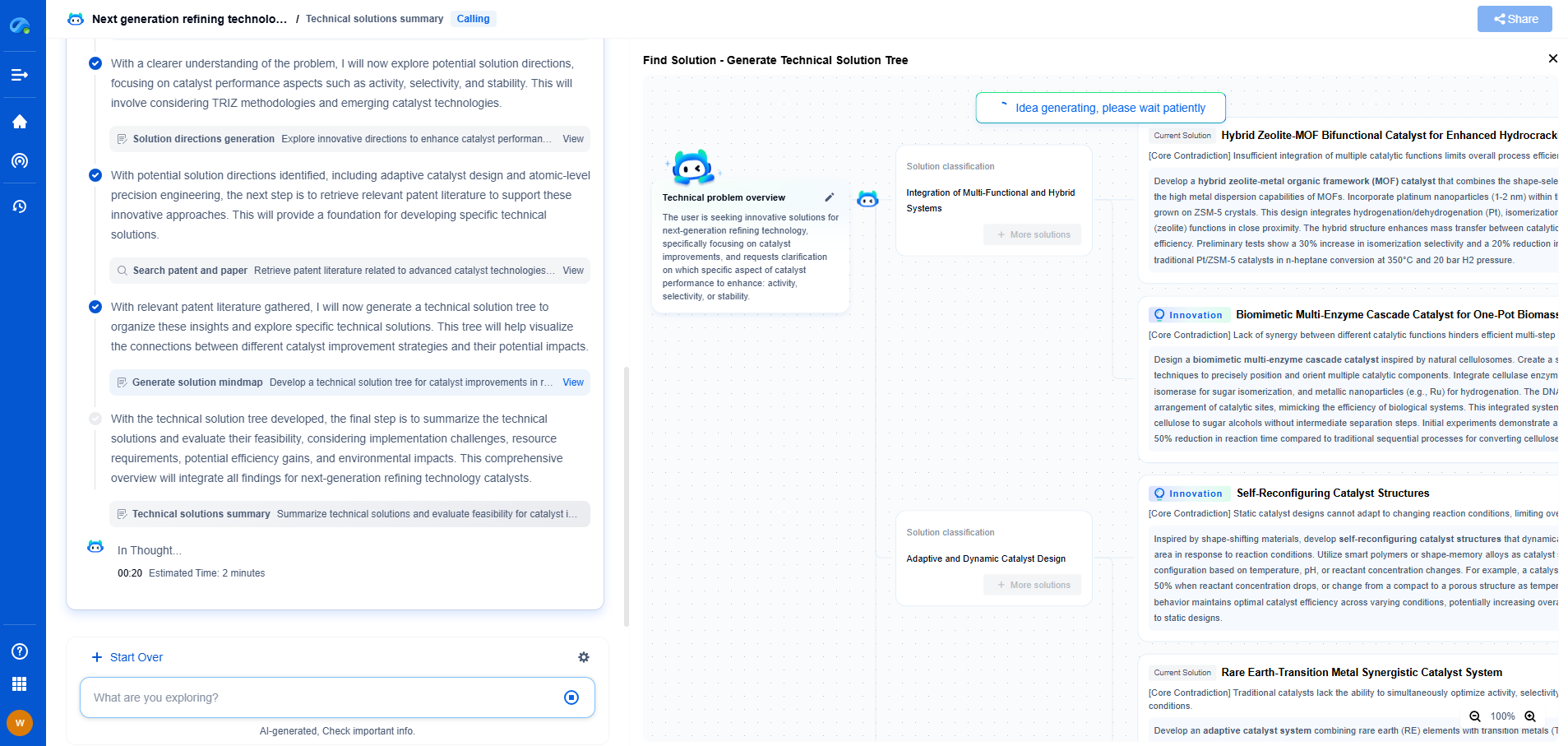

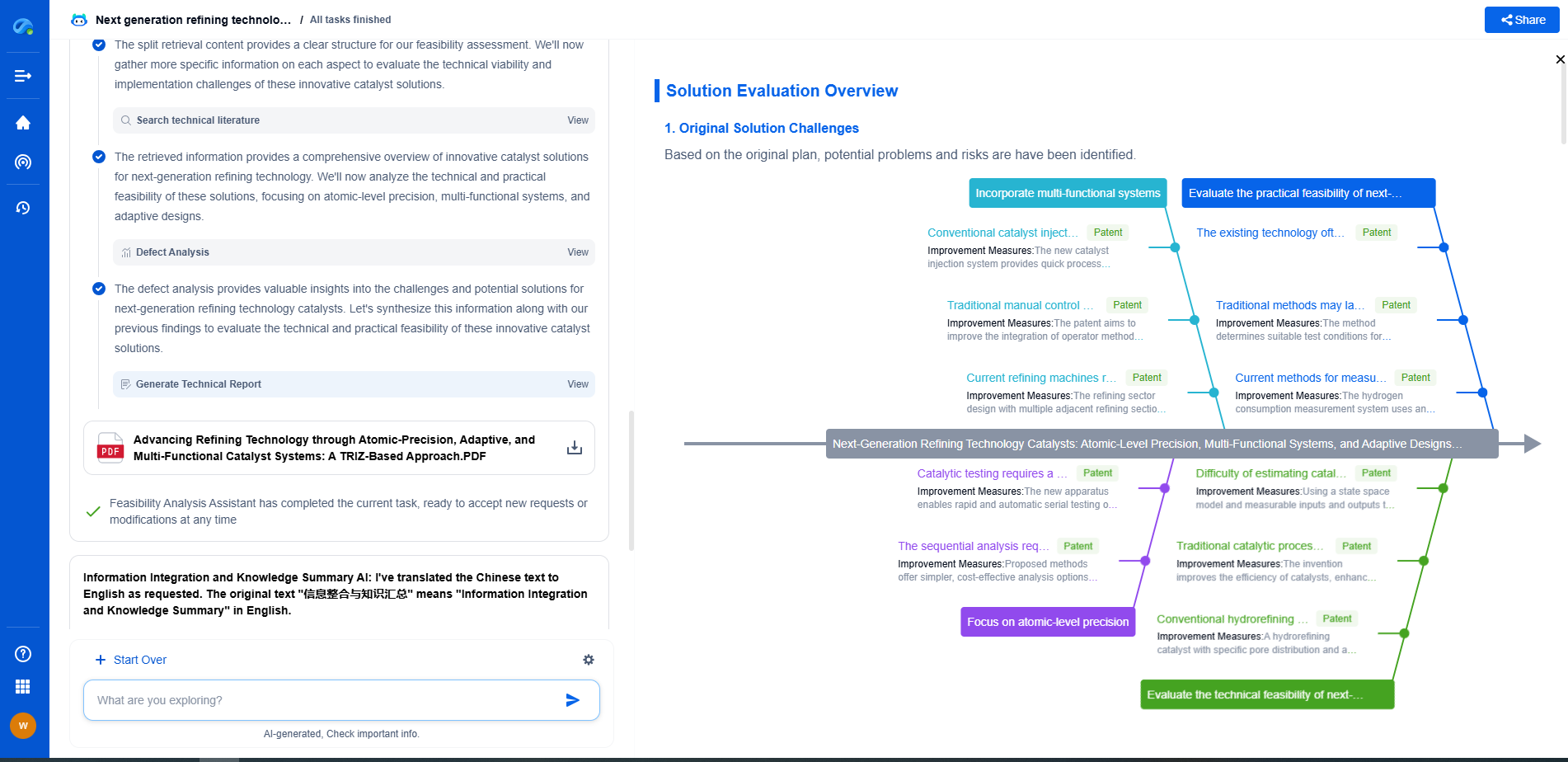

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Whether you're optimizing lithography depth of focus or exploring new materials for sub-3nm nodes, Patsnap Eureka empowers you to make smarter decisions, faster—combining AI efficiency with domain-specific insight.

💡 Start your free trial today and see how Eureka transforms how you discover, evaluate, and act on innovation in photolithography—from idea to impact.