EUV stochastic noise and defectivity: Challenges for HVM nodes

JUL 28, 2025 |

Understanding EUV Stochastic Noise

Stochastic noise is a phenomenon that arises from the inherent randomness in the photon absorption process during EUV lithography. As the industry has transitioned into using EUV wavelengths (approximately 13.5nm), the process has become more susceptible to stochastic variations. These variations can lead to line-edge roughness (LER) and line-width roughness (LWR), which are critical concerns in pattern fidelity during semiconductor manufacturing.

The primary driver of stochastic noise at EUV wavelengths is the limited number of photons used in the exposure process. Fewer photons result in a higher degree of randomness, making it more challenging to achieve precision at smaller technology nodes. This noise can result in critical dimension (CD) variability, impacting the performance and yield of the final semiconductor products.

Defectivity Challenges in HVM

Defectivity refers to the presence of defects that occur during the manufacturing process, which can degrade the performance or even prevent the functionality of semiconductor devices. EUV lithography is particularly susceptible to defectivity due to several factors inherent in the technology.

One of the key challenges in managing defectivity is the generation of defects on the mask, which can be propagated to the wafer during exposure. Mask defects are challenging to detect and mitigate, given the high resolution required at EUV wavelengths. Furthermore, defects can also arise from the resist materials used in EUV lithography, which may exhibit sensitivity to stochastic variations and environmental conditions.

Implications for HVM Nodes

The combined effects of stochastic noise and defectivity have profound implications for high-volume manufacturing nodes. As devices continue to shrink, the tolerance for variability diminishes, requiring tighter control over the lithography process. This necessitates significant advancements in EUV technology to ensure that it can meet the demands of mass production at advanced nodes.

Yield losses due to stochastic noise and defectivity directly translate into increased production costs. Additionally, if these challenges are not adequately addressed, they could lead to delays in time-to-market for new semiconductor technologies, impacting the competitiveness of companies at the forefront of innovation.

Strategies for Mitigating Challenges

Several strategies are currently being explored to mitigate the impact of EUV stochastic noise and defectivity. Enhancements in EUV source power and the development of more sensitive resist materials are crucial steps toward reducing stochastic effects. Increasing the number of photons reaching the wafer can help achieve more consistent exposure, while advanced resist materials can improve pattern fidelity.

Furthermore, innovations in mask technology are essential. The development of defect-free masks and improvements in mask inspection and repair techniques are critical to reducing defectivity. Advanced computational lithography techniques, such as optical proximity correction (OPC) and machine learning algorithms, can also play a significant role in anticipating and compensating for potential variations.

Conclusion

EUV stochastic noise and defectivity present formidable challenges to the efficient scaling of semiconductor devices at high-volume manufacturing nodes. However, through a concerted effort involving technological innovations and strategic planning, these challenges can be effectively managed. The continuous evolution of EUV lithography will not only help overcome current hurdles but will also pave the way for the development of even more advanced semiconductor technologies in the future.

As photolithography continues to push the boundaries of nanoscale patterning, from EUV and DUV advancements to multi-patterning and maskless lithography, innovation cycles are accelerating—and the IP landscape is becoming more complex than ever.

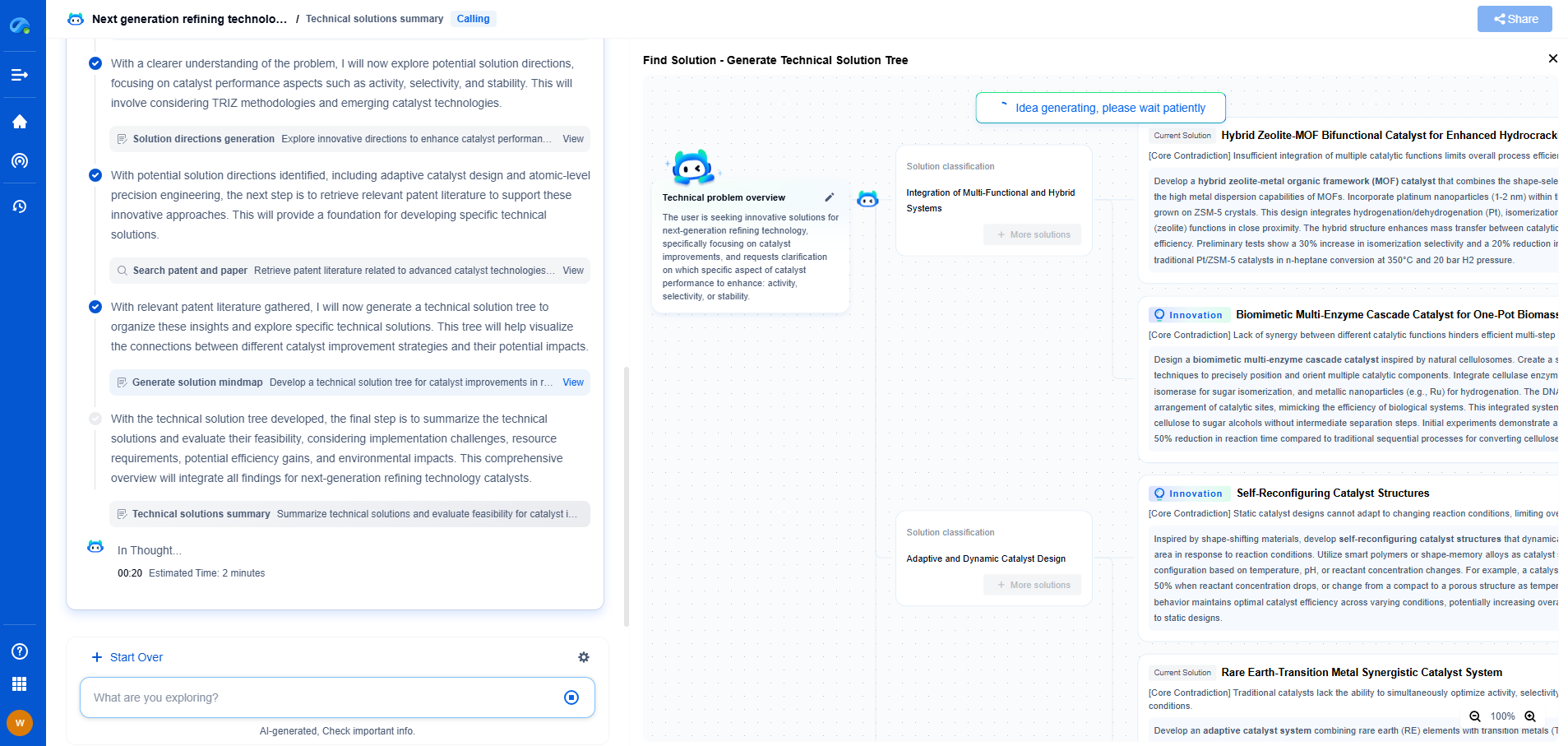

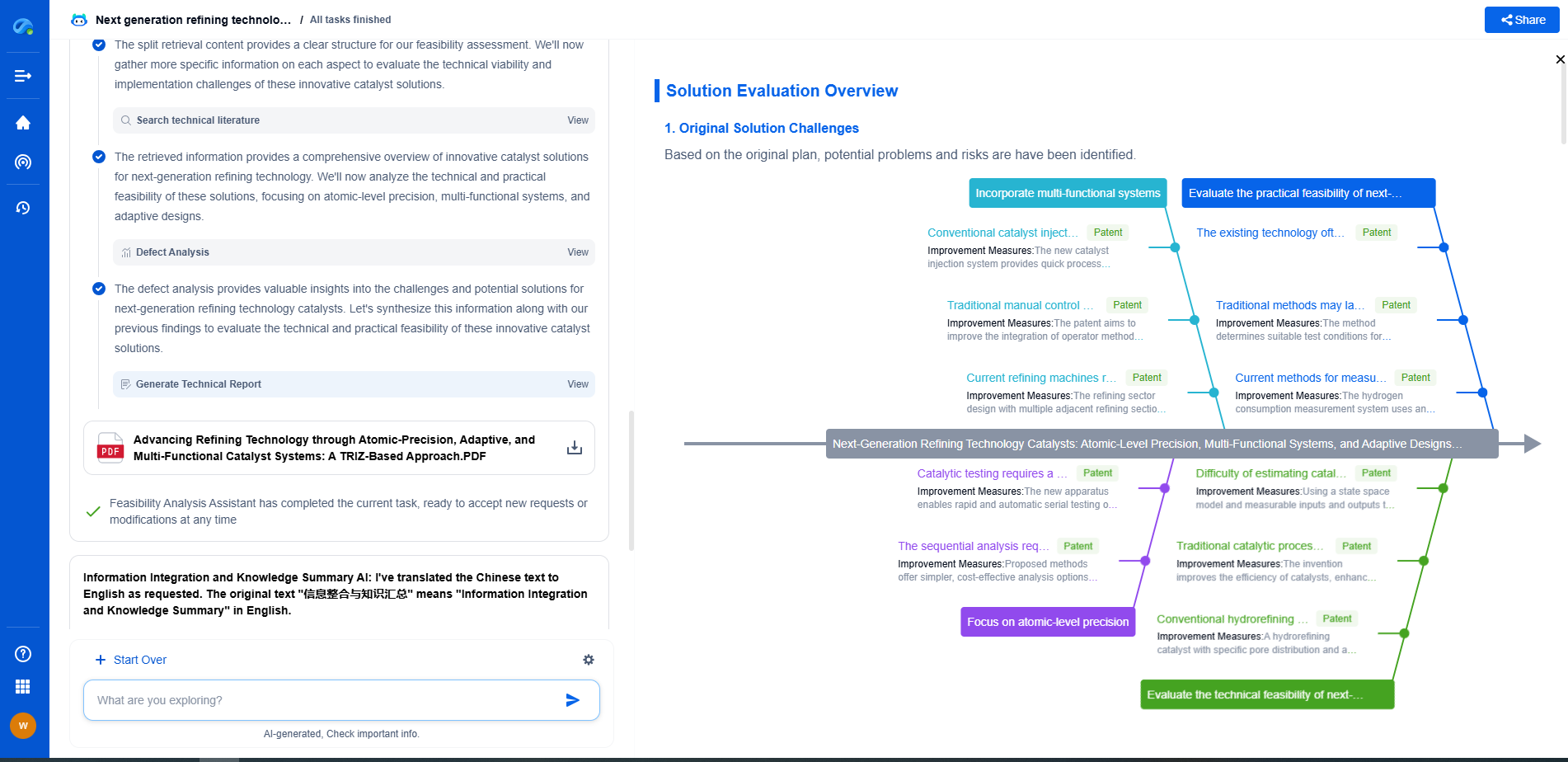

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Whether you're optimizing lithography depth of focus or exploring new materials for sub-3nm nodes, Patsnap Eureka empowers you to make smarter decisions, faster—combining AI efficiency with domain-specific insight.

💡 Start your free trial today and see how Eureka transforms how you discover, evaluate, and act on innovation in photolithography—from idea to impact.