High-NA EUV: 0.55 Numerical Aperture System Challenges

JUL 28, 2025 |

As the semiconductor industry continues to push the boundaries of miniaturization, achieving finer features on chips is paramount. This quest has led to the development of extreme ultraviolet (EUV) lithography, which operates at a wavelength of 13.5 nm. More recently, the introduction of high numerical aperture (high-NA) EUV systems with a numerical aperture of 0.55 has promised further leaps in resolution. However, this advancement also brings a unique set of challenges that need to be addressed for effective implementation.

Optical System Complexity

One of the primary challenges of high-NA EUV systems is the increased complexity of the optical system. With a higher numerical aperture, the system's optics must be designed to handle a steeper angle of light incidence. This requirement complicates the design of the projection optics, necessitating more mirrors and sophisticated coatings to minimize aberrations and maintain image fidelity. The increased number of optical elements also leads to larger overall system sizes, demanding significant engineering efforts to ensure precision alignment and stability.

Mask Technology and Defectivity

High-NA EUV lithography imposes stringent demands on mask technology. The smaller features and tighter tolerances increase the susceptibility to mask defects, which in turn can lead to yield issues in chip production. The development of defect-free masks requires advanced inspection and repair techniques, as well as the use of novel materials that can withstand the high energy of EUV photons without degrading. Additionally, the shift to a higher NA impacts mask design rules, necessitating new approaches in patterning and mask-making processes.

Resist Materials and Sensitivity

The transition to high-NA EUV systems also challenges the development of photoresist materials. Due to the higher resolution and reduced depth of focus, resists must exhibit both high sensitivity to EUV light and excellent resolution capabilities. Achieving this balance is non-trivial, as increasing resist sensitivity often leads to trade-offs in line-edge roughness and pattern fidelity. Researchers are exploring new resist chemistries and processing techniques to overcome these hurdles, but an optimal solution remains elusive.

Overlay and Alignment Challenges

Maintaining precise overlay and alignment accuracy is critical in high-NA EUV lithography. The reduced depth of focus necessitates extremely tight control over wafer positioning and focus during exposure. This requirement complicates the alignment process, as even minute deviations can lead to significant errors in the final device patterning. Advanced metrology techniques, combined with real-time feedback and control systems, are essential to meet the stringent overlay specifications demanded by next-generation semiconductor devices.

Thermal Management and Energy Efficiency

The increased power requirements of high-NA EUV lithography systems pose significant challenges in thermal management and energy efficiency. The high energy of EUV photons generates substantial heat within the optical components, necessitating advanced cooling strategies to maintain system integrity and performance. Furthermore, achieving efficient conversion of energy into EUV light remains a critical area of research, as current light sources still suffer from relatively low efficiency rates. Innovations in source technology and heat dissipation mechanisms are essential to ensure the practicality of high-NA EUV systems.

Conclusion

While high-NA EUV lithography presents numerous challenges, addressing these issues is vital for the continued progress of semiconductor technology. As the industry works to overcome obstacles in optical design, mask technology, resist development, and system integration, collaborations between researchers, equipment manufacturers, and chipmakers will be crucial. The successful implementation of high-NA EUV systems promises to propel the industry forward, enabling the next generation of high-performance, low-power semiconductor devices.

As photolithography continues to push the boundaries of nanoscale patterning, from EUV and DUV advancements to multi-patterning and maskless lithography, innovation cycles are accelerating—and the IP landscape is becoming more complex than ever.

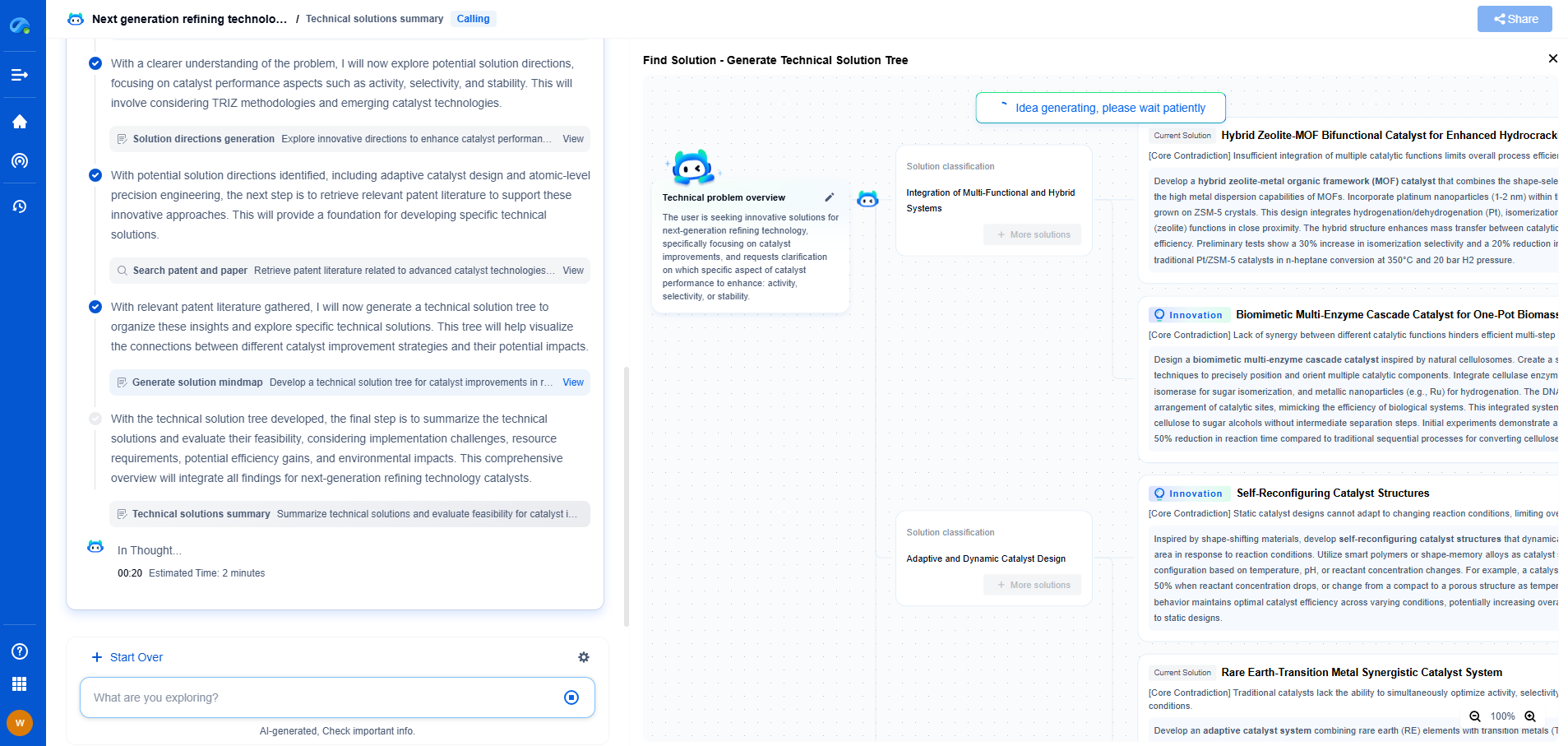

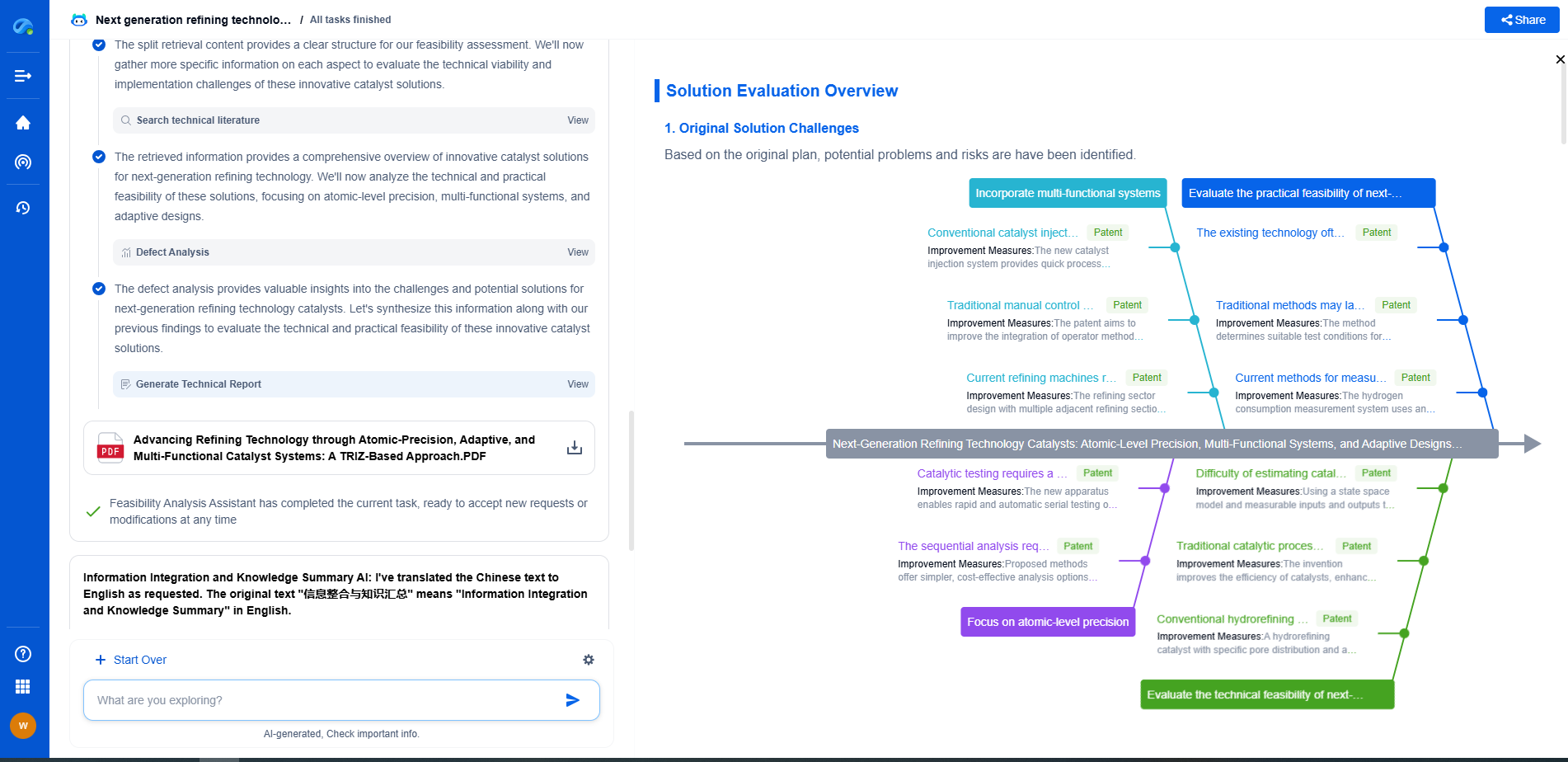

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Whether you're optimizing lithography depth of focus or exploring new materials for sub-3nm nodes, Patsnap Eureka empowers you to make smarter decisions, faster—combining AI efficiency with domain-specific insight.

💡 Start your free trial today and see how Eureka transforms how you discover, evaluate, and act on innovation in photolithography—from idea to impact.