How LER impacts device variability and transistor performance

JUL 28, 2025 |

Line-edge roughness (LER) refers to the deviation of the edges of a line from an ideal, smooth edge. In the context of semiconductor devices, LER is an important factor affecting the performance and variability of transistors. As the semiconductor industry continues to push towards smaller nodes, the impact of LER on device performance becomes more significant. This is because, at smaller scales, even minor imperfections can lead to substantial changes in electrical characteristics.

The Origins of LER

LER arises during the lithography process, a critical step in semiconductor fabrication where patterns are transferred onto a silicon wafer. Various factors contribute to LER, including the inherent roughness in photoresist materials, limitations of the exposure tools, and the etching process. As lithographic techniques are pushed to their limits to achieve smaller features, controlling LER becomes an increasingly challenging task.

How LER Affects Device Variability

Device variability refers to the differences in performance characteristics among transistors that are intended to be identical. LER contributes to this variability because it can cause fluctuations in the critical dimensions of transistor gates. The gate length is particularly sensitive to LER, and variations can lead to differences in threshold voltage, drive current, and leakage current. As a result, a high LER can make it difficult to achieve tight control over the electrical properties of transistors, which is crucial for ensuring consistent performance across a chip.

Impact on Transistor Performance

The performance of transistors in integrated circuits is fundamentally linked to their physical dimensions and material properties. LER can impact these dimensions in several ways. For example, gate length variations due to LER can alter the transistor's switching speed and power consumption. Shorter gate lengths, resulting from LER, can increase the drive current but also elevate leakage currents, leading to higher power dissipation.

Moreover, LER can exacerbate short-channel effects, where the channel length of the transistor becomes comparable to the depletion width of the source/drain junctions. This can lead to increased off-state leakage and reduced threshold voltage, both of which degrade device performance and power efficiency.

Strategies to Mitigate LER

To mitigate the impact of LER, the semiconductor industry employs several strategies. Advanced lithography techniques, such as extreme ultraviolet (EUV) lithography, offer higher resolution and can reduce LER. Additionally, the use of novel photoresist materials and improved etching processes can help minimize roughness. In some cases, post-lithography treatments, like thermal annealing, are used to smooth out the line edges.

Another approach is the design of circuits that are more tolerant to variability. By incorporating redundancy and error correction or by designing logic blocks that can function correctly despite some level of variability, manufacturers can alleviate some of the adverse effects of LER.

Future Outlook

As technology nodes continue to shrink, the challenge of managing LER will persist. The industry will need to innovate continuously to develop new materials, processes, and design methodologies that can cope with the limitations imposed by LER. Collaboration between material scientists, process engineers, and circuit designers will be essential in addressing these challenges.

In conclusion, while LER presents significant challenges in the fabrication of modern semiconductor devices, ongoing advancements in technology and design strategies offer promising paths to manage its impact. By understanding the origins, effects, and mitigation strategies for LER, the semiconductor industry can continue to push the boundaries of device performance and integration.

As photolithography continues to push the boundaries of nanoscale patterning, from EUV and DUV advancements to multi-patterning and maskless lithography, innovation cycles are accelerating—and the IP landscape is becoming more complex than ever.

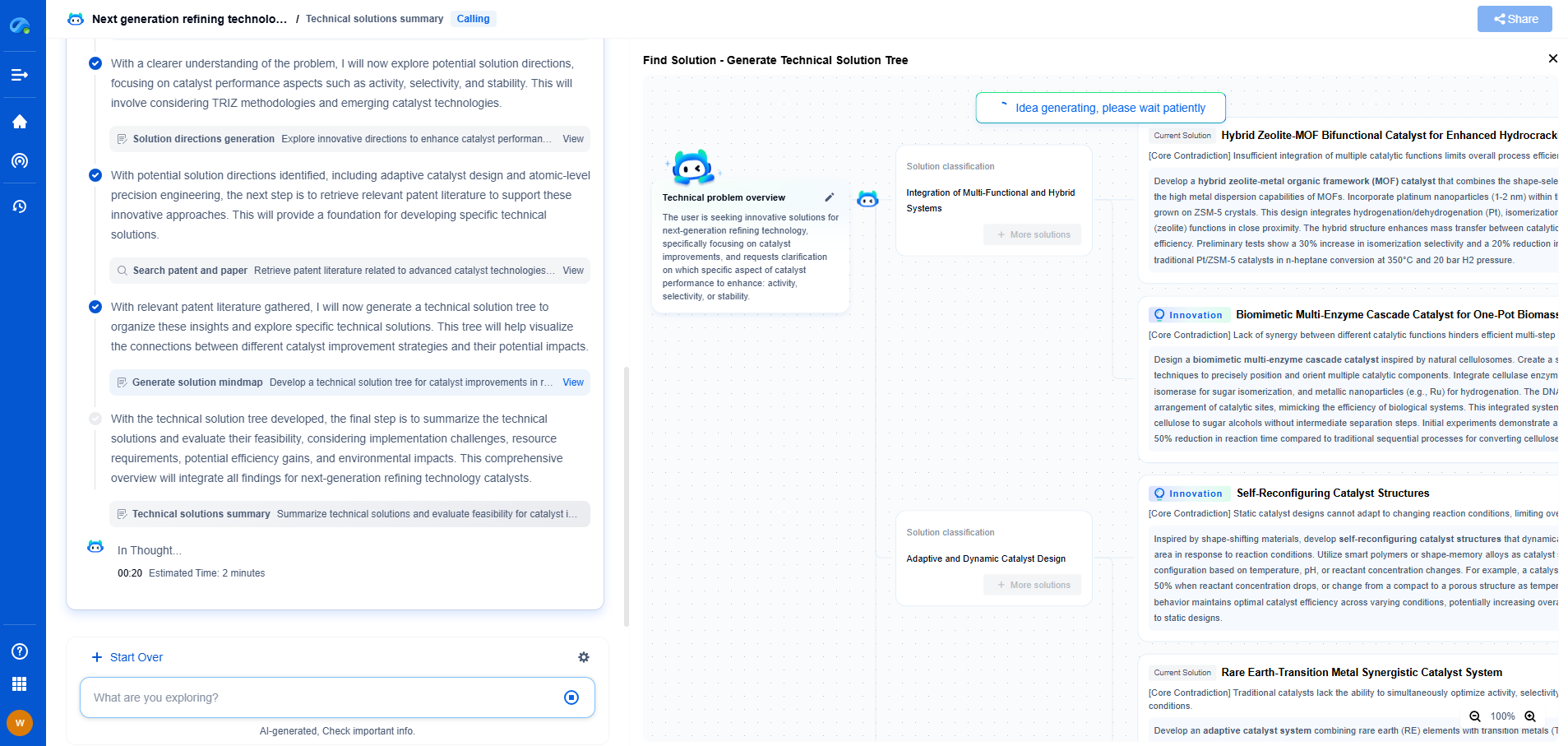

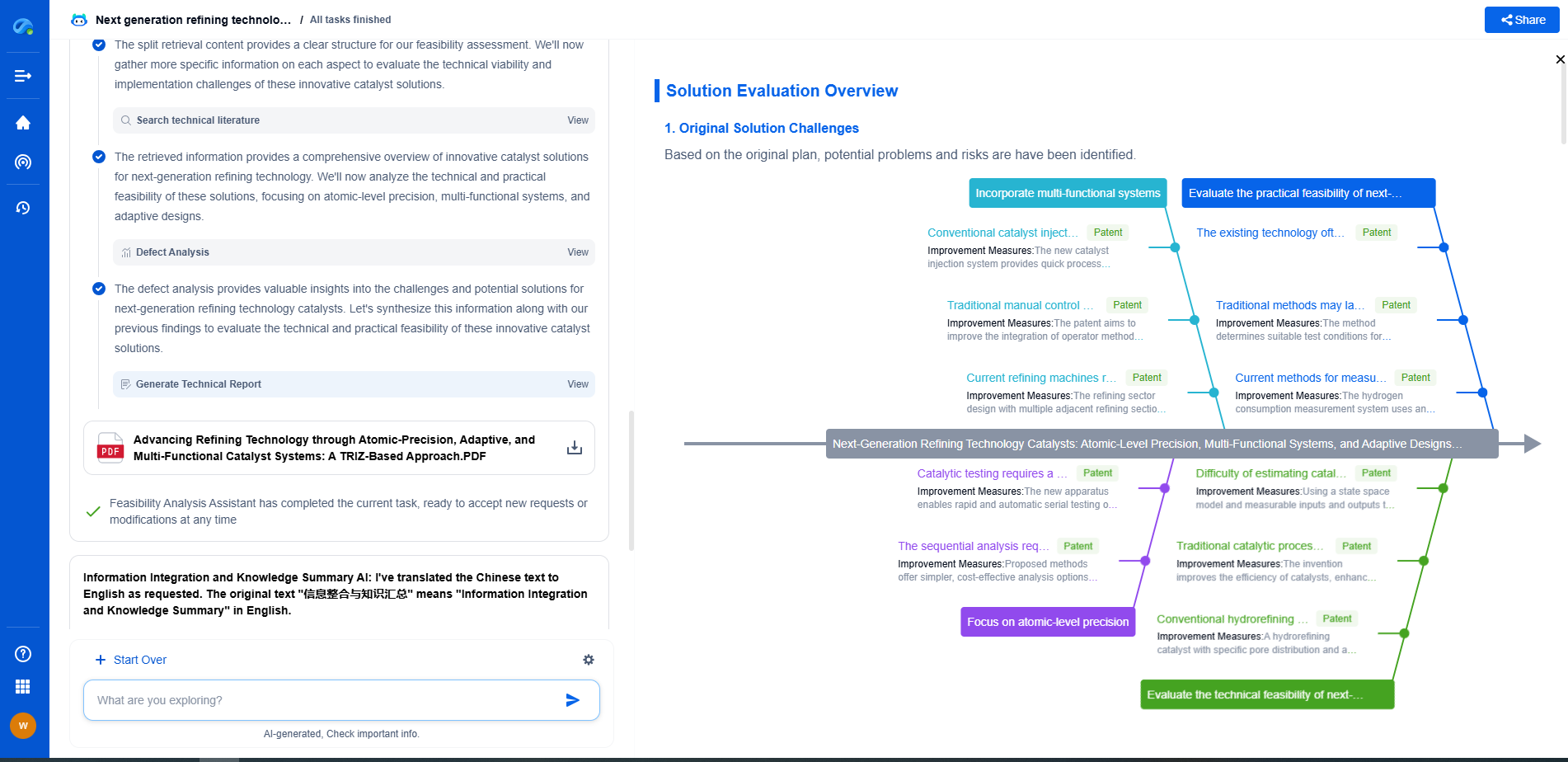

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Whether you're optimizing lithography depth of focus or exploring new materials for sub-3nm nodes, Patsnap Eureka empowers you to make smarter decisions, faster—combining AI efficiency with domain-specific insight.

💡 Start your free trial today and see how Eureka transforms how you discover, evaluate, and act on innovation in photolithography—from idea to impact.