How to minimize line edge roughness during post-lithography cleaning

JUL 28, 2025 |

Understanding Line Edge Roughness

Before we explore the solutions, it's essential to understand what line edge roughness is. LER refers to the deviation from the ideal edge of a line pattern on a wafer. These deviations can be caused by factors such as variations in the photoresist material, exposure to radiation, and the subsequent development process. LER can lead to variations in critical dimensions, affecting the electrical properties of the semiconductor devices.

Importance of Reducing LER

Reducing LER is vital for ensuring device reliability and performance. Rough edges can result in uneven electric fields, increased leakage currents, and reduced effective channel width in transistors, ultimately leading to performance degradation. In advanced lithography nodes, where dimensions are shrinking, the impact of LER becomes even more pronounced, necessitating effective control measures.

Optimizing Lithography Parameters

One of the primary methods to minimize LER is by optimizing lithography parameters. This includes careful selection of photoresist materials that offer high resolution and sensitivity. Additionally, adjusting exposure doses and focus settings can help achieve better control over pattern edges. Utilizing advanced exposure techniques such as immersion lithography and extreme ultraviolet (EUV) lithography can also contribute to reducing LER.

Post-Exposure Baking and Development

The post-exposure bake (PEB) step plays a critical role in defining the final resist profile. Optimizing PEB temperature and time can aid in reducing LER by promoting a more uniform polymerization of the photoresist. Similarly, selecting the appropriate developer solution and optimizing development time can help achieve smoother line edges. It's crucial to maintain precise control over these parameters to minimize roughness.

Implementing Advanced Cleaning Techniques

After lithography, advanced cleaning techniques can be employed to further minimize LER. Plasma cleaning, for instance, uses ionized gases to remove residues without physically touching the wafer surface, reducing the risk of introducing additional roughness. Similarly, employing supercritical CO2 cleaning can effectively remove submicron particles and residues, leaving cleaner and smoother line edges.

Exploring Novel Materials and Processes

Incorporating novel materials and processes can also contribute to minimizing LER. For example, using self-assembled monolayers (SAMs) can help in achieving smoother surfaces by providing a uniform coating that minimizes edge deviations. Additionally, exploring new resist chemistries and bottom anti-reflective coatings (BARCs) can enhance pattern fidelity and reduce roughness.

Leveraging Simulation and Modeling

Simulation and modeling tools can be invaluable in predicting and mitigating LER. By simulating the lithography process, manufacturers can identify potential sources of roughness and optimize parameters accordingly. These tools can also help in evaluating the effectiveness of different cleaning techniques and materials, reducing the need for extensive experimental trials.

Continuous Monitoring and Feedback

Implementing a robust monitoring and feedback system is crucial for maintaining control over LER. Real-time monitoring using advanced metrology tools can help in detecting variations and deviations, allowing for immediate corrective actions. Incorporating feedback loops into the manufacturing process ensures that any issues are addressed promptly, minimizing the impact on device performance.

Conclusion

Minimizing line edge roughness during post-lithography cleaning is a multifaceted challenge that requires a comprehensive approach. By optimizing lithography parameters, employing advanced cleaning techniques, exploring novel materials, and leveraging simulation and modeling, manufacturers can effectively reduce LER. As semiconductor technology continues to evolve, staying ahead of these challenges will be essential for ensuring the production of high-quality, reliable devices.

As photolithography continues to push the boundaries of nanoscale patterning, from EUV and DUV advancements to multi-patterning and maskless lithography, innovation cycles are accelerating—and the IP landscape is becoming more complex than ever.

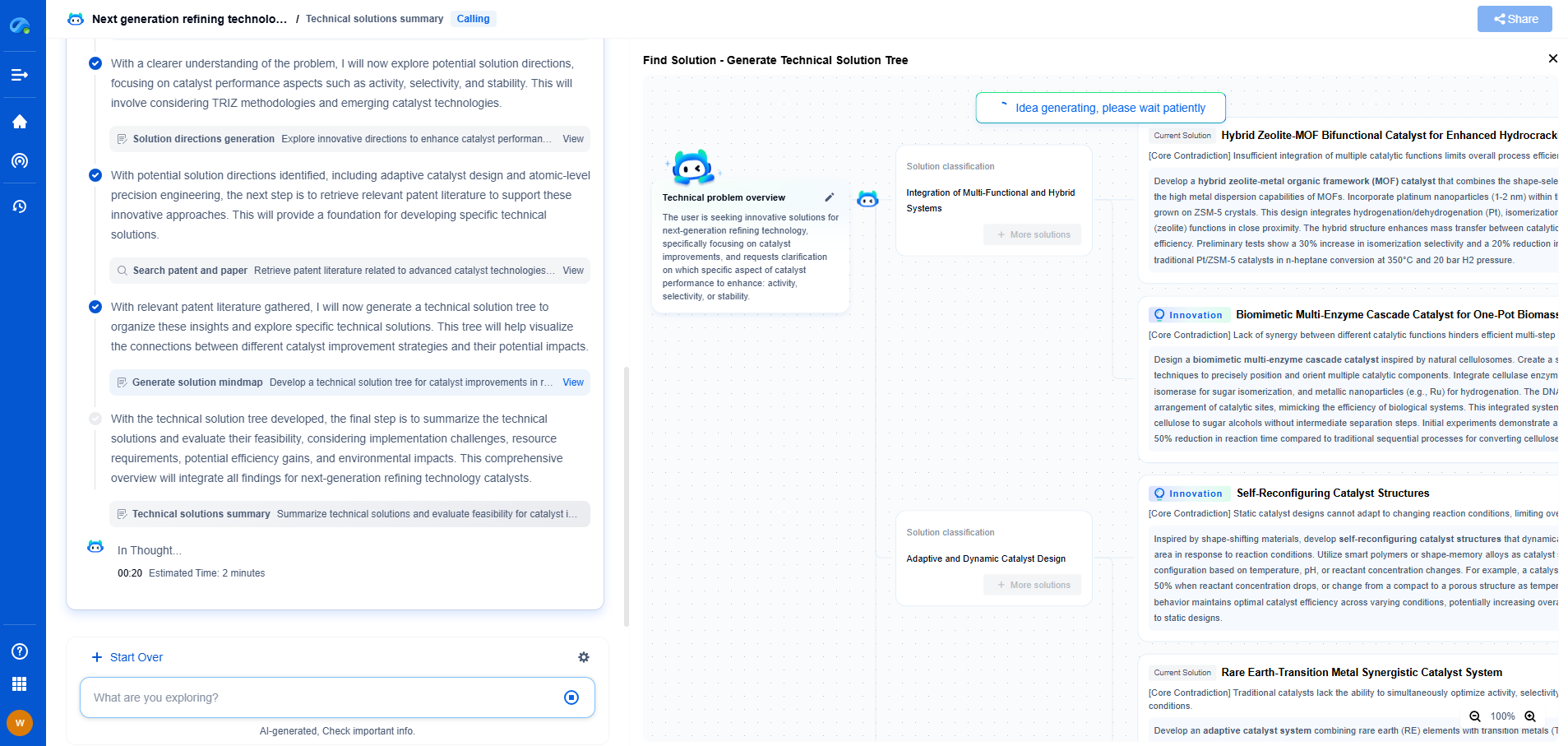

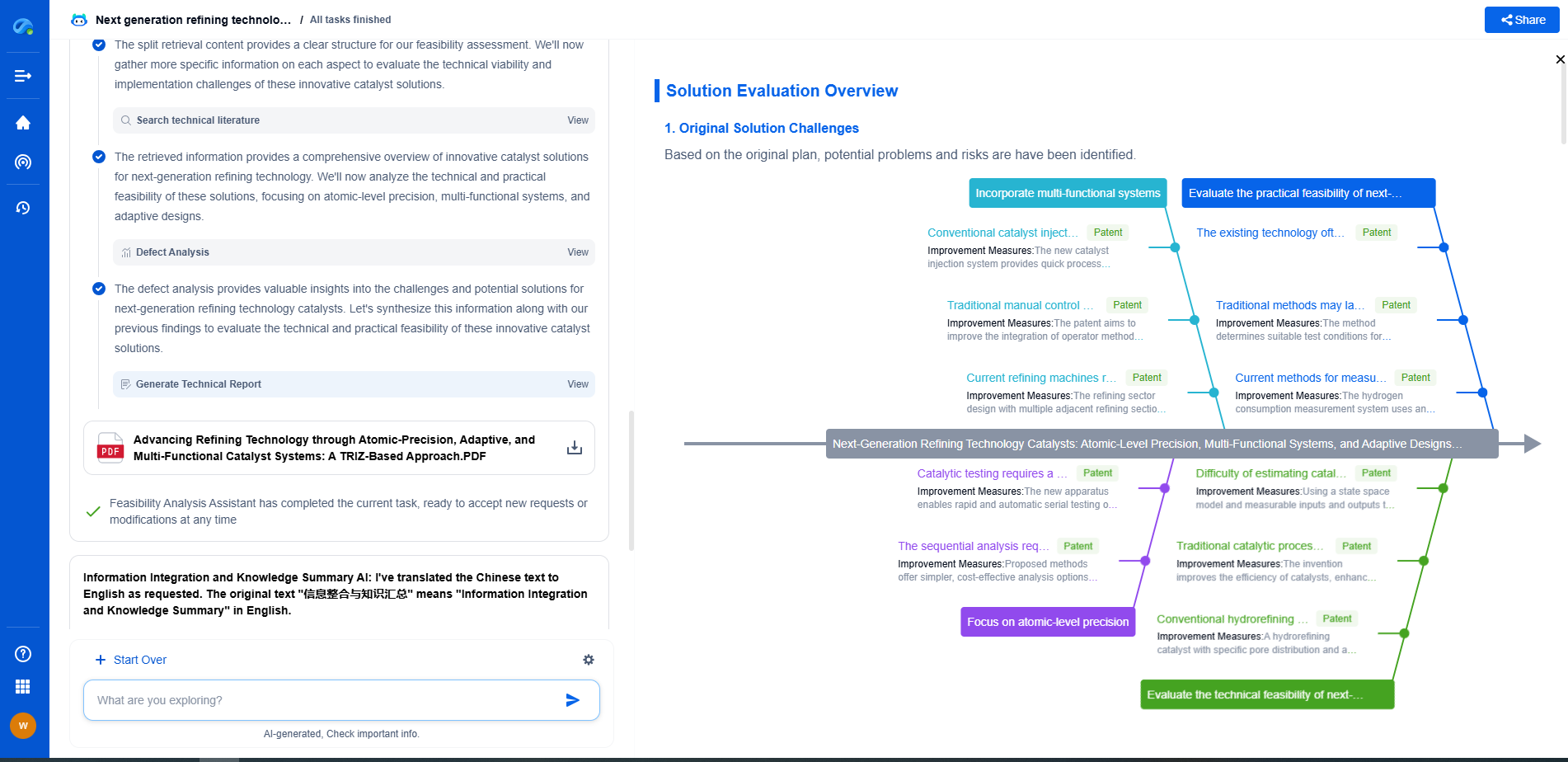

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Whether you're optimizing lithography depth of focus or exploring new materials for sub-3nm nodes, Patsnap Eureka empowers you to make smarter decisions, faster—combining AI efficiency with domain-specific insight.

💡 Start your free trial today and see how Eureka transforms how you discover, evaluate, and act on innovation in photolithography—from idea to impact.