I²C Bus Lockup: Causes and Recovery Methods

JUL 17, 2025 |

The Inter-Integrated Circuit (I²C) bus is a popular communication protocol used in embedded systems for connecting low-speed peripherals to processors and microcontrollers. Despite its advantages, engineers and developers often encounter I²C bus lockups, which can halt communication and disrupt system functionality. Understanding the causes and recovery methods for I²C bus lockup is crucial for maintaining robust system performance.

Causes of I²C Bus Lockup

1. **Noise and Interference**

One of the most common causes of I²C bus lockup is noise and electromagnetic interference. As the I²C bus typically operates with open-drain connections, it can be highly susceptible to external noise, which may falsely trigger state changes. This can result in extended clock stretching or even erroneous data being read or written, eventually leading to bus lockup.

2. **Bus Contention**

In a multi-master I²C environment, bus contention can occur when more than one master attempts to control the bus simultaneously. This can lead to signal conflicts, incomplete data transmission, and ultimately, bus lockup. Synchronization issues, incorrect priority settings, or a misunderstanding of bus arbitration rules can contribute to contention problems.

3. **Software Bugs**

Software bugs in the I²C driver or application can also lead to bus lockup. These issues may arise from improper handling of start and stop conditions, incorrect acknowledgment bit management, or failure to handle error conditions properly. Inadequate testing and lack of robust error handling routines can exacerbate these software-related issues.

4. **Faulty Devices**

At times, the cause of I²C bus lockup can be traced back to faulty devices on the bus. A slave device may hang or fail to release the bus after a transaction, preventing any other communication from occurring. This kind of problem may stem from hardware malfunctions or design flaws within the slave device.

Recovery Methods for I²C Bus Lockup

1. **Bus Reset Mechanisms**

Implementing a bus reset mechanism is an effective way to recover from I²C bus lockup. This often involves toggling the bus lines to clear any stuck signals or erroneous states. Generating a series of clock pulses while holding the data line can help ensure that any device trapped in a specific state is released. After resetting, the bus is typically re-initialized to restore normal operation.

2. **Watchdog Timers**

Using a watchdog timer is a proactive approach to detect and recover from bus lockups. By setting a timer to monitor the duration of bus inactivity or extended clock stretching, systems can automatically trigger a bus reset or system reset if a lockup is detected. This ensures that the lockup is resolved without manual intervention, enhancing system reliability.

3. **Error Recovery Protocols**

Incorporating error recovery protocols into the I²C communication routine is vital for dealing with unexpected conditions. Implementing retries for failed transactions, utilizing timeout mechanisms, and maintaining robust error handling routines can prevent lockups from escalating into critical failures. Properly designed error recovery protocols allow the system to gracefully handle unforeseen issues and maintain communication continuity.

4. **Hardware Design Improvements**

To minimize susceptibility to noise and interference, developers should focus on hardware design improvements. This includes proper shielding of the I²C lines, optimizing pull-up resistors, ensuring adequate signal termination, and maintaining a clean power supply to the bus components. These efforts contribute to a more stable I²C bus environment and reduce the likelihood of lockups.

Conclusion

I²C bus lockup is a significant concern that can impact the performance and reliability of embedded systems. By understanding the common causes such as noise, bus contention, software bugs, and faulty devices, engineers can implement effective recovery methods. Bus reset mechanisms, watchdog timers, error recovery protocols, and hardware design improvements are essential strategies to prevent and resolve I²C bus lockups. With these measures, developers can enhance system robustness and ensure seamless communication across I²C-enabled devices.

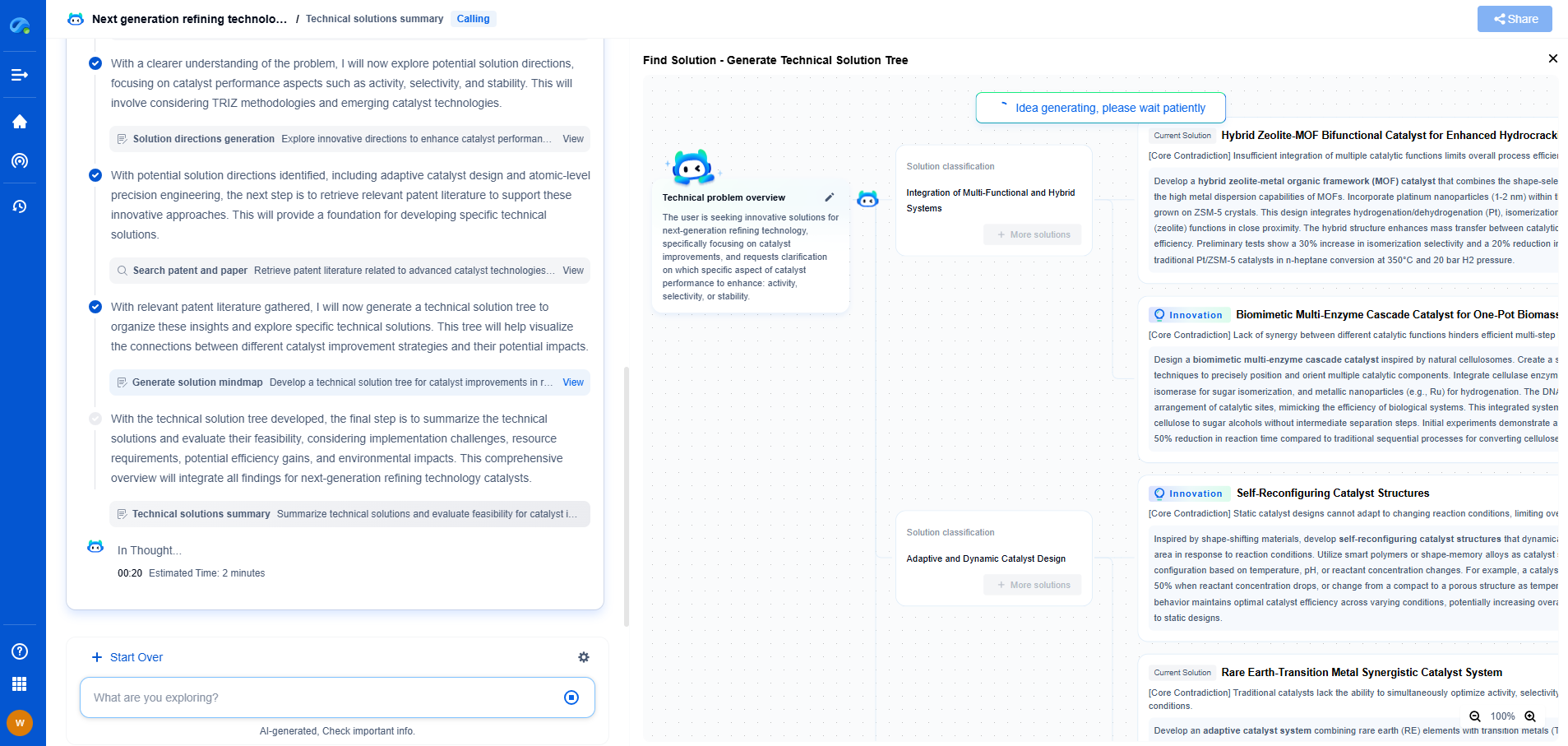

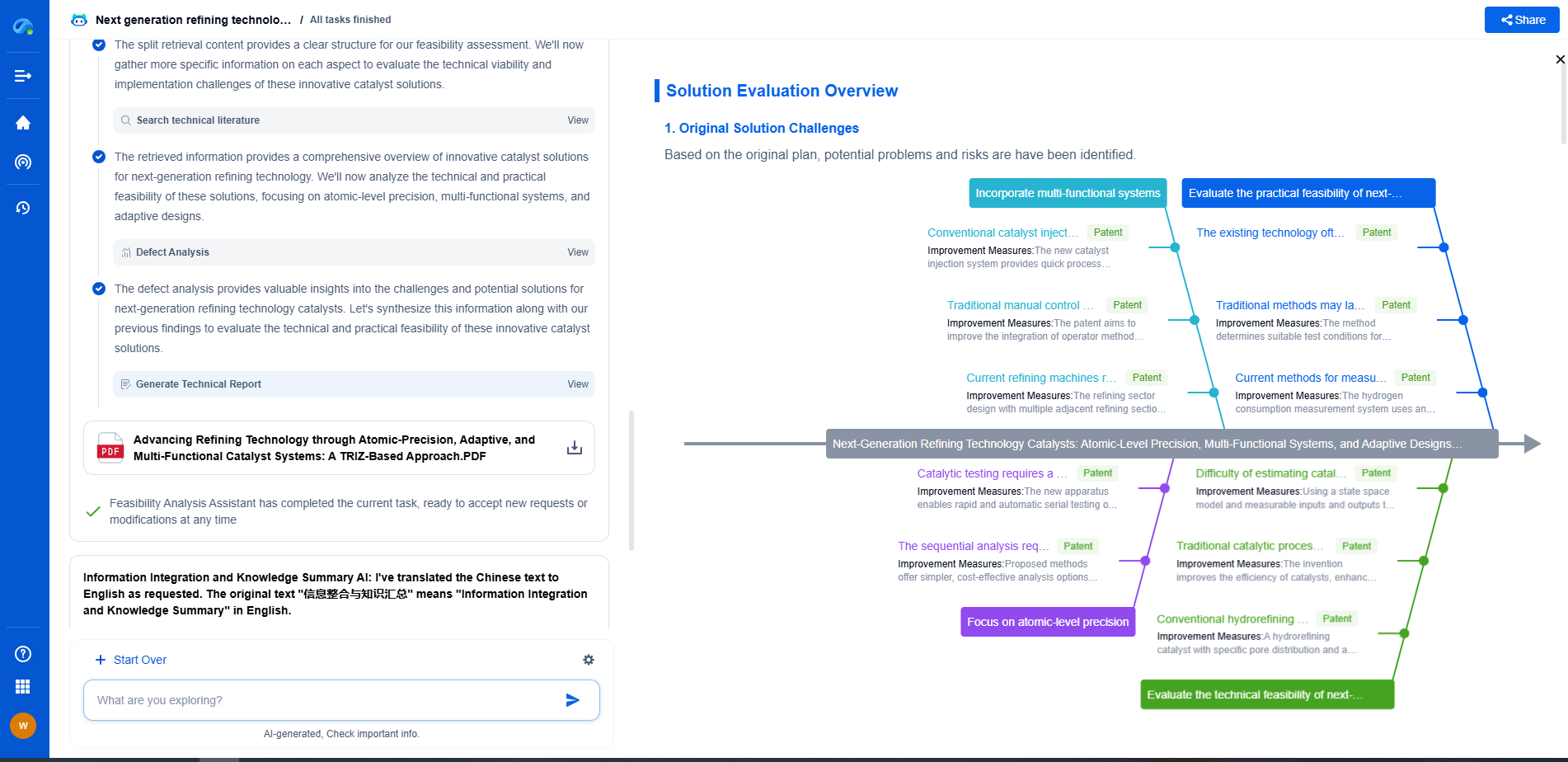

Whether you’re developing multifunctional DAQ platforms, programmable calibration benches, or integrated sensor measurement suites, the ability to track emerging patents, understand competitor strategies, and uncover untapped technology spaces is critical.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

🧪 Let Eureka be your digital research assistant—streamlining your technical search across disciplines and giving you the clarity to lead confidently. Experience it today.