LELE Overlay Errors: First-Layer vs. Second-Layer Alignment

JUL 28, 2025 |

In the world of semiconductor manufacturing, precision and accuracy are paramount. One of the critical challenges faced during the production process is ensuring the proper alignment of layers in lithography. Lithography is the technique used to print intricate circuit patterns onto silicon wafers, and even minor misalignments can lead to significant issues in the final product. Among the various techniques used, LELE (Litho-Etch-Litho-Etch) is a widely adopted double patterning method. However, it is not without its challenges, particularly when it comes to overlay errors between the first and second layers.

Understanding LELE Overlay Errors

Overlay errors refer to the misalignment between different layers of a semiconductor wafer. In a LELE process, these errors can occur both within the same layer and between the first and second layers. Precise alignment is crucial to ensure that the patterns etched onto each layer match up perfectly, allowing for the proper functioning of integrated circuits.

First-Layer Alignment Challenges

The first layer in a LELE process serves as the foundation for subsequent layers. Any misalignment at this stage can propagate through the entire manufacturing process, causing compounded errors in the final product. First-layer alignment errors can arise due to a variety of factors, including equipment inaccuracies, environmental conditions, and variations in the wafer itself. Ensuring accurate alignment at this stage requires meticulous calibration and monitoring to minimize deviations.

Second-Layer Alignment Complexities

While first-layer alignment is critical, the second layer presents its own unique set of challenges. The second-layer alignment must take into account not only the potential errors from the initial patterning but also the complexities introduced by the additional lithography and etching steps. The interaction between the materials used in each layer, as well as the optical properties of the photoresists, can exacerbate alignment issues. In a LELE process, the second layer must be precisely aligned with the first to avoid overlapping or gaps, which can significantly impact device performance.

Comparing First-Layer and Second-Layer Alignment

Though both first-layer and second-layer alignments are critical, they differ in terms of focus and complexity. First-layer alignment primarily focuses on establishing a solid foundation, and errors at this stage can often be adjusted for in subsequent steps. In contrast, second-layer alignment must contend with accumulated errors and any new issues introduced during the process, making it a more complex challenge.

Impact of Overlay Errors on Device Performance

Overlay errors, whether in the first or second layer, can have serious implications for device performance. Misalignment can lead to issues such as electrical shorts, increased leakage currents, and reduced yield. In advanced semiconductor devices where precision is even more crucial, overlay errors can render an entire batch of wafers unusable, leading to significant financial losses. As technology nodes continue to shrink, the tolerance for overlay errors becomes even tighter, further emphasizing the need for precise alignment.

Strategies for Mitigating LELE Overlay Errors

To address the challenges of LELE overlay errors, manufacturers employ a range of strategies. Advanced metrology tools are used to measure alignment with high precision, providing feedback for corrective actions. Process optimization, including the use of sophisticated alignment marks, helps improve the accuracy of layer alignment. Additionally, continuous monitoring and adaptation of the manufacturing environment, such as temperature and humidity control, play a crucial role in minimizing overlay errors.

Conclusion

In the ever-evolving landscape of semiconductor manufacturing, LELE overlay errors in first-layer and second-layer alignments remain a significant concern. Understanding the complexities and differences between these alignment challenges is essential for maintaining high standards of precision and device performance. Through technological advancements and rigorous process control, manufacturers strive to reduce overlay errors, ensuring that the intricate and delicate structures of modern integrated circuits are created with the utmost accuracy.

As photolithography continues to push the boundaries of nanoscale patterning, from EUV and DUV advancements to multi-patterning and maskless lithography, innovation cycles are accelerating—and the IP landscape is becoming more complex than ever.

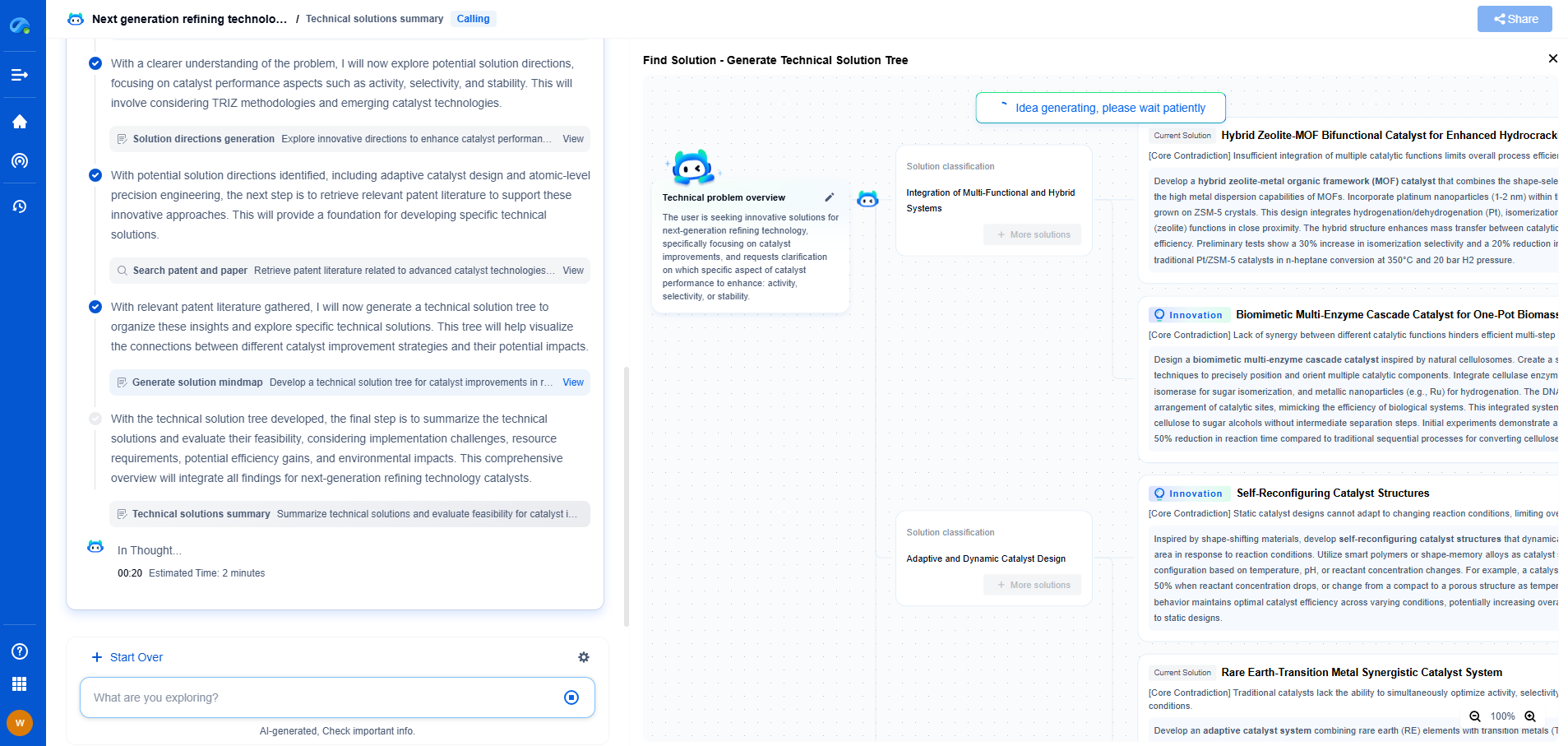

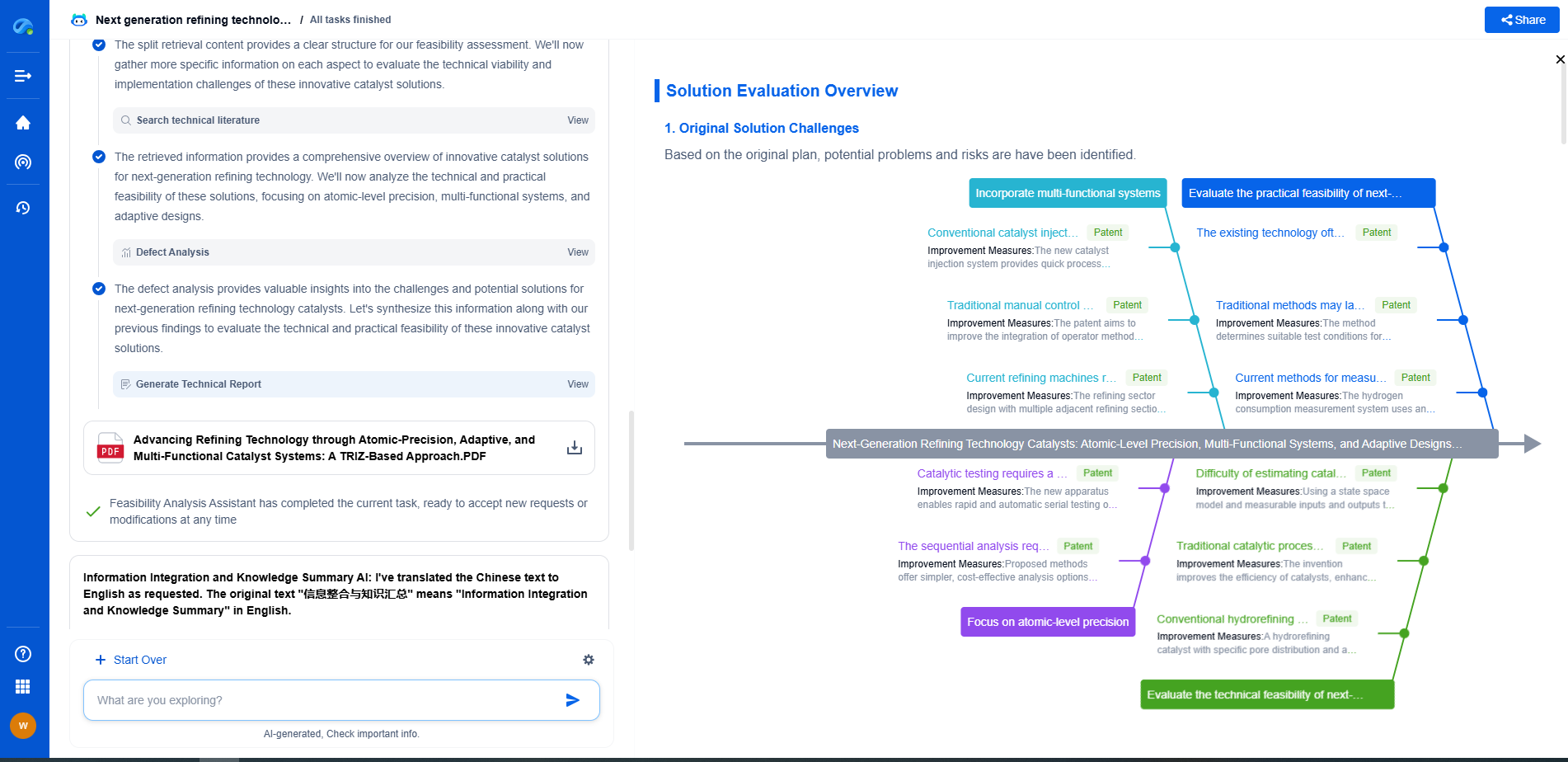

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Whether you're optimizing lithography depth of focus or exploring new materials for sub-3nm nodes, Patsnap Eureka empowers you to make smarter decisions, faster—combining AI efficiency with domain-specific insight.

💡 Start your free trial today and see how Eureka transforms how you discover, evaluate, and act on innovation in photolithography—from idea to impact.