LER vs. LWR: Line Width Roughness Measurement Differences

JUL 28, 2025 |

In the realm of semiconductor manufacturing, precision is paramount. As devices continue to shrink in size, the ability to accurately measure and control various parameters becomes increasingly crucial. Two such parameters are Line Edge Roughness (LER) and Line Width Roughness (LWR). Understanding the differences in their measurement is vital for improving both the quality and performance of semiconductor devices. This blog delves into the intricacies of LER and LWR, shedding light on their measurement differences and significance.

Understanding LER and LWR

Line Edge Roughness (LER) refers to the variations along the edge of a line. In semiconductor terms, this could be the edge of a gate or a wire on a chip. LER is essentially the deviation of the line edge from its intended path, creating a jagged appearance when viewed under magnification. On the other hand, Line Width Roughness (LWR) pertains to the variations in the width of the line itself. It accounts for both edges of the line, essentially measuring the difference between the maximum and minimum widths across a specified length.

Measurement Techniques

The primary challenge in measuring LER and LWR lies in the scale. As semiconductor technology advances, lines can be just a few nanometers wide, making precise measurement daunting. Scanning Electron Microscopy (SEM) is commonly used to measure both LER and LWR. SEM provides high-resolution images that allow for detailed analysis of the line edges and widths. However, there are nuances in the measurement process for each.

Measuring LER involves capturing the edge profile of the line and comparing it to the intended edge path. This requires multiple measurements along the length of the line to account for any variations. LWR measurement, meanwhile, involves calculating the deviation in width, which requires assessing both edges of the line simultaneously. This often means that the precision of LWR measurement is inherently linked to the accuracy of the LER measurement.

Significance of Measurement Differences

The differences in measuring LER and LWR have significant implications for semiconductor manufacturing. LER primarily affects the performance of transistors. High LER can lead to increased leakage currents and reduced performance, as the jagged edges can disrupt the uniform electric fields across the transistor channels. LWR, however, is a critical parameter for ensuring uniformity in device performance across a chip. Variations in line width can result in inconsistent electrical properties, affecting the overall chip performance.

Technological Advances and Challenges

Recent advancements in measurement technology have improved the accuracy and precision of both LER and LWR measurements. Techniques such as Atomic Force Microscopy (AFM) and advanced imaging algorithms provide more detailed insights into line roughness. However, challenges remain. As device geometries shrink further, the demand for even more precise measurement techniques grows. Additionally, the effects of roughness on device performance become more pronounced as lines become thinner.

Conclusion

In the competitive world of semiconductor manufacturing, every detail counts. Understanding the differences in measuring LER and LWR is essential for fabricating high-performance devices. While both parameters are crucial, they impact device performance in different ways, necessitating precise measurement and control. As technology continues to advance, the quest for ever-more accurate measurements will remain a cornerstone of semiconductor development. Through continued innovation and research, the industry aims to meet the challenges posed by decreasing feature sizes, ensuring the production of reliable and efficient semiconductor devices.

As photolithography continues to push the boundaries of nanoscale patterning, from EUV and DUV advancements to multi-patterning and maskless lithography, innovation cycles are accelerating—and the IP landscape is becoming more complex than ever.

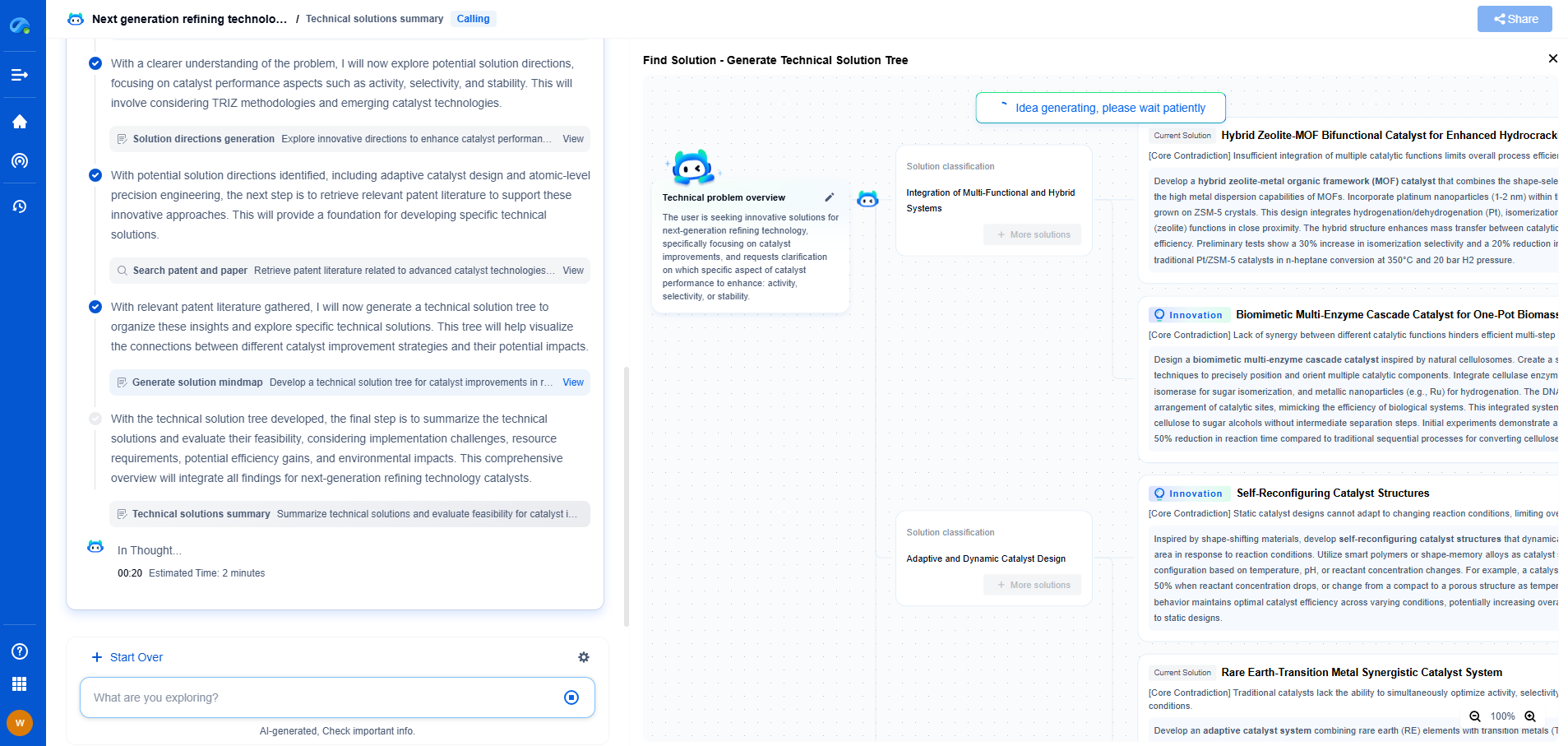

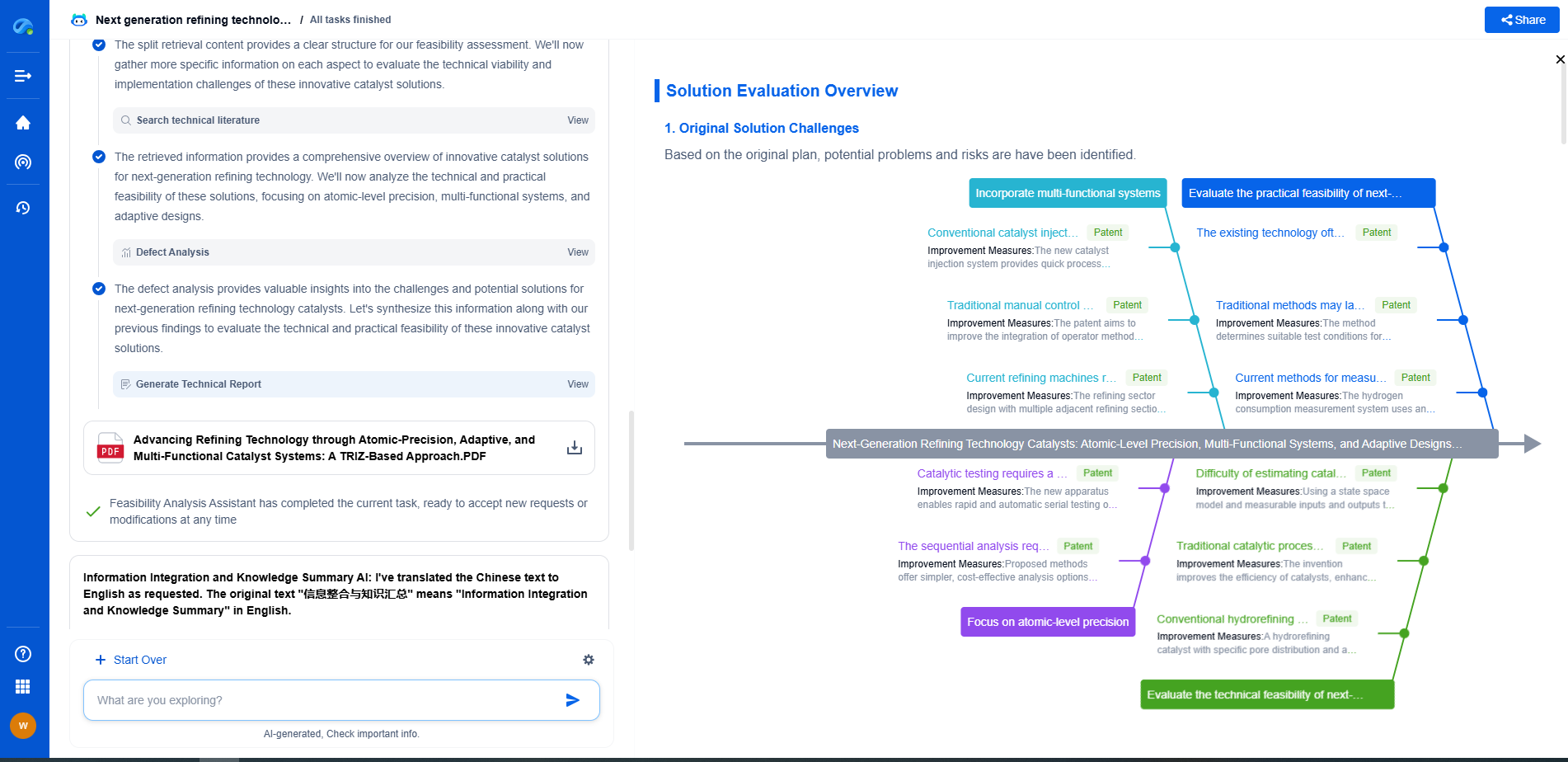

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Whether you're optimizing lithography depth of focus or exploring new materials for sub-3nm nodes, Patsnap Eureka empowers you to make smarter decisions, faster—combining AI efficiency with domain-specific insight.

💡 Start your free trial today and see how Eureka transforms how you discover, evaluate, and act on innovation in photolithography—from idea to impact.