Low-Power Digital Filtering in Embedded Measurement Devices

JUL 17, 2025 |

Digital filtering is a crucial process in embedded measurement devices, employed to extract useful information from signals while discarding unwanted noise. Embedded systems often operate under stringent resource constraints, including limited power supply, which necessitates the implementation of low-power digital filtering techniques. The challenge lies in achieving high-quality signal processing without compromising energy efficiency.

The Importance of Low-Power Design

In the realm of embedded systems, power consumption is a critical consideration. Many embedded devices are battery-operated, such as portable medical equipment, sensor nodes in remote locations, or wearable technology. Excessive power usage can lead to frequent battery replacements or recharging, hindering the device's practicality and user experience. Therefore, optimizing digital filtering algorithms for low power consumption is essential to prolong battery life while maintaining effective signal processing capabilities.

Types of Digital Filters

Digital filters can be broadly categorized into two types: Finite Impulse Response (FIR) filters and Infinite Impulse Response (IIR) filters. Each has its own advantages and challenges concerning power consumption.

1. Finite Impulse Response (FIR) Filters: FIR filters offer stability and a linear phase response, making them suitable for applications where phase linearity is crucial. However, they often require more computational resources due to the need for more coefficients, which can impact power consumption. Techniques such as coefficient optimization and the use of symmetric filter structures can help mitigate power usage.

2. Infinite Impulse Response (IIR) Filters: IIR filters generally require fewer coefficients than FIR filters, potentially reducing computational demands. However, they may introduce stability issues and nonlinear phase responses, which must be carefully managed. Efficient implementation strategies, such as cascaded filter structures and fixed-point arithmetic, can enhance their power efficiency.

Techniques for Low-Power Digital Filtering

To achieve low-power digital filtering, developers can employ several strategies:

1. Algorithm Optimization: Reducing the number of arithmetic operations within the filtering algorithm directly impacts power consumption. Techniques like loop unrolling, strength reduction, and exploiting filter symmetry can decrease the computational load.

2. Hardware Acceleration: Utilizing hardware accelerators, such as Digital Signal Processors (DSPs) or Application-Specific Integrated Circuits (ASICs), can offload complex filtering tasks from the main processor, reducing power usage. These specialized components are optimized for specific operations, enhancing overall efficiency.

3. Dynamic Voltage and Frequency Scaling (DVFS): Adjusting the voltage and frequency of the processor according to the workload can significantly reduce power consumption. During periods of low processing demand, lowering these parameters conserves energy without affecting performance.

4. Sleep Modes and Duty Cycling: Implementing sleep modes and duty cycling allows the processor to enter a low-power state when not actively filtering data. Carefully designed scheduling can ensure that the processor wakes only when necessary, minimizing energy expenditure.

Evaluating the Impact of Low-Power Filtering

Evaluating the performance of low-power digital filtering involves balancing power consumption with signal processing quality. Metrics such as Signal-to-Noise Ratio (SNR), filter delay, and energy per operation provide insights into the efficiency of the implemented filter. Real-world testing, alongside simulation, can help developers fine-tune their algorithms to achieve the desired power-performance trade-off.

Conclusion

Low-power digital filtering in embedded measurement devices is a delicate balancing act of optimizing algorithms and utilizing hardware efficiently to extend battery life without compromising signal integrity. By understanding the characteristics of FIR and IIR filters and employing advanced techniques, developers can design embedded systems that deliver high-quality data processing while operating within stringent power constraints. As technology continues to advance, these strategies will remain pivotal in the development of next-generation embedded measurement devices.

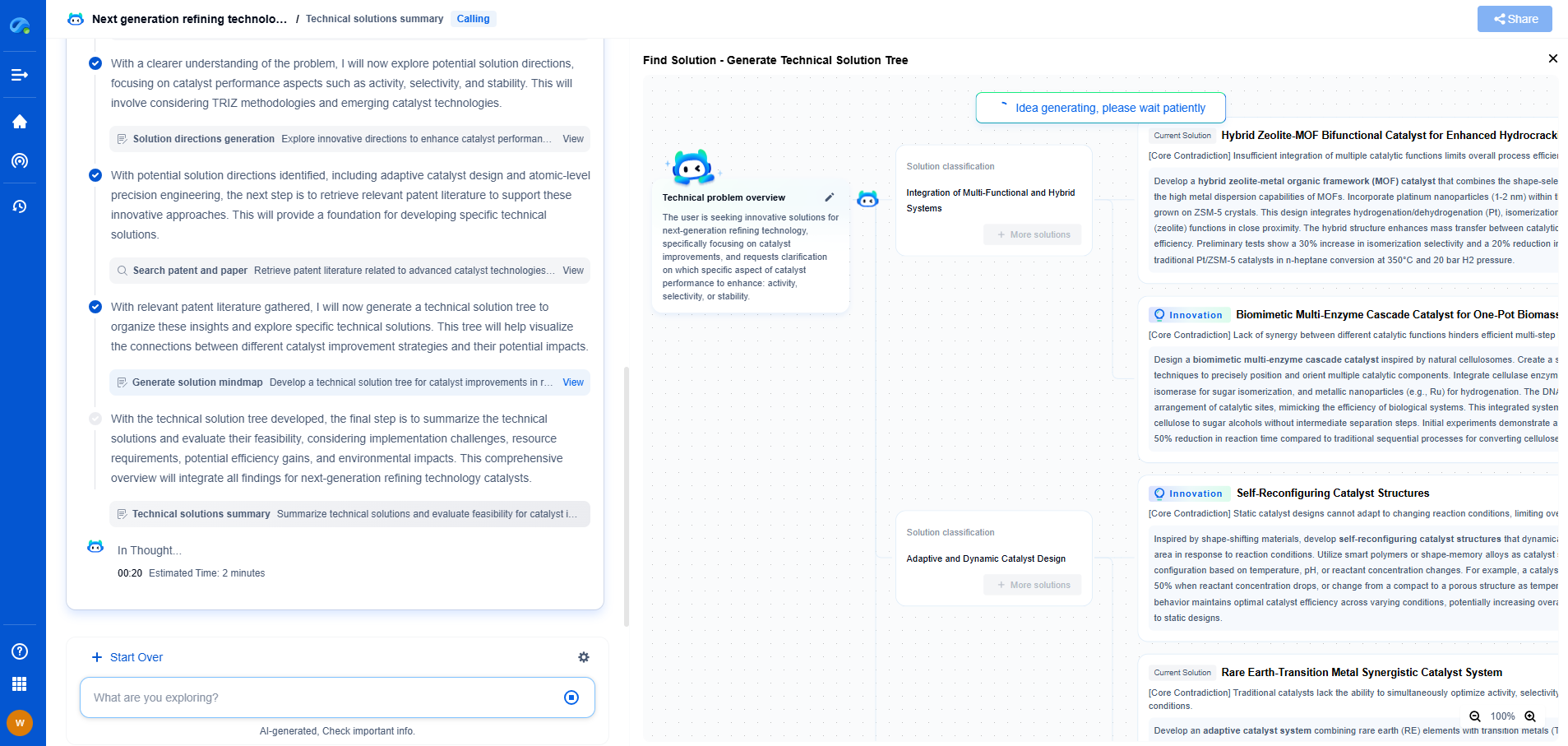

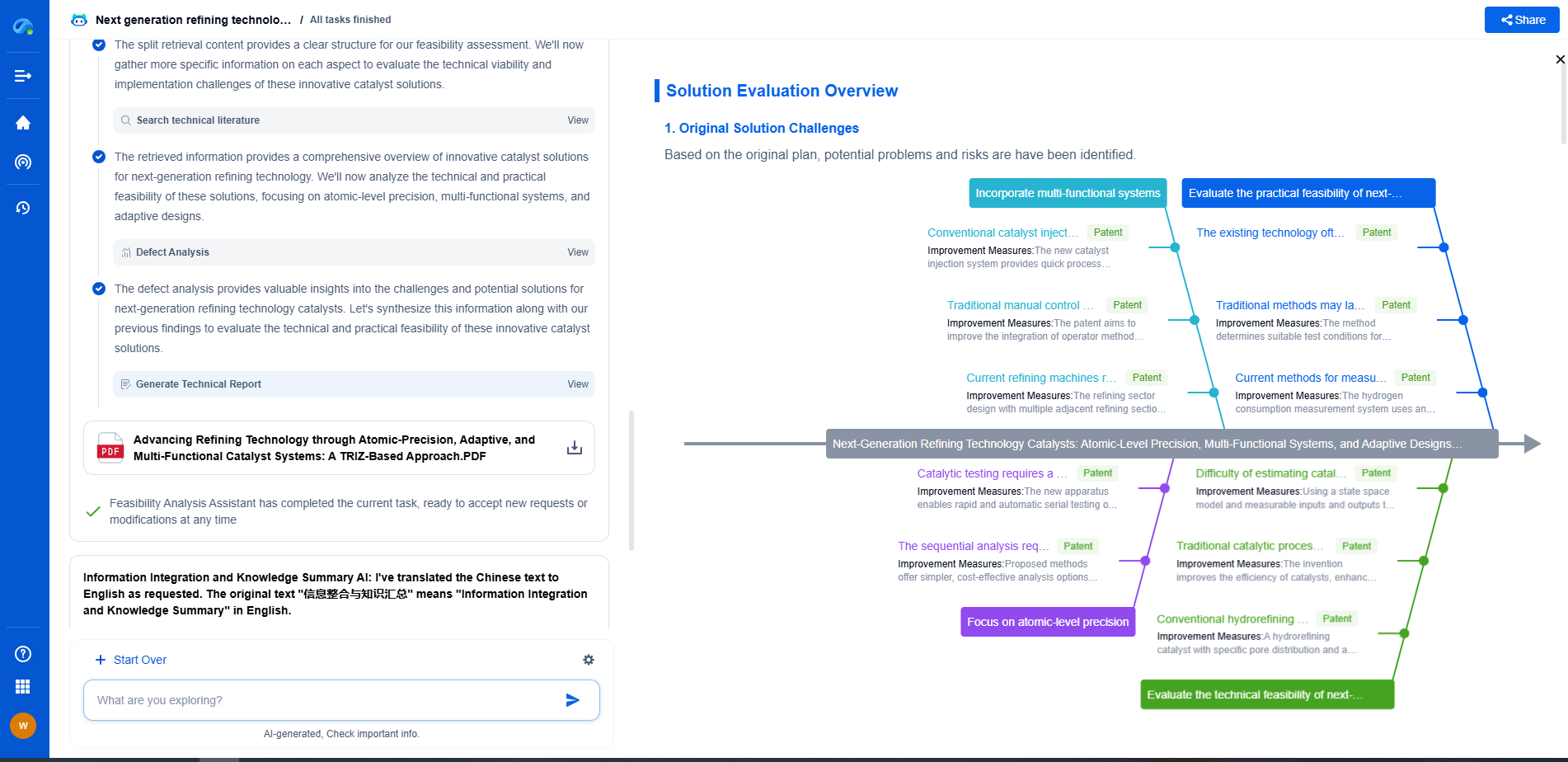

Whether you’re developing multifunctional DAQ platforms, programmable calibration benches, or integrated sensor measurement suites, the ability to track emerging patents, understand competitor strategies, and uncover untapped technology spaces is critical.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

🧪 Let Eureka be your digital research assistant—streamlining your technical search across disciplines and giving you the clarity to lead confidently. Experience it today.