Mitigating Temperature Effects in SOI Piezoresistors

JUL 14, 2025 |

Silicon-On-Insulator (SOI) technology has revolutionized the design and performance of piezoresistors, offering improved sensitivity and reduced parasitic capacitance. However, like most semiconductor devices, SOI piezoresistors are susceptible to temperature variations, which can affect their performance and reliability. In this article, we will explore strategies to mitigate the effects of temperature on SOI piezoresistors, ensuring consistent performance across a range of operating conditions.

Understanding Temperature Effects in SOI Piezoresistors

Temperature variations can influence the electrical characteristics of SOI piezoresistors, notably their resistance and sensitivity. The primary factors affected by temperature include carrier mobility, bandgap energy, and intrinsic carrier concentration, all of which contribute to changes in resistance. As temperature increases, carrier mobility tends to decrease due to increased phonon scattering, while the intrinsic carrier concentration increases, leading to a reduction in resistivity. These variations can lead to inaccuracies in sensor measurements and reduced device performance.

Design Strategies for Temperature Compensation

1. Material Selection

Selecting the appropriate materials for SOI piezoresistors is crucial in mitigating temperature effects. High-quality silicon wafers with low defect densities are preferred to ensure stable performance. Additionally, doping levels can be optimized to minimize the temperature coefficient of resistance (TCR). The use of high-resistivity silicon or materials with a narrow TCR can significantly reduce temperature-induced variations.

2. Structural Design Optimization

The design of the piezoresistor structure plays a pivotal role in temperature compensation. Implementing symmetric designs can help balance thermal expansion and minimize mechanical stress. Employing a Wheatstone bridge configuration is another effective strategy, as it inherently compensates for temperature variations by comparing resistances, thus negating common-mode temperature effects.

3. Thin-Film Techniques

The use of thin-film techniques allows for precise control of the piezoresistor dimensions and doping profiles, leading to enhanced temperature stability. By tailoring the thickness and doping concentration, engineers can achieve a more stable TCR. Additionally, passivation layers can be applied to protect the piezoresistors from environmental temperature fluctuations, further enhancing thermal stability.

Advanced Compensation Techniques

1. Active Temperature Compensation

Active temperature compensation involves the use of additional circuitry to dynamically adjust the piezoresistor's output in response to temperature changes. This can be achieved through the integration of temperature sensors and compensation algorithms within the device. By continuously monitoring the temperature and adjusting the output accordingly, active compensation ensures consistent performance across a wide temperature range.

2. Calibration and Correction Algorithms

Implementing calibration and correction algorithms can effectively mitigate temperature effects in SOI piezoresistors. These algorithms use pre-characterized temperature-resistance data to adjust the sensor output in real-time. By incorporating machine learning techniques, these algorithms can adapt to varying environmental conditions, improving the accuracy and reliability of the piezoresistors.

3. Thermal Isolation Techniques

Thermal isolation techniques aim to minimize the influence of external temperature changes on the piezoresistor. This can be achieved through the use of microfabricated structures that isolate the sensing element from the substrate, reducing heat transfer. Additionally, thermal insulation materials can be employed to shield the piezoresistors from rapid temperature fluctuations, ensuring steady performance.

Conclusion

Mitigating temperature effects in SOI piezoresistors is essential for maintaining their reliability and accuracy in various applications. By employing strategic design choices, advanced compensation techniques, and appropriate material selection, engineers can significantly reduce the impact of temperature variations. As technology continues to advance, further improvements in SOI piezoresistor performance will contribute to their widespread adoption in diverse fields, from automotive sensors to biomedical devices.

From 5G NR to SDN and quantum-safe encryption, the digital communication landscape is evolving faster than ever. For R&D teams and IP professionals, tracking protocol shifts, understanding standards like 3GPP and IEEE 802, and monitoring the global patent race are now mission-critical.

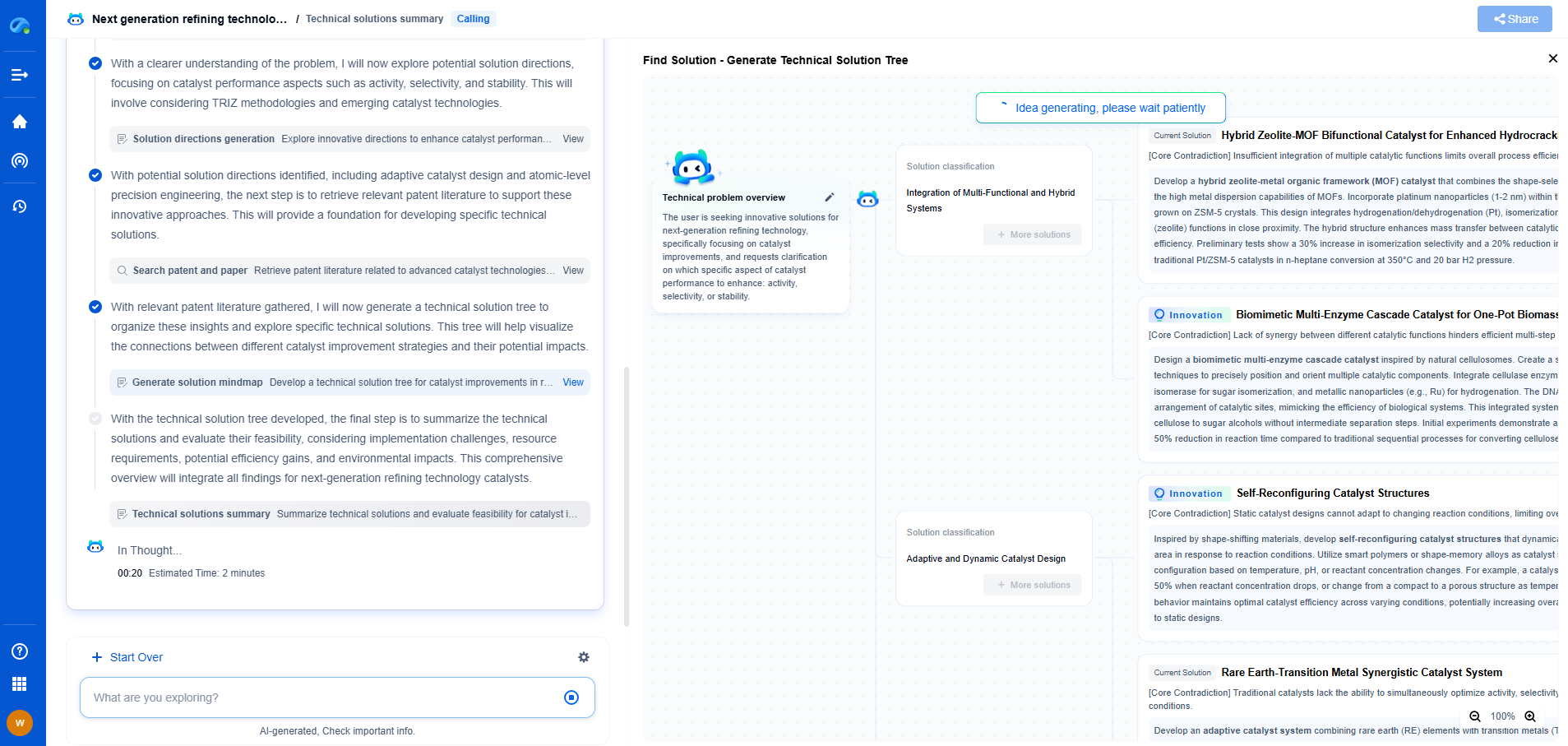

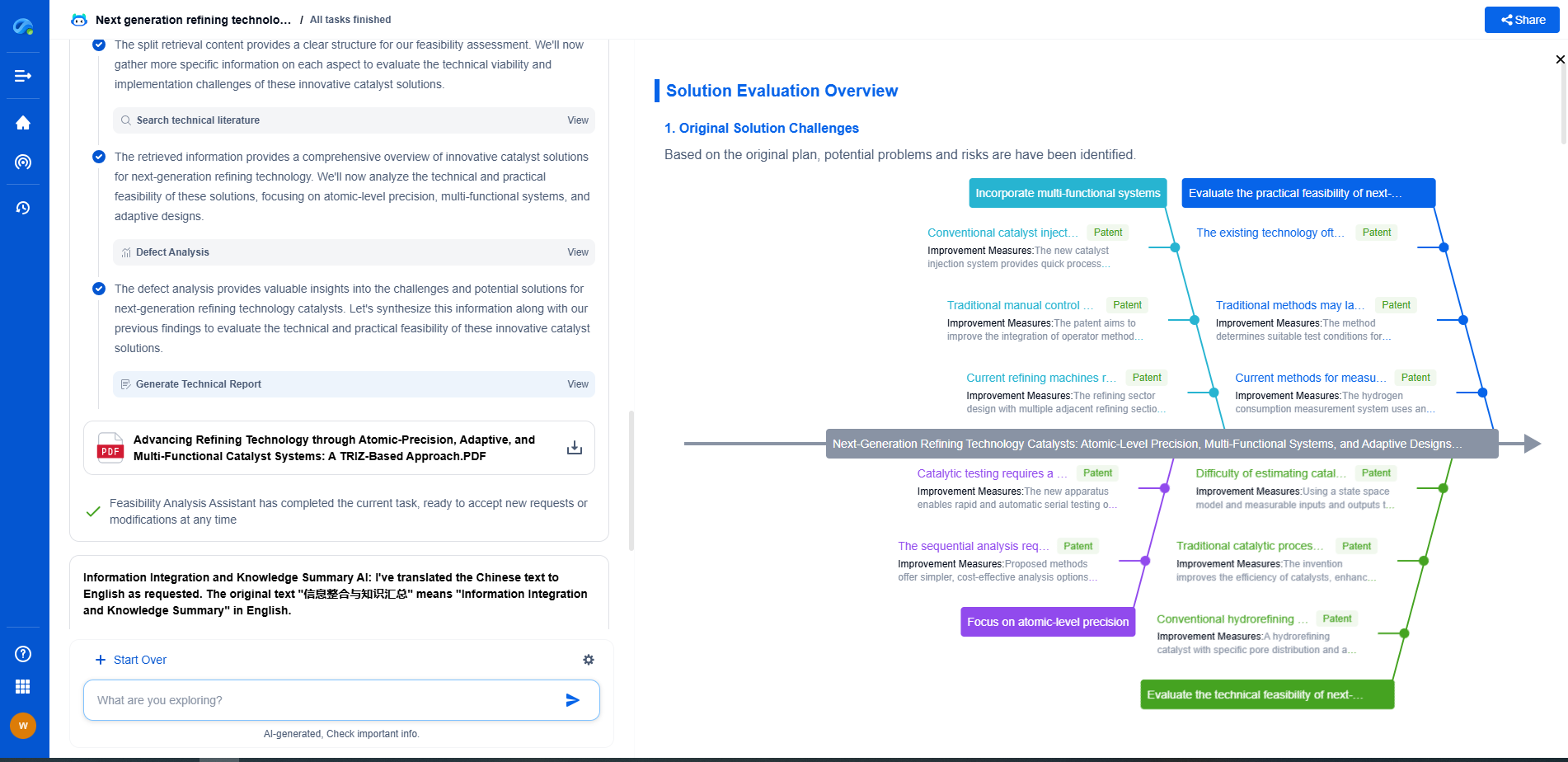

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

📡 Experience Patsnap Eureka today and unlock next-gen insights into digital communication infrastructure, before your competitors do.