Multi-Patterning Lithography: Why Do We Need Multiple Masks?

JUL 28, 2025 |

As semiconductor technology advances, the demand for smaller, faster, and more power-efficient devices continues to grow. A significant part of achieving these gains lies in the lithography process used in chip manufacturing. The traditional single-patterning lithography methods, which have served the industry for decades, are now reaching their physical limitations. This is where multi-patterning lithography comes into play, allowing chipmakers to push beyond the constraints of conventional lithography.

What is Multi-Patterning Lithography?

Multi-patterning lithography refers to the use of multiple photomasks to achieve finer patterns on silicon wafers than what could be accomplished with a single mask. This technique involves several iterations of lithography steps, each adding more precision to the pattern being printed. The need for multiple masks arises from the fact that as the features on chips become smaller, the ability to accurately transfer these patterns with a single exposure becomes increasingly difficult due to the diffraction limits of light.

Why Do We Need Multiple Masks?

The use of multiple masks is essential for several reasons. Firstly, the resolution limit of existing photolithography equipment means that a single patterning step cannot produce the tiny features required for advanced nodes. By using multiple masks, manufacturers can divide the complex patterns into simpler components, aligning and overlapping them precisely to create the desired intricate circuitry.

Secondly, as the process nodes get smaller, the critical dimension control becomes more stringent. Multi-patterning allows for better management of these dimensions, ensuring that each layer of the chip aligns perfectly with the others. This precision is crucial for maintaining the electrical integrity of the circuits and enabling the proper functioning of the final product.

Types of Multi-Patterning Techniques

There are several multi-patterning techniques, each suited to different types of patterning challenges:

1. **Double Patterning (DPT)**: The simplest form of multi-patterning, where a single layer is split into two separate exposures. This is often used in conjunction with existing lithography tools to improve resolution without a complete overhaul of the process.

2. **Triple and Quadruple Patterning (TPT/QPT)**: These techniques extend the double patterning approach by adding additional mask layers. As the complexity and density of integrated circuits increase, these methods provide the necessary precision and control.

3. **Self-Aligned Patterning**: This includes techniques like Self-Aligned Double Patterning (SADP) and Self-Aligned Quadruple Patterning (SAQP), which use spacer-defined features to achieve even finer resolutions. These methods are highly precise as they rely on the self-alignment of features, reducing the risk of overlay errors.

Challenges and Considerations

While multi-patterning offers significant advantages, it also introduces new challenges. The most obvious is cost—each additional mask and processing step adds to the manufacturing expense. This makes the process economically viable only for high-demand products.

Moreover, the complexity of the process increases with additional steps, requiring more sophisticated equipment and highly skilled personnel to manage the intricacies of mask alignment and pattern fidelity. Any error in the process can lead to defects that are expensive to rectify.

The Future of Multi-Patterning Lithography

As the industry continues to push towards smaller nodes with ever-wider applications, the importance of multi-patterning in lithography is unquestionable. However, the search for more cost-effective and efficient methods is ongoing, with extreme ultraviolet (EUV) lithography being one promising alternative for the future. EUV offers the potential to simplify the process by reducing the number of masks needed, albeit with its challenges to overcome.

In conclusion, multi-patterning lithography is a critical technology that enables the continued miniaturization of semiconductor devices. While it presents its own set of challenges, the ability to produce smaller and more complex features makes it an indispensable tool in the ever-evolving landscape of semiconductor manufacturing.

As photolithography continues to push the boundaries of nanoscale patterning, from EUV and DUV advancements to multi-patterning and maskless lithography, innovation cycles are accelerating—and the IP landscape is becoming more complex than ever.

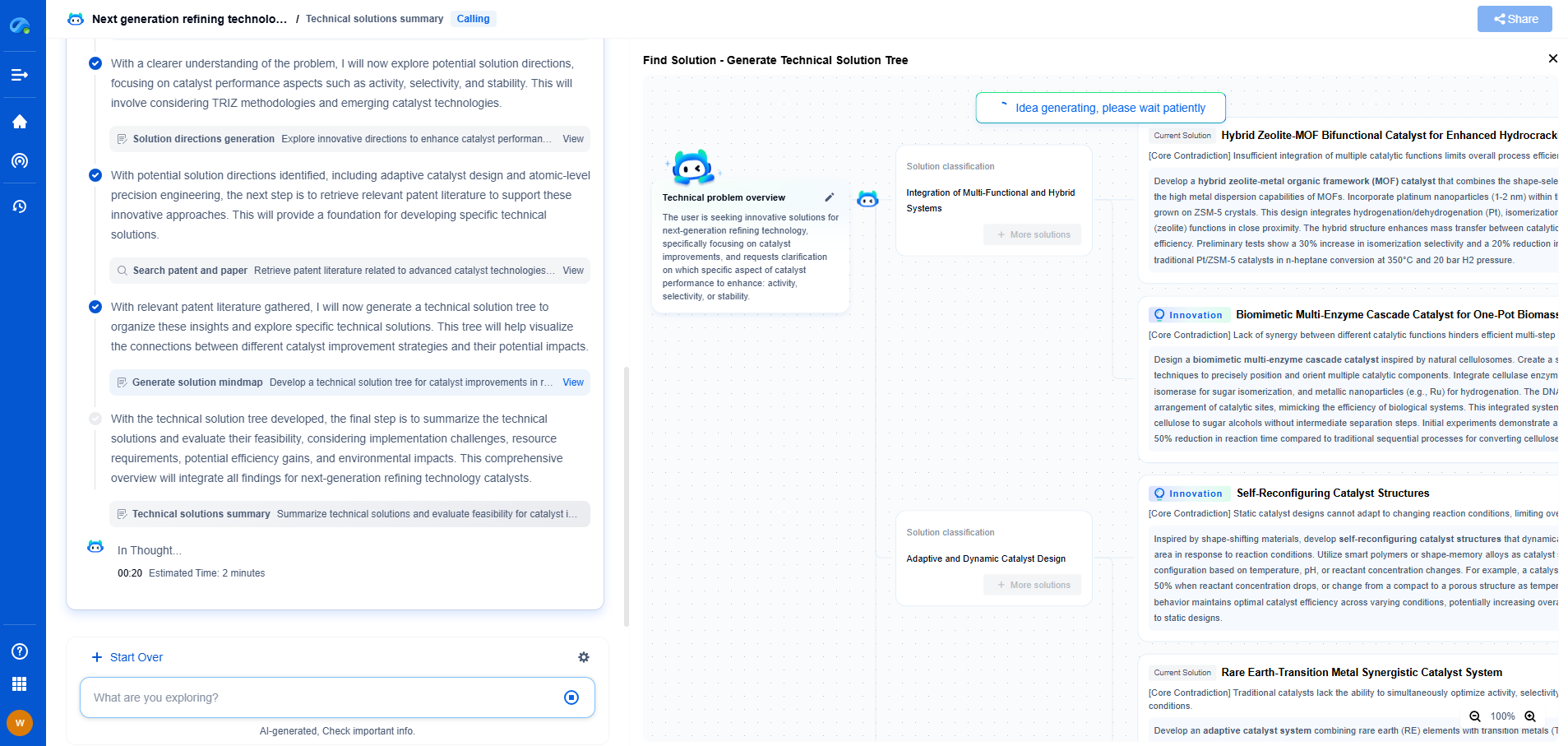

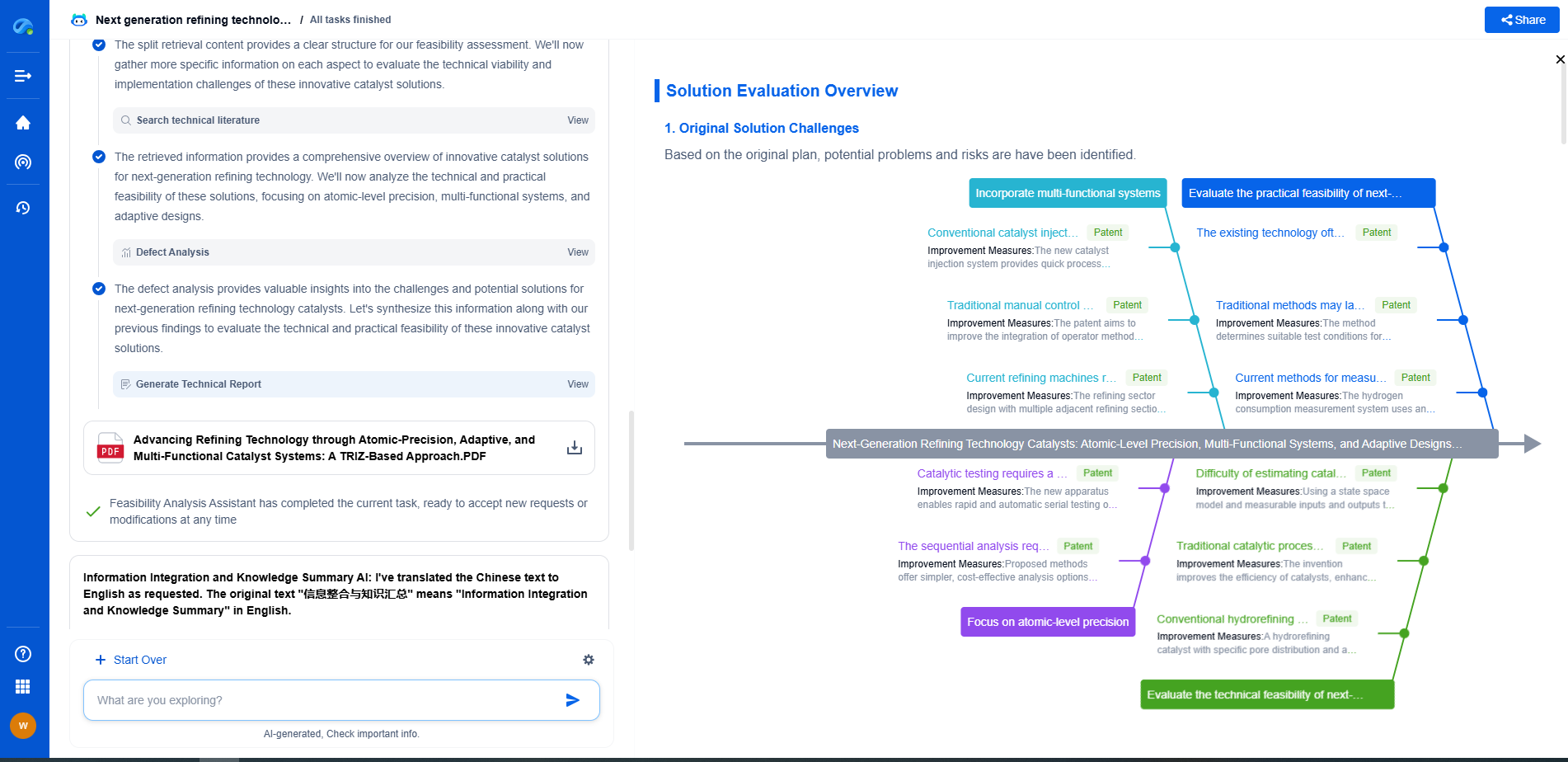

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Whether you're optimizing lithography depth of focus or exploring new materials for sub-3nm nodes, Patsnap Eureka empowers you to make smarter decisions, faster—combining AI efficiency with domain-specific insight.

💡 Start your free trial today and see how Eureka transforms how you discover, evaluate, and act on innovation in photolithography—from idea to impact.