Signal Integrity Considerations in Interdigitated Capacitor Structures

JUL 9, 2025 |

Signal integrity is a critical design aspect in high-frequency electronic circuits, particularly when dealing with components like interdigitated capacitors (IDCs). These structures are often employed in RF and microwave applications due to their compact size and the ability to provide high capacitance values. However, the unique geometry of IDCs introduces several challenges that can affect signal integrity. This article explores these considerations and offers insights into optimizing IDC designs for superior performance.

Understanding Interdigitated Capacitor Structures

Interdigitated capacitors consist of interlaced fingers from two or more conductive layers, creating a high-density capacitive structure. The proximity and arrangement of these fingers significantly influence the electrical characteristics, such as capacitance, inductance, and resistance. At high frequencies, the parasitic effects become prominent, impacting signal integrity. Therefore, a thorough understanding of the IDC's physical layout and its interaction with the surrounding environment is essential for maintaining signal integrity.

Parasitic Effects and Their Impact on Signal Integrity

One of the primary challenges in IDC structures is managing parasitic effects. Parasitic capacitance and inductance can lead to signal distortion, increased noise, and crosstalk. The close proximity of the conductive fingers in IDCs inherently creates parasitic capacitance, which can inadvertently couple signals between adjacent lines or components. This coupling can degrade the signal quality and lead to unwanted resonances.

Additionally, parasitic inductance, often caused by the loop areas formed by the signal paths, can introduce inductive reactance, which further complicates the signal integrity. To mitigate these effects, careful consideration of the finger width, length, and spacing is necessary, as well as the use of low-loss dielectric materials to minimize unwanted interactions.

Design Strategies for Improved Signal Integrity

Effective design strategies are crucial for optimizing signal integrity in interdigitated capacitor structures. One approach is to minimize the parasitic inductance by reducing the loop areas, which can be achieved by optimizing the layout and alignment of the interdigitated fingers. Additionally, selecting materials with low dielectric loss and high dielectric constant can help maintain signal integrity by reducing losses.

Furthermore, incorporating ground planes or shielding layers can help suppress electromagnetic interference and reduce crosstalk between adjacent traces. This shielding can be particularly beneficial in densely packed circuits where space constraints may exacerbate parasitic effects.

Simulation and Modeling Techniques

Accurate simulation and modeling are indispensable tools for predicting the behavior of IDC structures under various operating conditions. Electromagnetic simulation software can provide insights into the electric and magnetic fields within the capacitor, helping designers identify potential problem areas and optimize the geometry for better signal integrity.

By utilizing these tools, designers can experiment with different configurations and materials virtually, allowing for refined designs that anticipate and mitigate signal integrity issues before physical prototyping.

Considerations for Manufacturing and Testing

Once the design is optimized, manufacturing processes must be carefully managed to ensure that the theoretical benefits are realized in practice. Precision fabrication techniques are essential to achieve the tight tolerances required for IDC structures. Moreover, thorough testing and characterization of the final product are crucial to validate its performance and ensure it meets the desired specifications.

Conclusion

Interdigitated capacitors offer significant advantages in compact and high-density circuit designs but come with unique challenges that can impact signal integrity. By understanding the parasitic effects and employing strategic design and simulation techniques, these challenges can be effectively managed. As technology continues to advance and demand for high-speed, high-frequency applications grows, mastering these considerations will be increasingly important for engineers and designers working with interdigitated capacitor structures.

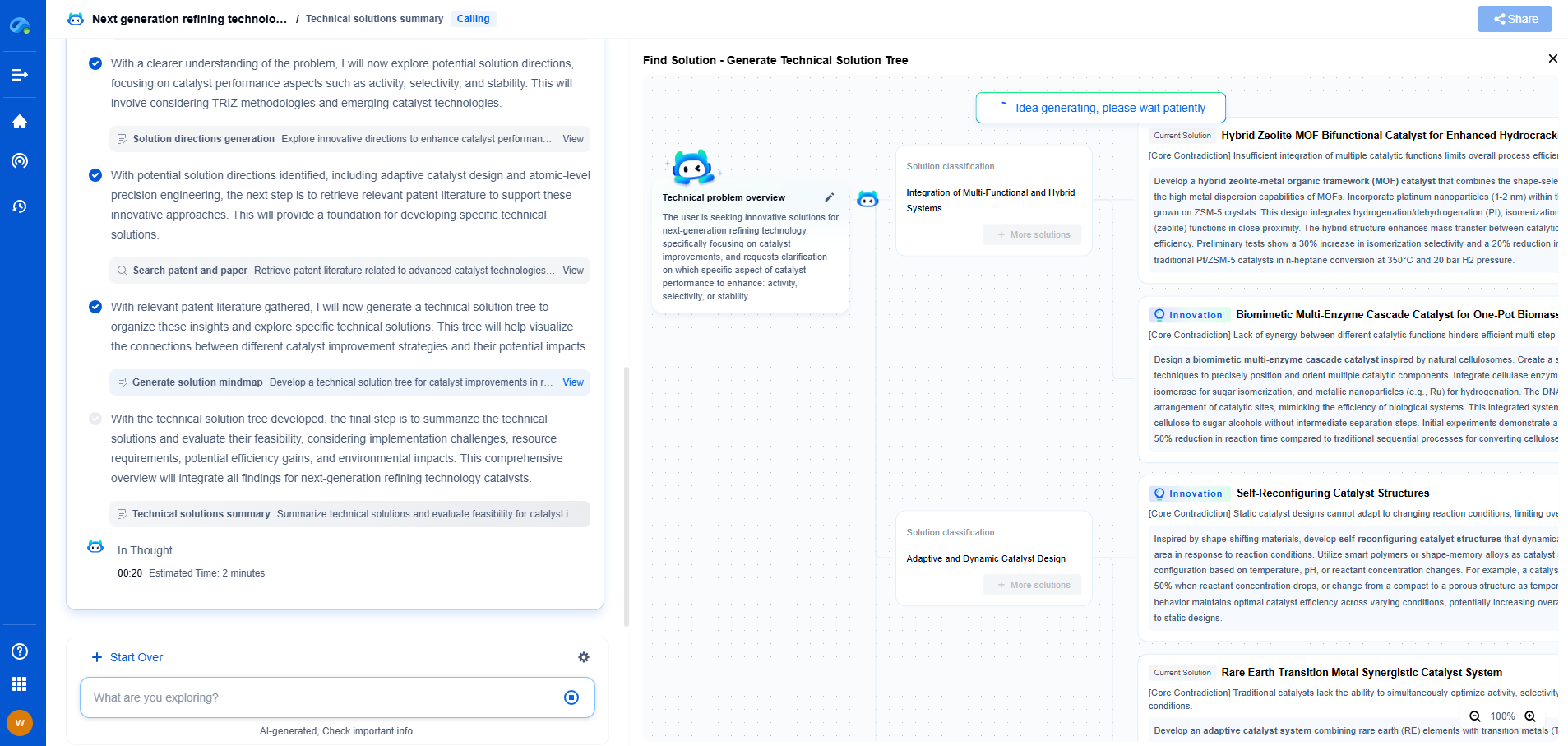

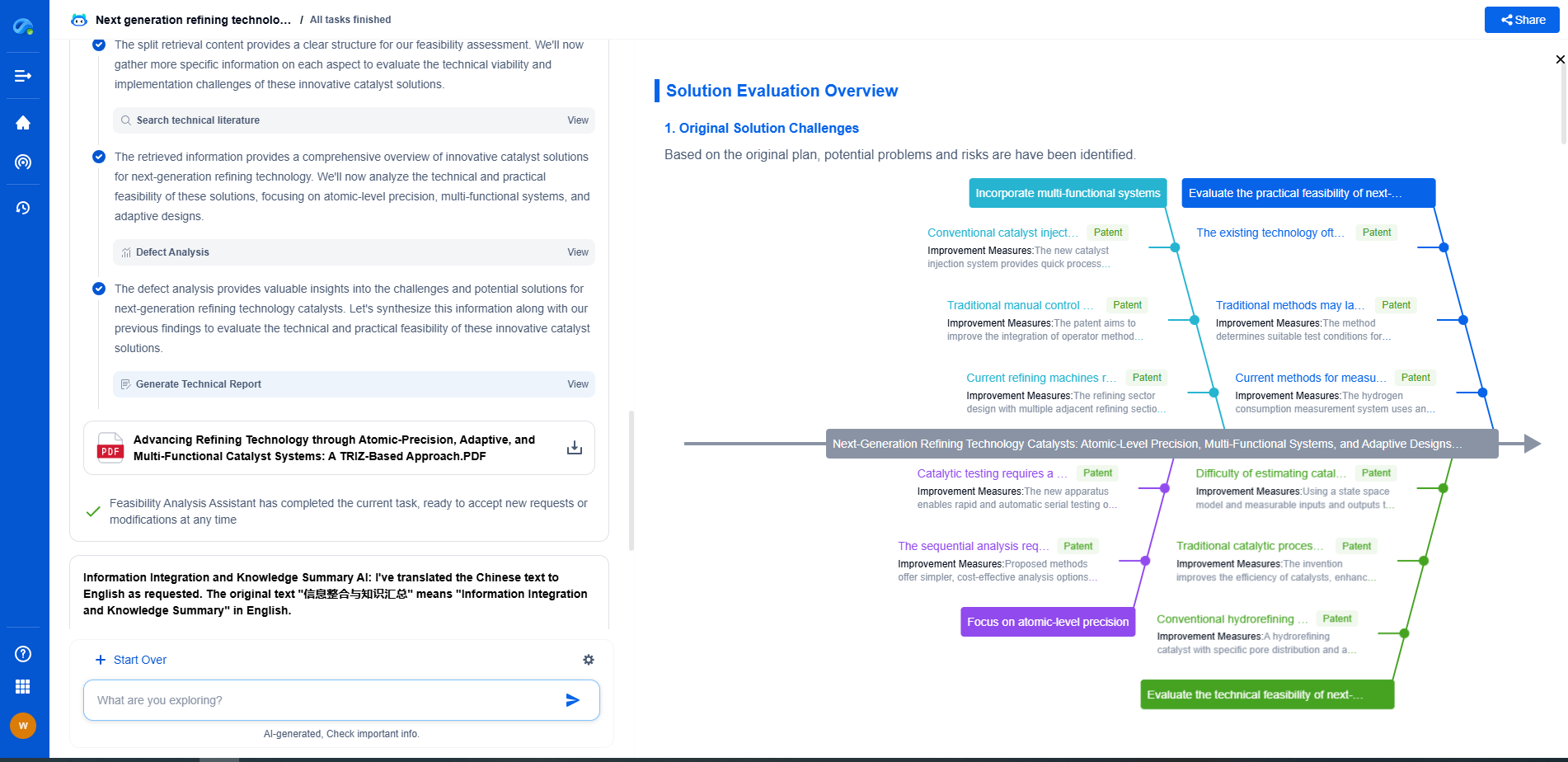

Looking to accelerate your capacitor innovation pipeline?

As capacitor technologies evolve—from miniaturized MLCCs for smartphones to grid-scale energy storage devices—so must the way your team accesses critical knowledge.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Try Patsnap Eureka now and discover a faster, smarter way to research and innovate in capacitor technology.