Tips for Reducing Measurement Latency in Embedded Systems

JUL 17, 2025 |

Measurement latency in embedded systems refers to the time delay between the initiation of a measurement process and the acquisition of the data. This delay can impact system performance, especially in real-time applications where timely data processing is crucial. Understanding and reducing measurement latency can significantly enhance the responsiveness and efficiency of embedded systems.

Understanding Causes of Measurement Latency

Before diving into solutions, it is essential to understand what causes measurement latency in embedded systems. Several factors can contribute to this delay, including signal processing time, data conversion processes, communication delays, and software processing time. By identifying these factors, developers can target specific areas for improvement.

Optimize Signal Processing

One of the primary contributors to measurement latency is the time taken to process incoming signals. To reduce this latency, ensure that signal processing algorithms are optimized for speed. This may involve using more efficient algorithms, reducing the complexity of calculations, or employing hardware accelerators that can handle specific tasks more quickly than the main processor.

Enhance Data Conversion Techniques

Analog-to-digital conversion (ADC) and digital-to-analog conversion (DAC) are inherent in many embedded systems. These processes can introduce significant delays if not optimized. Choosing ADCs and DACs with faster conversion rates can help minimize these delays. Additionally, using devices with built-in buffering can allow data to be processed in parallel, further reducing latency.

Minimize Communication Delays

Communication delays often occur when data is transferred between different components of an embedded system. Utilizing faster communication protocols and buses can help reduce these delays. For example, switching to SPI or I2C buses with higher data rates can improve communication efficiency. Furthermore, minimizing the distance over which data must travel and reducing the number of communication hops can also help lower latency.

Streamline Software Execution

The software running on an embedded system can significantly impact measurement latency. Optimizing software can involve several strategies, such as:

- Prioritizing Critical Tasks: Implement real-time operating systems (RTOS) to ensure that time-sensitive tasks receive priority processing.

- Code Optimization: Review and optimize code to eliminate unnecessary computations and streamline execution paths.

- Scheduling Efficiency: Use effective task scheduling techniques to minimize idle time and ensure timely task execution.

Utilize Dedicated Hardware Components

In some cases, offloading specific tasks to dedicated hardware components can reduce measurement latency. For example, using hardware timers for precise timing or employing dedicated coprocessors for intensive calculations can offload the main processor, allowing it to handle other tasks more efficiently.

Implement Predictive and Adaptive Techniques

Predictive and adaptive techniques can also aid in reducing latency. By anticipating future system states or adapting to current conditions, embedded systems can streamline processes and reduce the time taken to react to changes. Implementing machine learning algorithms or using adaptive filters can enable systems to respond more quickly to dynamic environments.

Conclusion

Reducing measurement latency in embedded systems is critical for enhancing performance, particularly in real-time applications. By understanding the causes of latency and implementing targeted strategies, developers can significantly improve system responsiveness. From optimizing algorithms to utilizing specialized hardware, these tips can help create more efficient and effective embedded systems.

Whether you’re developing multifunctional DAQ platforms, programmable calibration benches, or integrated sensor measurement suites, the ability to track emerging patents, understand competitor strategies, and uncover untapped technology spaces is critical.

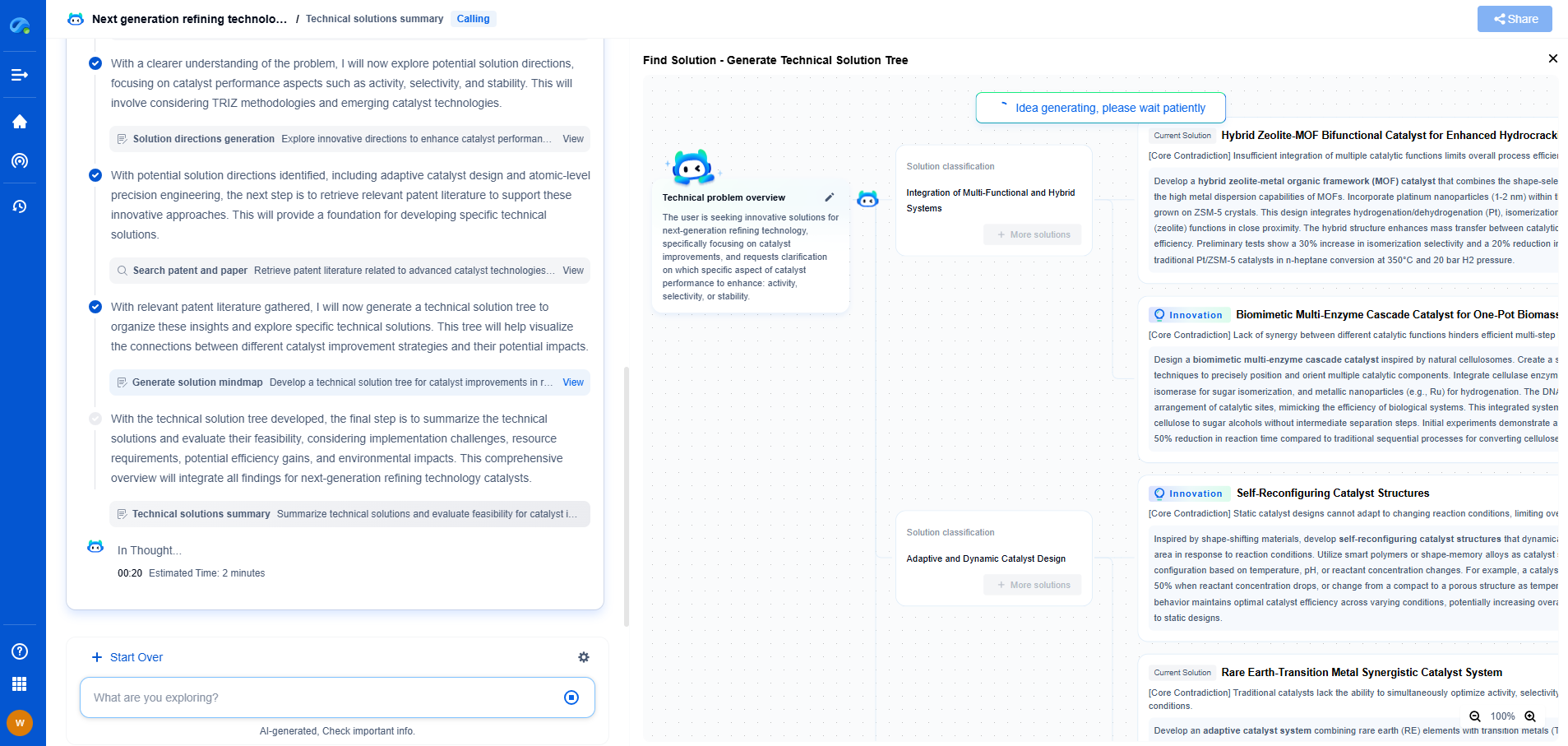

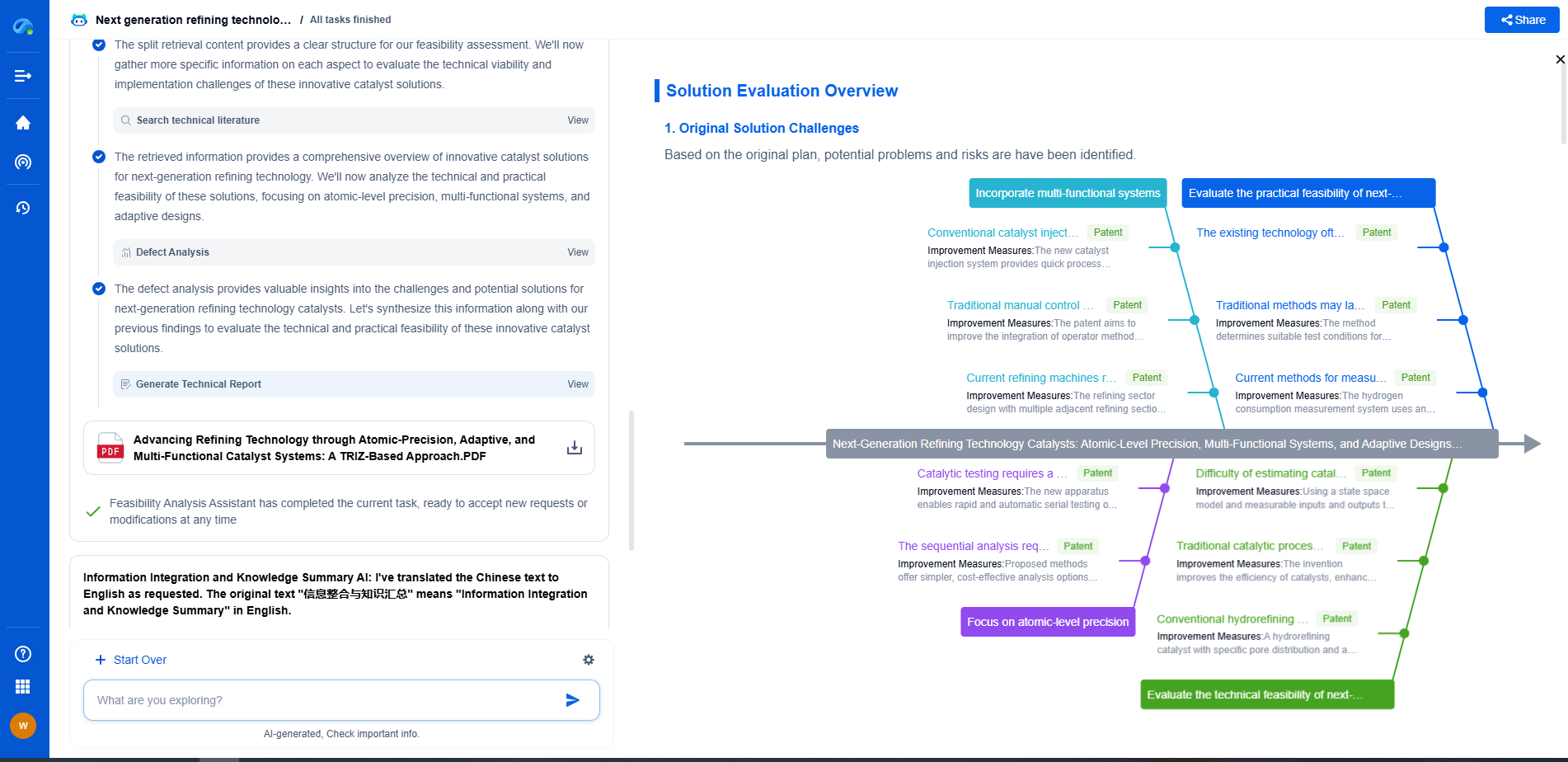

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

🧪 Let Eureka be your digital research assistant—streamlining your technical search across disciplines and giving you the clarity to lead confidently. Experience it today.