Wafer-Level Packaging vs. Traditional Wire Bonding for Capacitor Miniaturization

JUL 9, 2025 |

Understanding Wafer-Level Packaging

Wafer-level packaging (WLP) represents a progressive step forward in the miniaturization of electronic components, particularly capacitors. This approach involves packaging the entire silicon wafer first and then singulating it into individual components. As electronic devices continue to shrink, WLP has proven to be an effective means of reducing size while maintaining performance.

Unlike traditional methods, WLP allows for the addition of redistribution layers directly on the wafer, facilitating more connections and thus more functionality in a smaller area. This not only saves space but also improves the performance by reducing resistance and inductance paths that typically plague larger, more cumbersome packaging techniques.

Traditional Wire Bonding: An Established Technique

Wire bonding has been the backbone of semiconductor packaging for decades. This method involves using fine wires to connect the silicon chip to its package. It's a well-understood process that has been refined over the years to offer reliability and ease of manufacturing.

In the world of capacitor miniaturization, however, wire bonding presents some limitations. The most significant constraint is the physical space required for the wire loops, which can be a bottleneck in the pursuit of ever-smaller electronic components. Moreover, the inductances induced by these wire loops can become significant as the frequency of operation increases, potentially affecting the performance of high-speed or high-frequency applications.

Comparative Analysis: Size and Performance

When comparing WLP and traditional wire bonding, one of the most apparent differences is in size reduction. WLP eliminates the need for wire loops, which means capacitors can be packaged much closer to the chip die. This compactness is crucial as it directly correlates with the overall reduction in device size, a critical factor in mobile and wearable technology.

Moreover, WLP often results in a thinner profile, which complements the sleek designs of modern electronics. This size advantage not only enhances the aesthetic of finished products but also allows for more components to be packed into a given space, boosting functionality without compromising on design goals.

Performance-wise, WLP has a distinct advantage due to reduced parasitics like resistance, capacitance, and inductance. The direct wafer-level connections ensure that the signal integrity is maintained, which is especially vital in high-frequency applications. In contrast, traditional wire bonding, with its longer and more complicated connection paths, can introduce higher parasitic elements, potentially degrading performance.

Cost Considerations

Cost is always a consideration when choosing a packaging method. Traditional wire bonding is often seen as the more cost-effective option due to its established nature and less complex manufacturing requirements. However, as technology advances, the cost of WLP is becoming more competitive, especially when considering the performance and size benefits it offers.

The initial setup costs for WLP might be higher due to the specialized equipment and processes required. Nonetheless, the potential for high yields and the integration of multiple functionalities in a single package can offset these costs in large-scale production runs.

Future Outlook

The choice between wafer-level packaging and traditional wire bonding is becoming increasingly clear as the demand for smaller, more efficient electronic devices grows. WLP is setting new standards in miniaturization and performance, making it an attractive option for cutting-edge applications.

However, traditional wire bonding will likely continue to remain relevant, especially in applications where cost constraints are a significant factor or where the inherent design does not necessitate ultra-miniaturization.

As the electronics industry continues to evolve, the roles of both WLP and wire bonding will adapt, potentially leading to hybrid solutions that capitalize on the strengths of both methods. Staying informed about these advancements will be crucial for engineers and designers aiming to keep pace with the rapid progression of technology.

In conclusion, both wafer-level packaging and traditional wire bonding have their places in capacitor miniaturization. The decision between the two will depend on the specific needs of the application, weighing factors such as size, performance, cost, and future scalability.

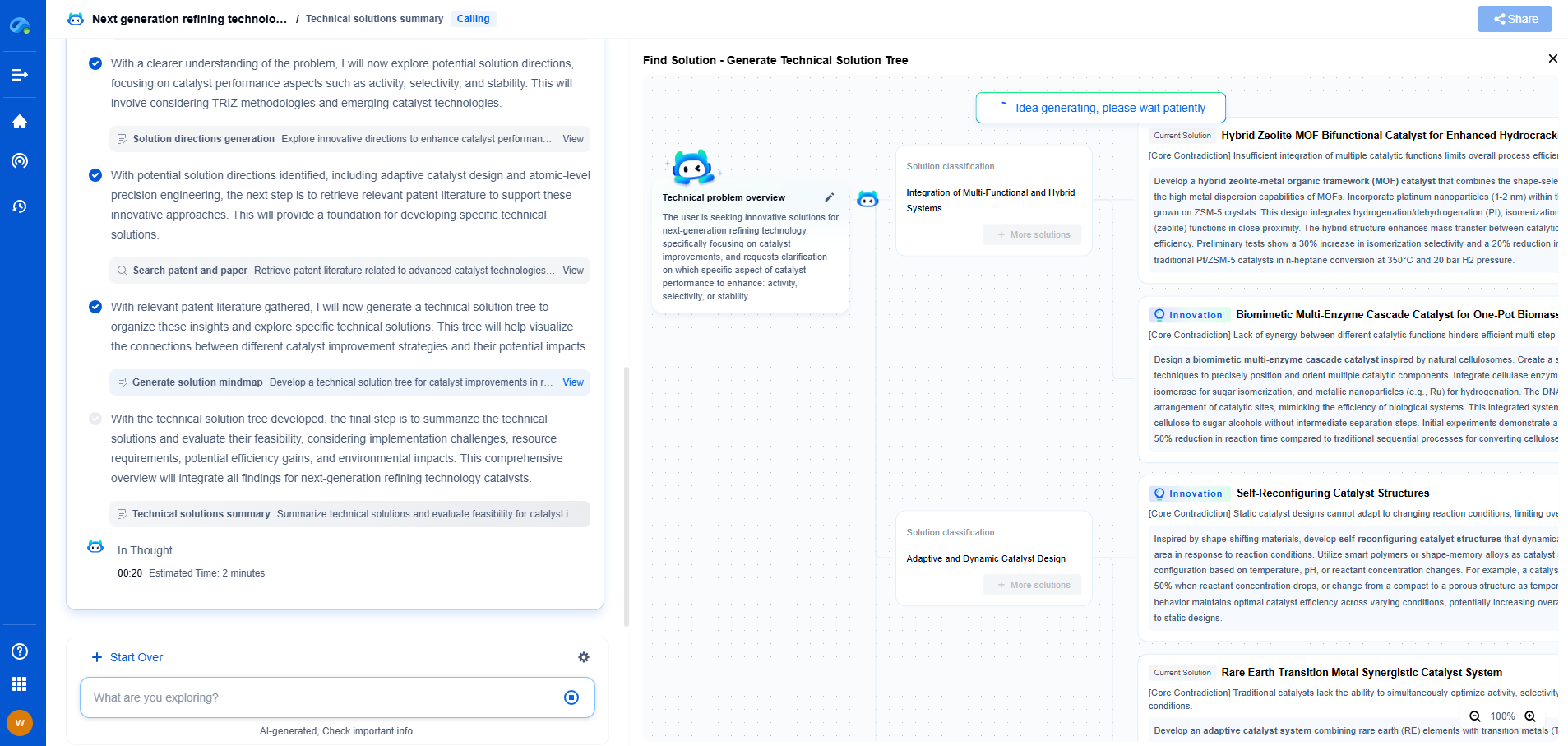

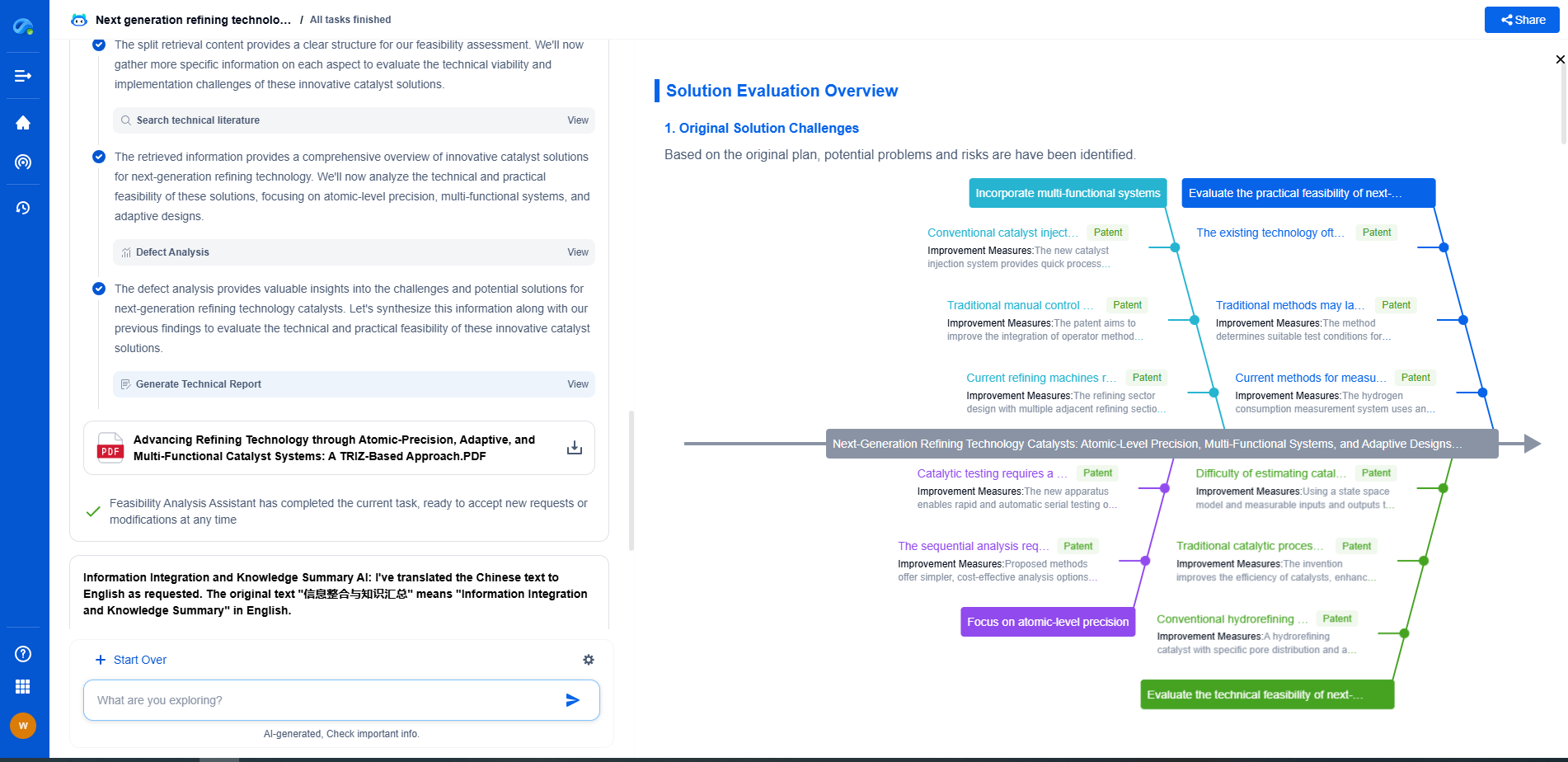

Looking to accelerate your capacitor innovation pipeline?

As capacitor technologies evolve—from miniaturized MLCCs for smartphones to grid-scale energy storage devices—so must the way your team accesses critical knowledge.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Try Patsnap Eureka now and discover a faster, smarter way to research and innovate in capacitor technology.