What Are JEDEC Packaging Standards? An Overview

JUN 27, 2025 |

The Joint Electron Device Engineering Council, commonly known as JEDEC, plays a crucial role in the semiconductor industry by setting standards that ensure the compatibility, reliability, and performance of electronic components. Among these, JEDEC packaging standards are essential for defining the mechanical and physical characteristics of semiconductor packages. These standards help in streamlining the manufacturing process, ensuring quality, and facilitating the integration of components across different devices and industries.

Understanding Semiconductor Packaging

Before delving into JEDEC's specific contributions, it's important to understand what semiconductor packaging entails. Semiconductor packaging refers to the process of enclosing integrated circuits (ICs) to protect them from physical damage and corrosion while facilitating electrical connections. Each package allows the IC to interface with the external environment and is critical for heat dissipation, performance, and durability.

Importance of JEDEC Packaging Standards

JEDEC packaging standards provide a framework for manufacturers to produce semiconductor components that are not only functional but also compatible with existing systems. These standards are vital for several reasons:

1. **Interoperability**: By adhering to JEDEC standards, different manufacturers can produce components that fit within a universal framework. This interoperability ensures that components from different sources can work together seamlessly.

2. **Quality Assurance**: JEDEC standards set benchmarks for quality, ensuring that semiconductor packages meet certain performance and durability criteria. This minimizes the risks of failure in critical applications.

3. **Cost Efficiency**: Standardization helps reduce manufacturing costs by allowing for mass production and reducing the need for custom components. It also simplifies the supply chain by reducing variation.

4. **Innovation Facilitation**: With clear standards in place, companies can focus on innovation rather than spending resources on developing proprietary packaging solutions. This accelerates technological advancement and encourages competitive development.

Key JEDEC Packaging Standards

JEDEC's catalog of standards is extensive, but here are a few key aspects related to packaging that are particularly noteworthy:

1. **Package Outline Dimensions**: JEDEC defines standard dimensions for various package types, such as Dual In-line Packages (DIP), Surface Mount Devices (SMD), and Chip Scale Packages (CSP). These dimensions ensure that the components fit correctly within a given space, facilitating design and assembly.

2. **Moisture Sensitivity Levels (MSL)**: JEDEC provides guidelines for classifying the moisture sensitivity of semiconductor packages. This classification is crucial for determining handling, storage, and shipping requirements to prevent moisture-induced defects.

3. **Thermal Characteristics**: Standards such as JESD51 provide methodologies for evaluating the thermal performance of packages, helping designers understand how packages will behave under different thermal conditions.

4. **Lead-Free Packaging**: In response to environmental concerns, JEDEC has developed standards that guide the industry in transitioning to lead-free packaging solutions, ensuring compliance with global environmental regulations.

The Role of JEDEC in Industry Collaboration

JEDEC's strength lies in its collaborative approach, bringing together industry experts, manufacturers, and academia to develop comprehensive standards. This collaboration ensures that standards are up-to-date with technological advancements and practical industry needs. JEDEC committees, which consist of representatives from major semiconductor companies, work tirelessly to address emerging challenges and trends, ensuring that the standards remain relevant and widely adopted.

Future Trends in JEDEC Packaging Standards

As technology evolves, so do the requirements for semiconductor packaging. The rise of IoT devices, artificial intelligence, and high-performance computing necessitates more advanced packaging solutions. JEDEC is actively working on standards that support the integration of 3D packaging, system-in-package (SiP) solutions, and advanced materials that enhance performance and efficiency.

Conclusion

JEDEC packaging standards play an indispensable role in the semiconductor industry by ensuring that components are reliable, compatible, and efficient. By providing a framework for standardization, JEDEC not only facilitates innovation but also contributes to cost-effective manufacturing and global interoperability. As the industry continues to evolve, JEDEC's commitment to developing relevant standards will be crucial in addressing future challenges and sustaining growth in the semiconductor sector.

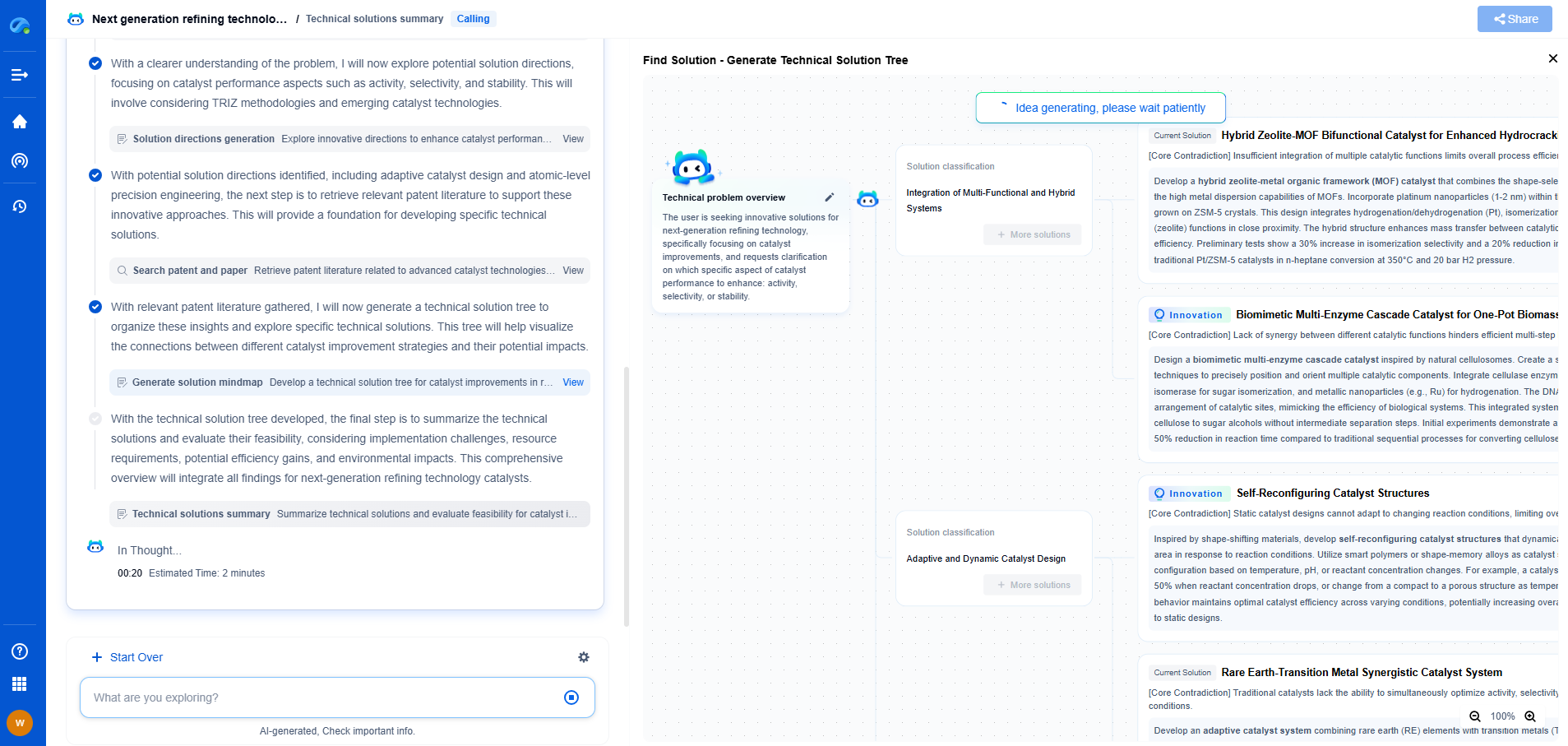

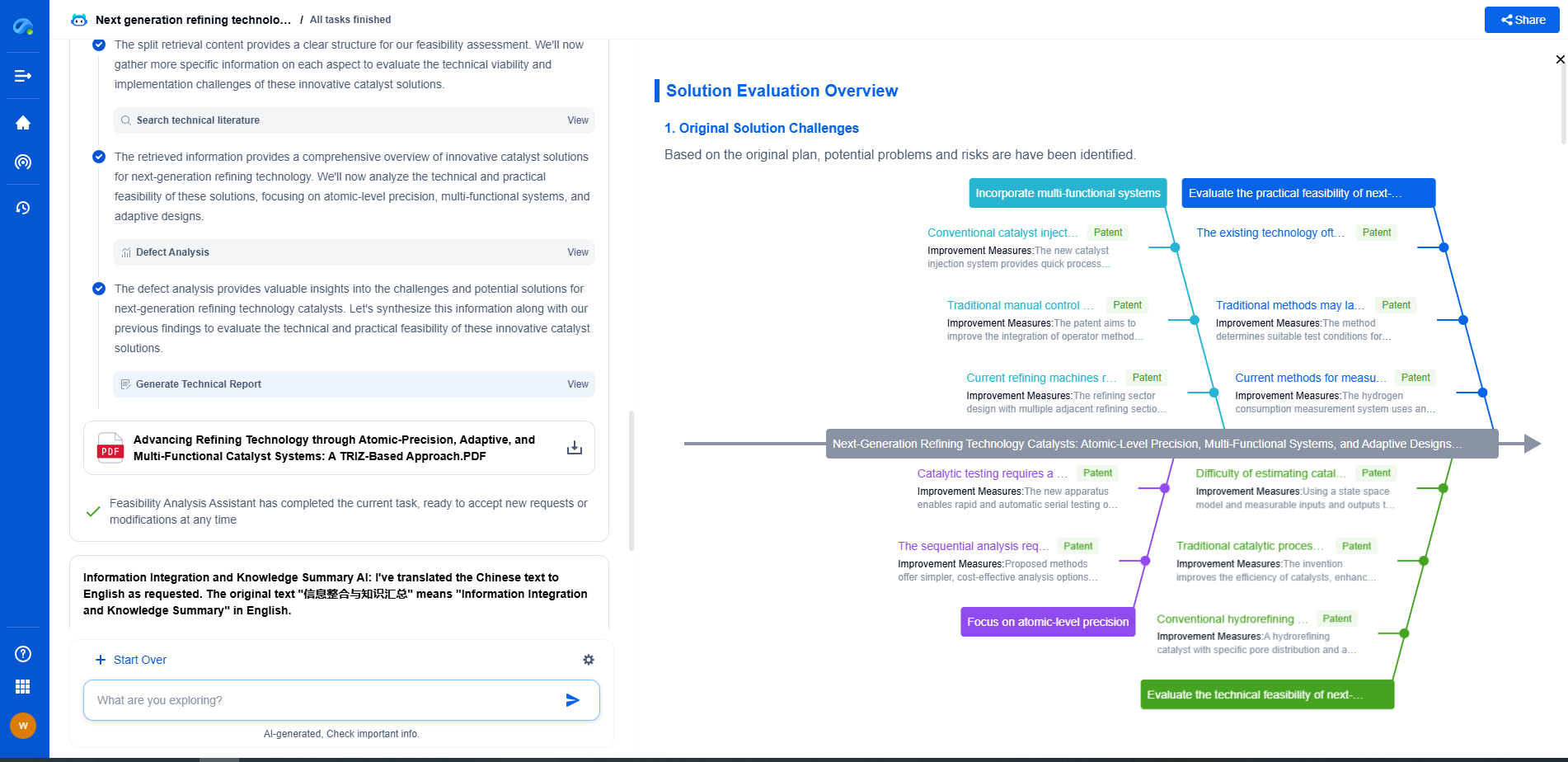

Empower Your Breakthroughs in Basic Electric Components with Patsnap Eureka

From resistors, capacitors, and inductors to fuses, connectors, superconductors, and nano-scale materials—basic electric elements may be the building blocks of modern electronics, but the innovation behind them is anything but simple. As device miniaturization accelerates and materials science pushes new frontiers, R&D and IP teams face increasing complexity in staying on top of technical advancements, patent activity, and competitive landscapes.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

🔧 Whether you’re optimizing energy storage, improving thermal resistance, or creating the next leap in circuit efficiency, Patsnap Eureka is your AI copilot for high-efficiency, high-precision R&D and IP strategy.

👉 Experience how Patsnap Eureka can revolutionize your R&D and IP strategy. Request a demo today and power up your next breakthrough.