When Your Delta-Sigma ADC Fails: Diagnosing Sampling and Filtering Errors

JUL 17, 2025 |

Delta-Sigma Analog-to-Digital Converters (ADCs) are renowned for their precision and versatility in converting analog signals into digital data. Widely used in audio applications, instrumentation, and communication systems, these converters excel at handling low-frequency signals with high accuracy. However, like any sophisticated technology, Delta-Sigma ADCs can encounter issues that compromise their performance. Understanding these potential pitfalls is crucial for diagnosing and correcting sampling and filtering errors when they arise.

Recognizing the Symptoms of ADC Failure

Before diving into diagnostic measures, it's important to identify the signs of ADC failure. Common symptoms include increased noise in the output, unexpected signal distortion, and erratic or unstable readings. Users might also notice latency issues or complete loss of signal. These symptoms often point to underlying problems in the sampling or filtering processes integral to Delta-Sigma ADC operation.

Understanding Sampling Errors

Sampling is a critical step in the ADC process, as it involves capturing analog signals at discrete intervals. Errors in sampling can significantly degrade the quality of the conversion. One prevalent issue is aliasing, which occurs when the sampling rate is insufficient to accurately represent the signal frequency. The Nyquist-Shannon theorem states that the sampling frequency must be at least twice the highest frequency component of the analog signal to prevent aliasing. Failure to adhere to this criterion results in an overlap of frequency components, generating incorrect signal representation.

Another potential sampling error is jitter, which is the variation in timing when sampling the analog signal. Jitter introduces phase noise and can lead to significant inaccuracies, especially in high-resolution applications. Diagnosing jitter typically involves scrutinizing the clock signals for consistency and stability.

Examining Filtering Errors

Delta-Sigma ADCs rely on both digital and analog filters to refine the conversion process. Inadequate or improperly configured filters can introduce errors that mimic or exacerbate sampling issues. For instance, insufficient anti-aliasing filtering can allow unwanted high-frequency components to enter the ADC, resulting in noisy or inaccurate outputs.

Digital filters, employed post-conversion, can also be a source of trouble. Incorrectly set filter parameters may lead to data loss or distortion. Ensuring that filters are well-matched to the application's bandwidth and response requirements is vital. Observing the ADC's response to known signals can reveal filtering discrepancies, which can then be corrected through parameter adjustments.

Troubleshooting Techniques

Diagnosing sampling and filtering errors requires a systematic approach. Begin by verifying the integrity of the clock signals and ensuring that the sampling rate meets or exceeds the Nyquist criterion. Utilizing an oscilloscope or logic analyzer can help visualize timing issues or jitter, providing insight into potential sources of error.

Next, examine filter configurations. Check the specifications of any anti-aliasing filters and confirm they align with the signal bandwidth. Similarly, review digital filter settings within the ADC to ensure they are optimized for the target application. Adjusting these settings may resolve or significantly reduce error rates.

If problems persist, consider environmental factors such as electromagnetic interference, which can affect ADC performance. Shielding the ADC and its associated circuitry, along with ensuring clean, stable power supply connections, can mitigate such issues.

Best Practices for Reliable ADC Operation

To prevent sampling and filtering errors from occurring in the first place, adhere to several best practices. Ensure that your design incorporates adequate anti-aliasing filters and that the chosen ADC is appropriate for the signal types and frequencies involved. Maintain a clean and stable clock source to minimize jitter and other timing-related errors. Regularly test and calibrate your ADC system to ensure ongoing accuracy and reliability.

Conclusion: Maintaining ADC Performance

While Delta-Sigma ADCs offer exceptional accuracy and performance, they are not immune to errors. By understanding the intricacies of sampling and filtering operations and employing careful diagnostic and maintenance strategies, you can effectively troubleshoot and resolve issues as they arise. Ultimately, a proactive approach to design and maintenance will help ensure that your Delta-Sigma ADC system consistently delivers optimal performance.

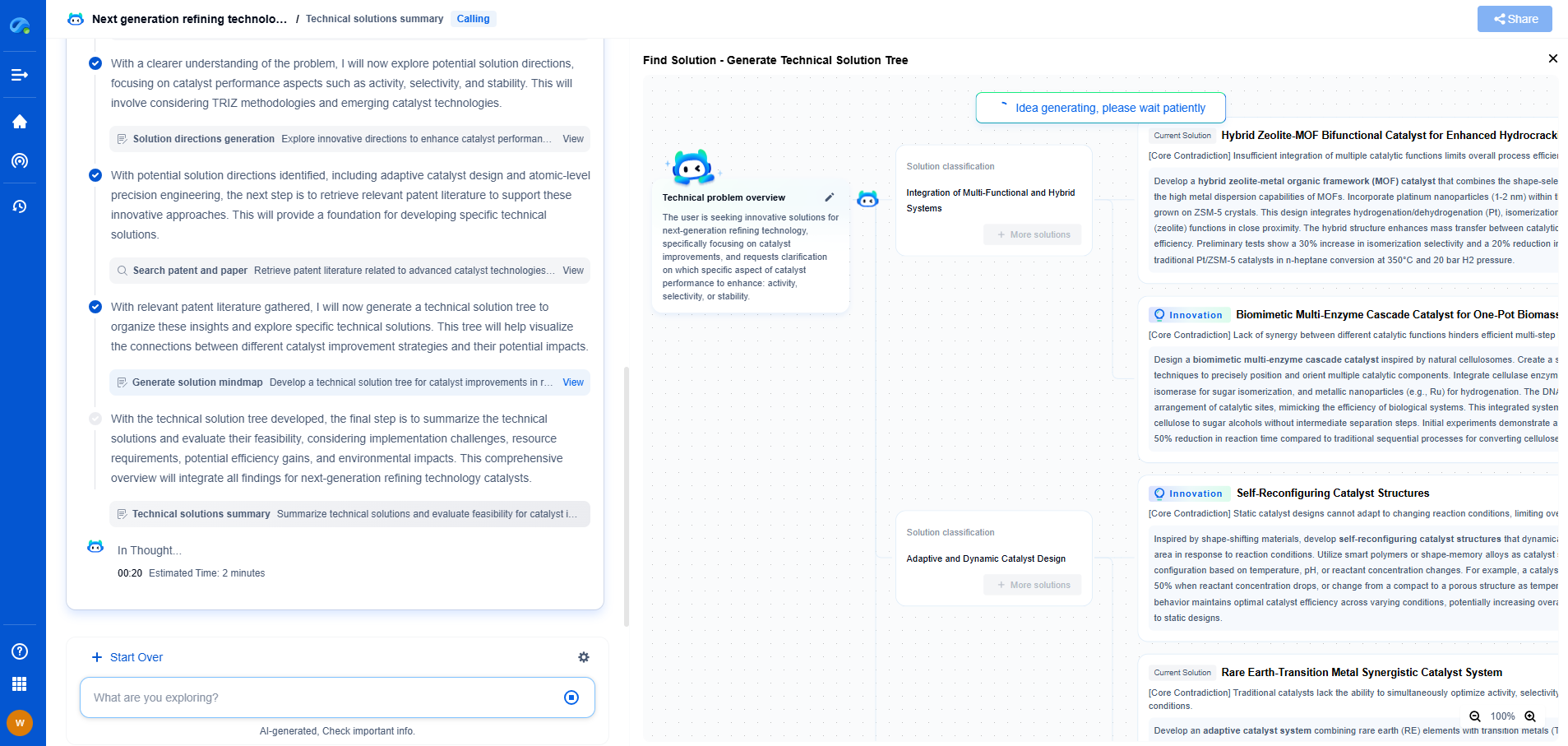

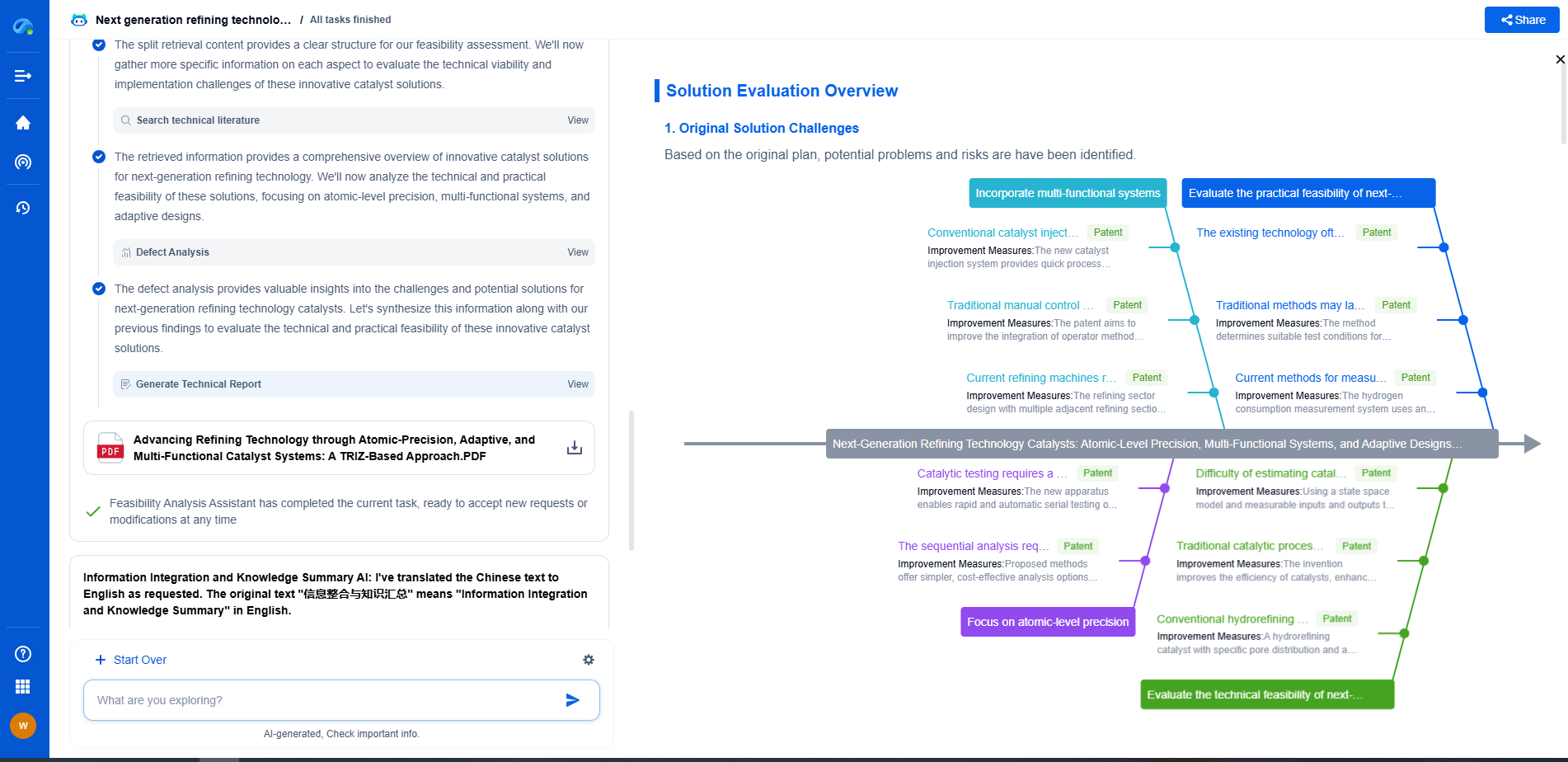

Whether you’re developing multifunctional DAQ platforms, programmable calibration benches, or integrated sensor measurement suites, the ability to track emerging patents, understand competitor strategies, and uncover untapped technology spaces is critical.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

🧪 Let Eureka be your digital research assistant—streamlining your technical search across disciplines and giving you the clarity to lead confidently. Experience it today.