What is a D Flip-Flop?

A D Flip-Flop is a fundamental storage element in digital electronics that is used to store a binary state (0 or 1) and preserve it until it is explicitly changed. It is a type of sequential logic circuit that plays a crucial role in the design of digital systems, including counters, shift registers, and digital clocks.

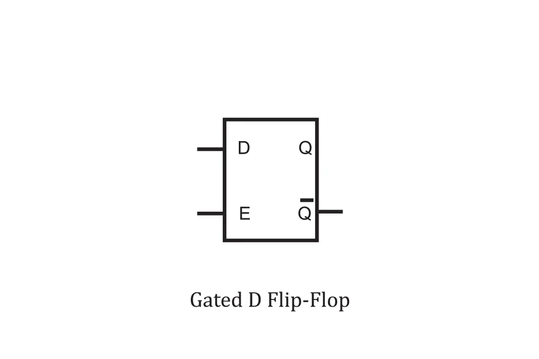

How Does a D Flip-Flop Work?

The D flip-flop functions by capturing the state of the input (D) at the rising edge of the clock signal (CK). The output (Q) updates to match the input only during the clock’s low-to-high transition. While the clock remains high, the output stays stable, unaffected by input changes.

The key components of a D flip-flop include

- Input Stage: Receives the data (D) to be stored.

- Output Stage: Provides the output (Q) based on the stored data.

- Clock Signal: Triggers the update of the output at the rising edge.

The operation following steps

- The clock signal (CK) transitions from low to high.

- The current state of the input (D) is captured and stored.

- The output (Q) is updated to reflect the new state of the input.

Key Characteristics of a D Flip-Flop

- Storage Element: The primary function of a D Flip-Flop is to store the state of the input signal (D) at the rising or falling edge of a clock signal. This stored state is then available at the output (Q) after one clock cycle.

- Edge Triggering: Unlike level-triggered latches, D flip-flops capture input changes only at the clock edge. This ensures a stable output unaffected by input fluctuations during the rest of the clock cycle.

- Stability: The output of a D Flip-Flop is stable and retains its value between clock cycles, making it suitable for applications requiring predictable and reliable data storage.

Types of D Flip-Flops

- Master-Slave D Flip-Flop: This is a common implementation that uses two flip-flops (master and slave) to ensure that the output is stable and changes only at the clock edge.

- TSPC (True Single-Phase Clock) D Flip-Flop: This type minimizes function failure by slowing down voltage changes between stages using resistive elements.

- Differential D Flip-Flop: This type uses both the true and complement signals of the input, providing balanced transmission and potentially lower latency.

- Dynamic D Flip-Flop: Stores data as a charge in a capacitor, requiring periodic refresh to overcome leakage currents.

Truth Table of a D Flip-Flop

| Clock (CLK) | D Input | Q Output |

|---|---|---|

| Rising/Falling | 0 | 0 |

| Rising/Falling | 1 | 1 |

| Steady | X | Previous Q |

Circuit Design of a D Flip-Flop

Designing a D flip-flop involves creating a circuit that can store and transfer data reliably. Various techniques can be employed to optimize the design for power efficiency, speed, and area:

- CMOS Technology: CMOS flip-flops dominate modern applications due to their low power requirements and high noise immunity, making them efficient and reliable.

- Low Power Techniques: Innovative methods like adiabatic logic, partial signaling, and current-mode signaling minimize power consumption in flip-flop circuits.

- Advanced Materials: Emerging technologies, including single-electron devices, enable the creation of flip-flops with exceptional speed and minimal power dissipation.

- Layout Optimization: Efficient layout design using techniques like MTCMOS (Multi-Threshold CMOS) can further reduce power consumption and improve performance.

Advantages of D Flip-Flops

Memory Element

- D flip-flops act as basic memory elements, capable of storing a bit of information. They have two stable states, typically represented as logic 0 and logic.

Simpllicity and Versatility

- The structure of a D flip-flop is relatively simple, consisting of a few basic components like switches and a level shifter. This simplicity allows for versatility in design and integration into complex digital circuits.

Clock-Driven Operation

- The operation of a D flip-flop is synchronized with a clock signal, which ensures that data is captured and stored at precise intervals. This clock-driven mechanism helps in maintaining data integrity and synchronicity within the system.

Reduced Power Consumption

- Various designs of D flip-flops have been developed to minimize power consumption. For instance, reduced dynamic power flip-flops selectively disable charging/discharging operations to minimize capacitance, thereby reducing power usage.

Use in Secure Applications

- D flip-flops find applications in hardware security, particularly in Physically Unclonable Functions (PUFs). Their random startup values serve as a source of entropy, enabling the generation of unique secret keys for cryptographic operations. This makes them essential for creating secure and tamper-proof hardware systems.

Scalability and Integration

- D flip-flops can be easily integrated into large-scale integrated circuits (ASICs) and are scalable for use in various applications, from small portable devices to large-scale computing systems.

Challenges and Limitations

Power Consumption

- One of the significant challenges with D flip-flops is their power consumption, particularly in portable and battery-operated devices. To address this, designers have developed low-power flip-flop designs, such as those using MTCMOS and output control techniques, which can reduce power consumption by up to 53% without compromising delay time.

Noise Sensitivity

- Dynamic circuits, which include D flip-flops, can be susceptible to noise, especially in deep submicron technologies. To enhance noise tolerance, techniques such as reducing switching activity in internal nodes can be employed, leading to a significant reduction in power dissipation.

Process Variations

- Variations in manufacturing processes can affect the performance and reliability of D flip-flops. To mitigate this, designs that emphasize high regularity, such as the PowerPC 603 and Minority3-based flip-flops, can be implemented to improve robustness against process variations.

Performance Trade-offs

- There are often trade-offs between power consumption, speed, and area in D flip-flop designs. For example, while FinFET-based designs can significantly reduce the power-delay product (PDP) by 87%-92.6%, they might require additional design considerations to optimize area utilization.

Applications of D Flip-Flop

Digital Systems and Computing

- Central Processing Units (CPUs): D Flip-Flops manage data storage and transfer between processor stages, ensuring stable system states and proper data flow.

- Memory Systems: D Flip-Flops store binary data in memory circuits, facilitating data management in RAM and ROM for storage and retrieval operations.

Control Systems

- Sequential Logic Circuits: D Flip-Flops are essential for managing operation sequences in control systems, enabling counters, timers, and sequential control functions.

- Microcontrollers: D Flip-Flops handle timing and sequencing in microcontrollers, allowing efficient execution of complex tasks.

Communication Systems

- Data Transmission: D Flip-Flops are vital in shift registers for serial-to-parallel and parallel-to-serial data conversion, enabling efficient communication.

- Synchronization: They ensure accurate data transmission and reception by maintaining synchronization within communication systems.

Portable and Low-Power Applications

- Ultra-Low Power Design: Recent advancements have focused on optimizing D Flip-Flop designs for low-power applications. For instance, a modified SET (Single Edge Triggered) D Flip-Flop design has been optimized for portable applications, consuming less power and area while maintaining functionality. This design is suitable for applications requiring ultra-low power consumption and medium frequency operation.

Other Applications

- Digital Clocks and Timers: D Flip-Flops enable precise timing in digital clocks and timers by maintaining stable and accurate state transitions.

- Finite State Machines: D Flip-Flops implement finite state machines, essential for applications like robotics, automation, and embedded systems, ensuring reliable state progression.

Latest Technical Innovations in D Flip-Flop

Single-Electron Technology

- A D Flip-Flop designed using single-electron technology has been demonstrated to offer low power dissipation and high-speed performance. This technology leverages the manipulation of individual electrons, which can lead to significant improvements in device scalability and energy efficiency.

Multi-Threshold CMOS (MTCMOS) Technique

- The MTCMOS technique involves using a short pulse train as a clock signal, which results in a True Single Phase Clocking (TSPC) flip-flop. This method aims to reduce power consumption while maintaining high speed and noise margin. The design process utilizes Tanner EDA software for verification2.

Gate Diffusion Input (GDI) Technique

- The GDI (Gate Diffusion Input) technique reduces power dissipation in D Flip-Flops by employing gate clocking methodologies. It achieves an additional 1.38% power optimization over already refined designs. GDI is preferred due to its low power-delay product, offering enhanced efficiency compared to other CMOS configurations.

Adiabatic Design

- A quaternary adiabatic dynamic D Flip-Flop design has been proposed, utilizing multi-threshold metal oxide semiconductor (MOS) control and switch-signal theory. This design achieves significant energy savings, with simulations showing a 90% reduction in energy consumption at a frequency of 55.6 MHz compared to conventional CMOS designs.

Dynamic D Flip-Flop Designs

- Recent patents have focused on dynamic D Flip-Flop designs that reduce chip area, power consumption, and logic delay. These designs typically include latch units and output driving mechanisms that allow the flip-flop to operate in high level, low level, and high impedance states under a single clock signal control.

To get detailed scientific explanations of d flip flops, try Patsnap Eureka.

Learn more

Multiplexor: Efficient Data Selector for Electronics

Understanding STP Cable: Shielded Twisted Pair Explained

Understanding Twisted Pair Cable: Basics, Benefits, and Uses