Method for improving unevenness of polishing and method for preparing embedded copper metal layer

A copper metal, embedded technology, applied in chemical instruments and methods, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of slow removal of copper oxide layer, inability to be completely removed, prolonged grinding time of semiconductor wafers, etc., to achieve The effect of reducing polishing unevenness, improving product competitiveness, and improving process excellent rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

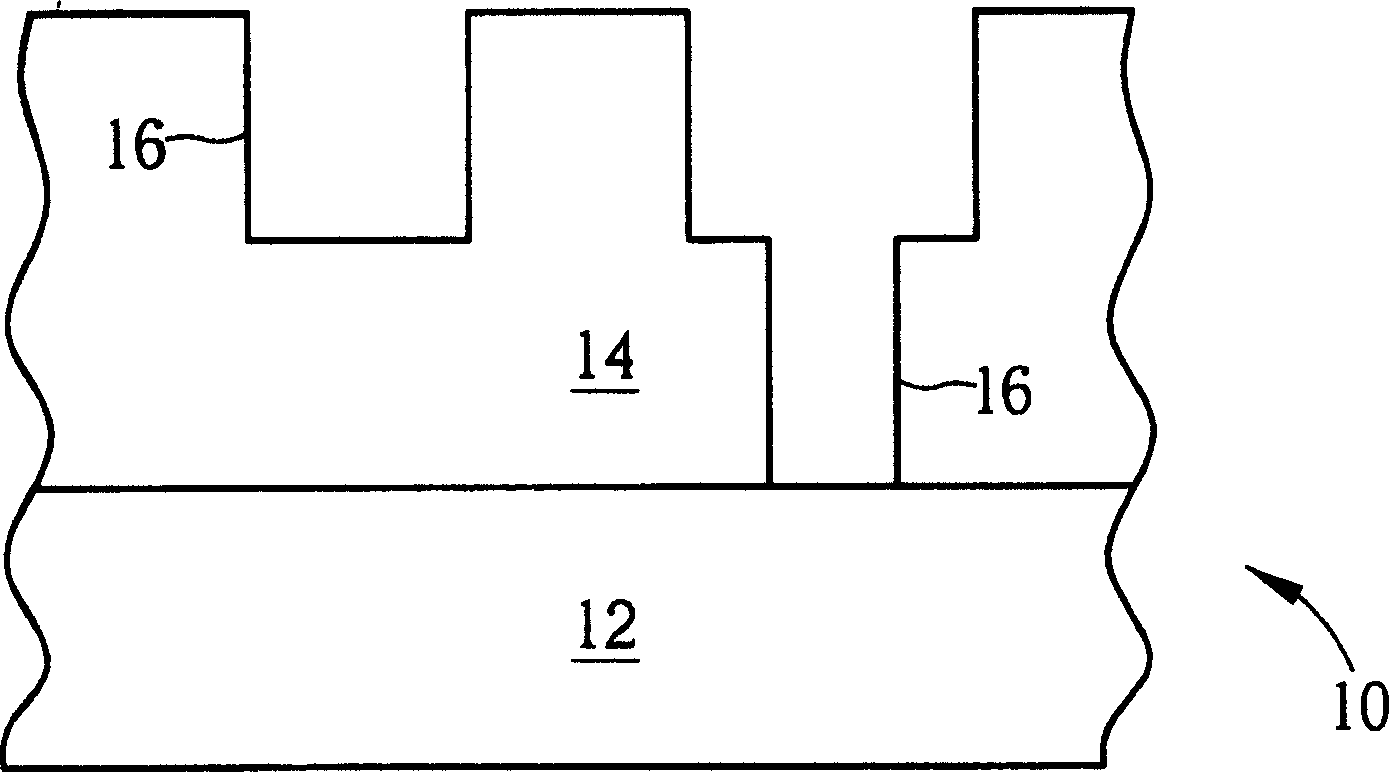

[0017] see Figure 1 to Figure 4 , Figure 1 to Figure 4 It is a schematic diagram of the method for fabricating an embedded copper metal layer on a semiconductor wafer 10 according to the present invention. Such as figure 1 As shown, the semiconductor wafer 10 includes a substrate 12 , a dielectric layer 14 disposed on the surface of the substrate 12 , and a plurality of embedded structures 16 disposed in the dielectric layer 14 . The embedded structure 16 can be designed as a single damascene (single damascene) structure or a dual damascene (dual damascene) structure according to product requirements, and wherein at least one embedded structure 16 penetrates the dielectric layer 14 to be electrically connected downward to the substrate. Conductive regions (not shown) in 12, such as other metal layers or parts of transistors.

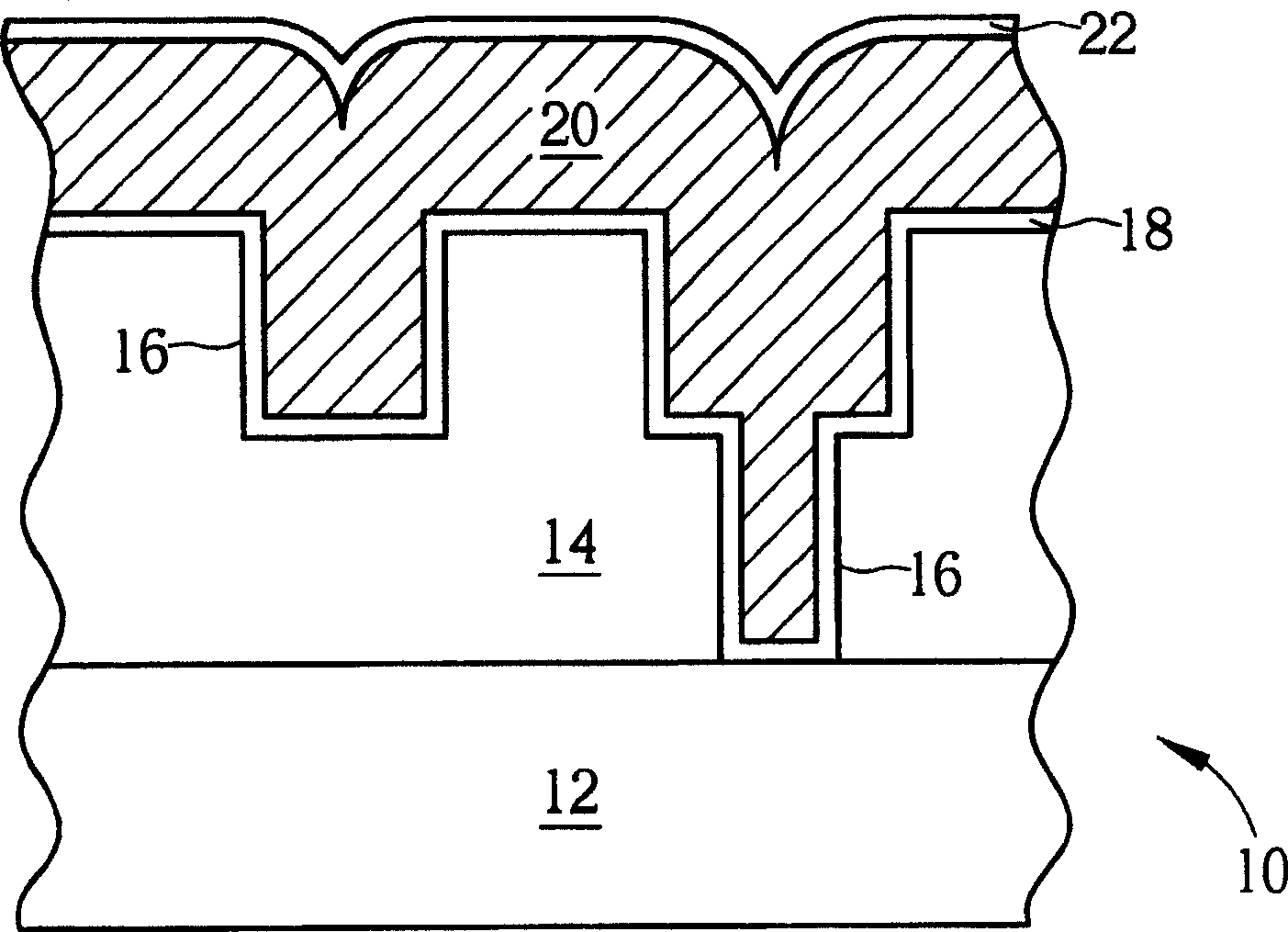

[0018] Such as figure 2 As shown, next, a barrier layer 18 is formed on the surface of the semiconductor wafer 10 . The barrier layer 18 uniforml...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com