Method and structure for reducing floating body effects in mosfet devices

A device and active device technology, applied in the field of semiconductor device processing, can solve problems such as low speed, reduced switching current, and increased thermal power

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

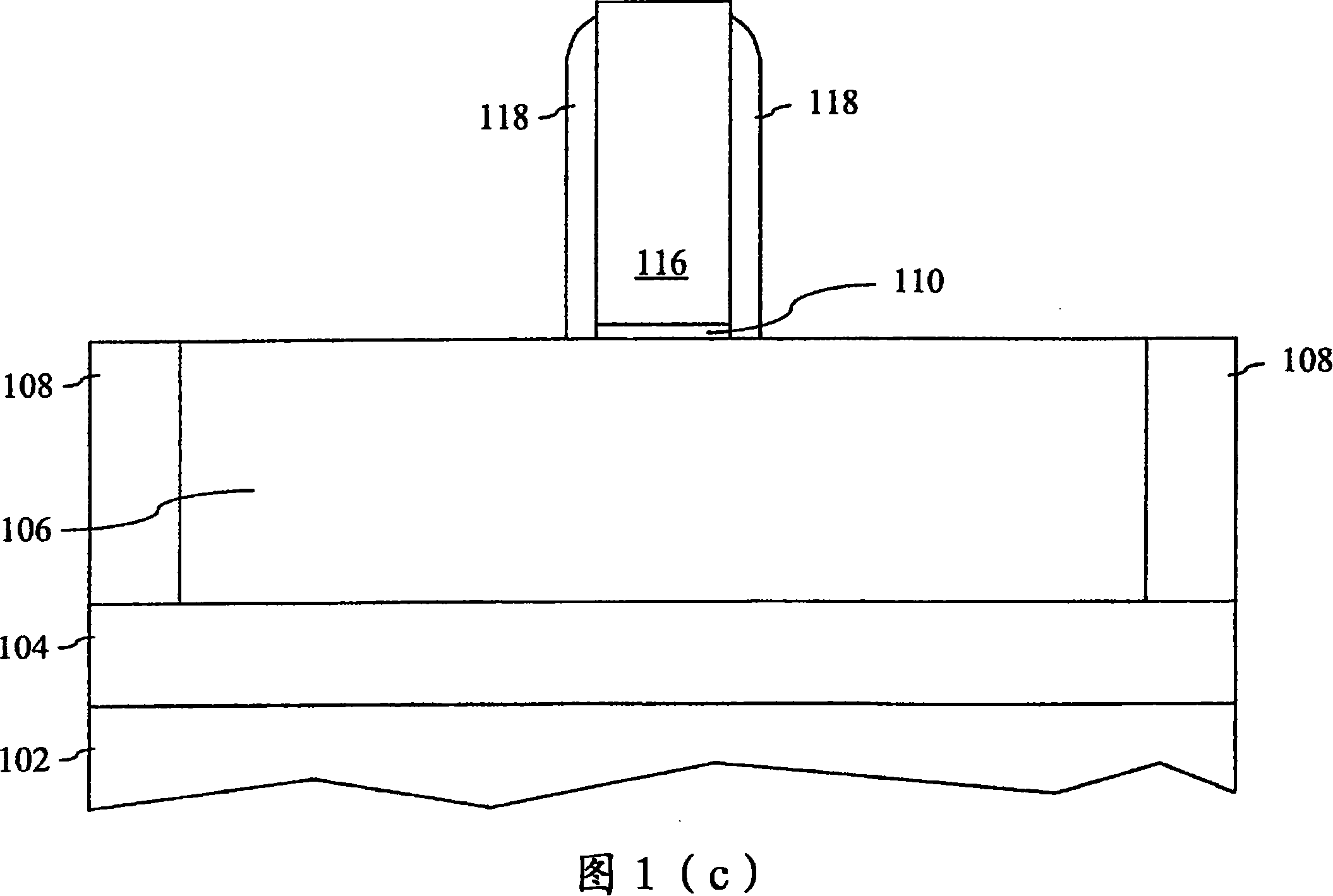

[0014] Disclosed herein is a method and structure for reducing floating body effects in MOSFET devices, including silicon-on-insulator (SOI) type devices, without junction leakage. Briefly stated, embodiments disclosed herein provide a metal plug formed through the source region of a transistor device such that the plug extends into the body of the transistor and provides a short circuit between the source and the bulk.

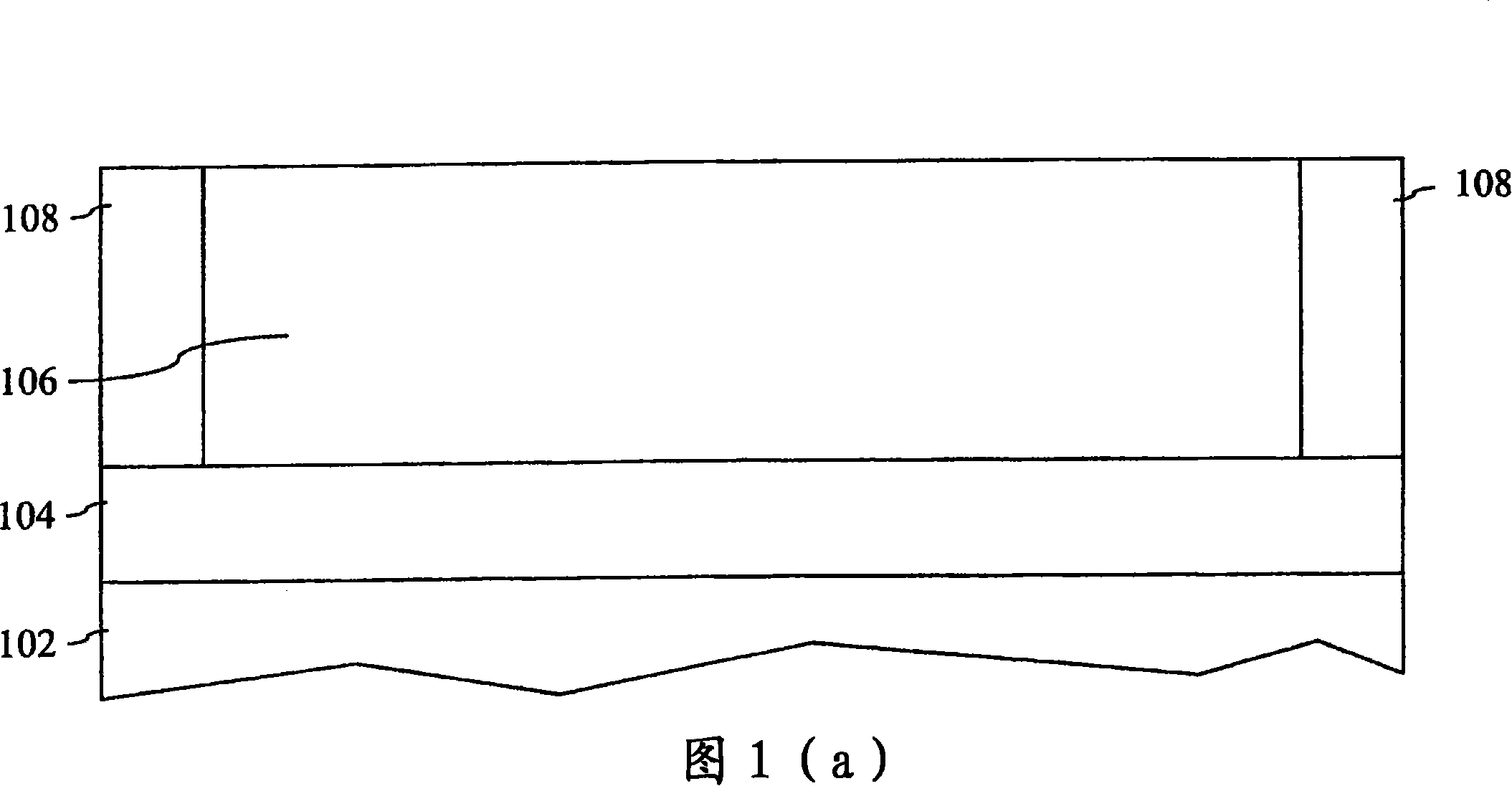

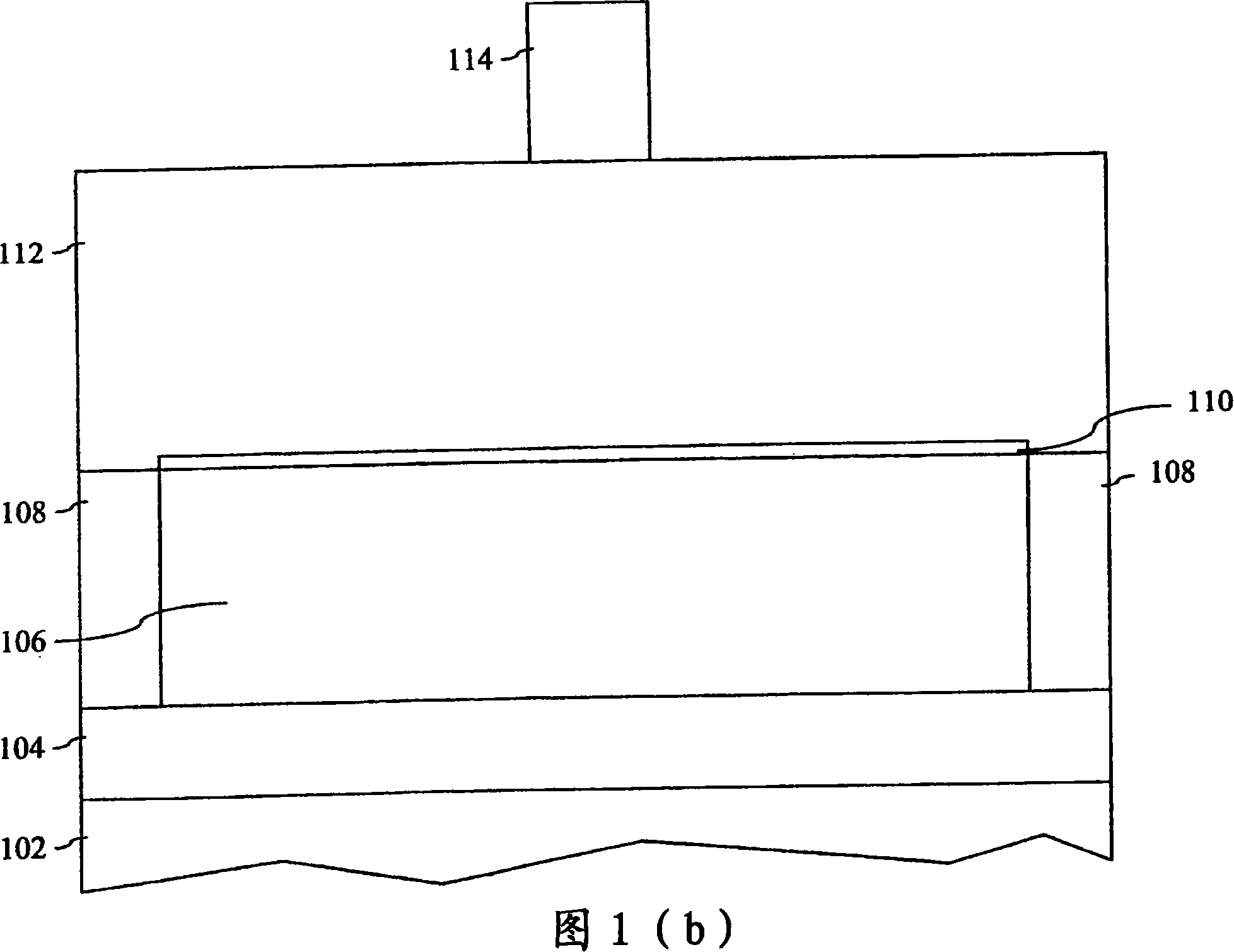

[0015] Reference is initially made to FIGS. 1( a ) through 1 ( k ), which illustrate a series of methods and structures for reducing floating body effects in silicon-on-insulator (SOI) transistor devices according to embodiments of the present invention. Section view. As shown in FIG. 1( a ), a bulk silicon layer 102 has a buried insulator (eg, oxide) layer (BOX) 104 formed thereon. A layer of crystalline silicon 106 is then formed over the BOX layer 104; thus, the term silicon-on-insulator (SOI) is also used to describe layer 106 in which active transistor ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com