Peripheral unit interconnection high speed bus interface and switchboard port testing method and system

A technology for external device interconnection and high-speed bus interface, applied in transmission systems, digital transmission systems, data exchange networks, etc., can solve the problem of limited CPU computing power, failure to measure the reliability and stability of PCIe interfaces, and data flow that cannot reach its limit Issues such as the maximum bandwidth to reduce costs and overcome the CPU computing speed limit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

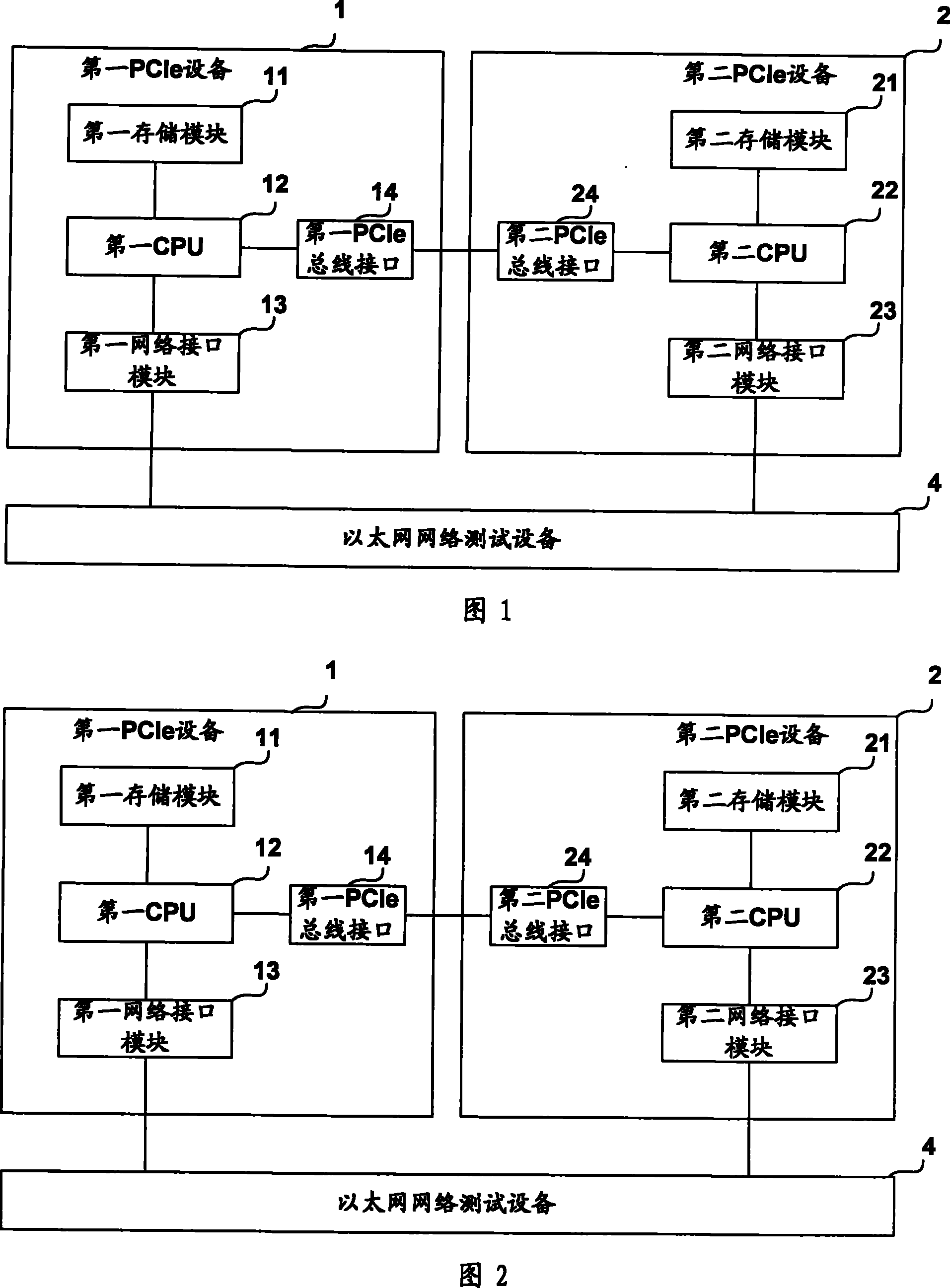

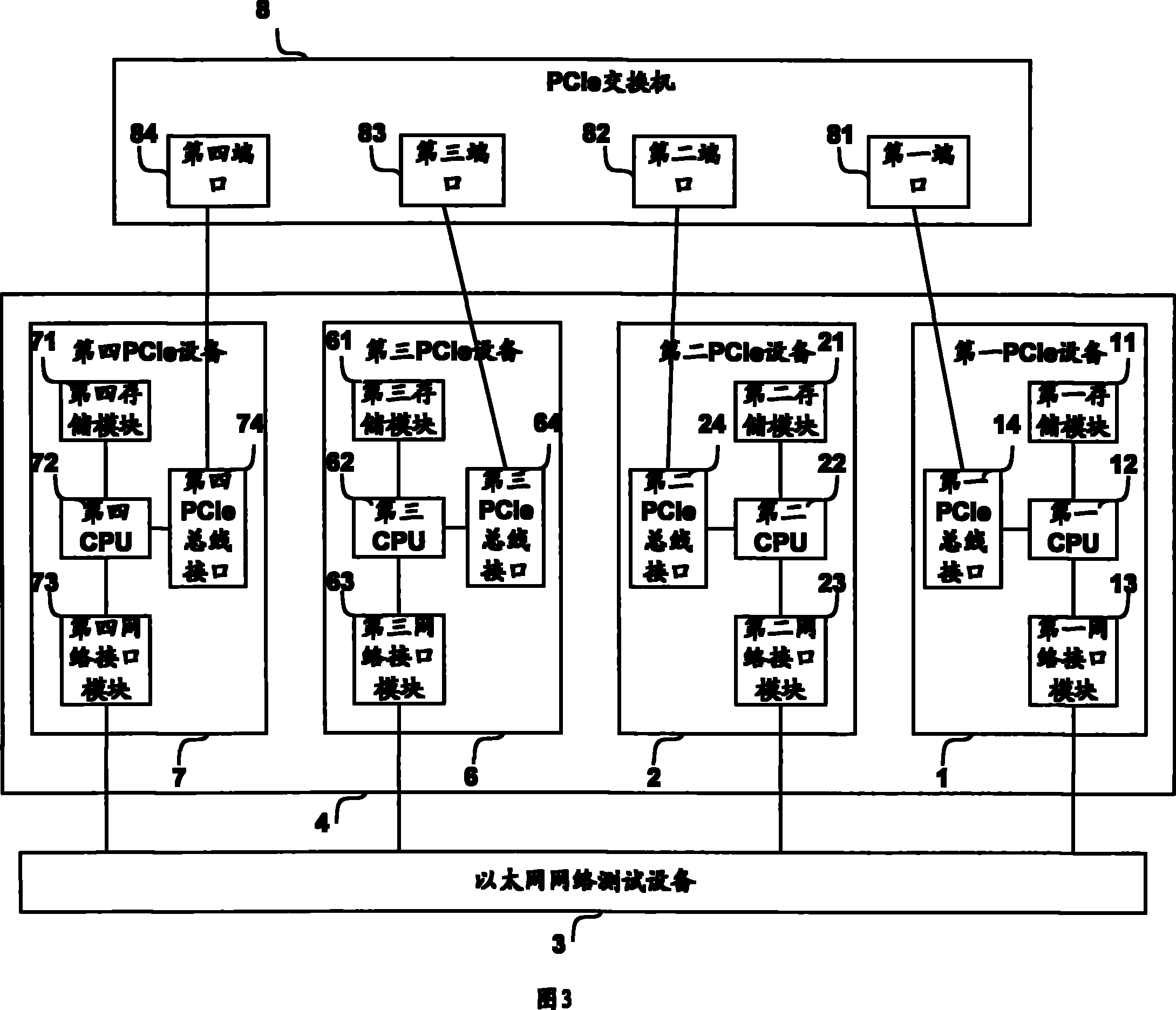

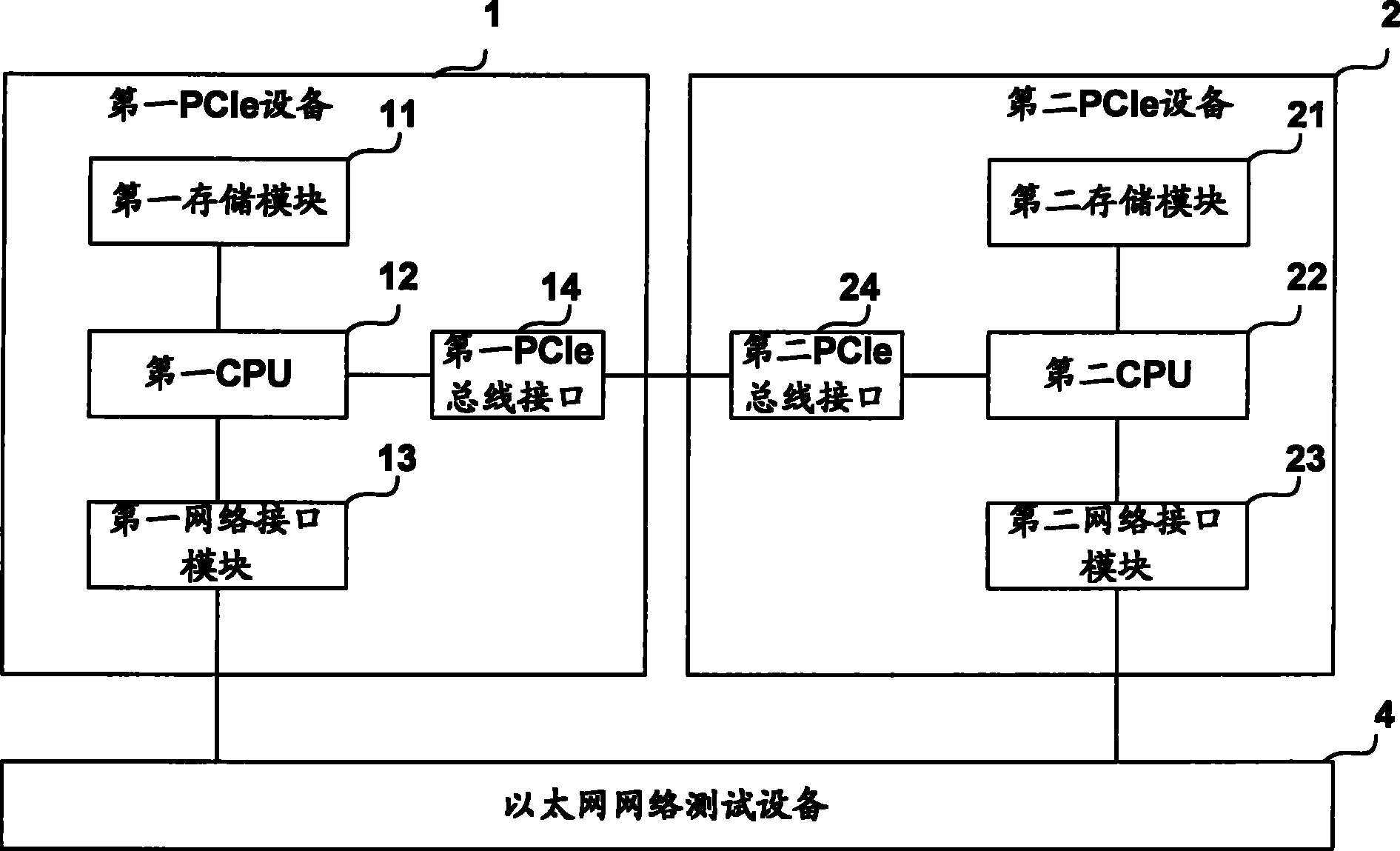

[0053] The structure of PCIe equipment among the present invention is: at least comprise CPU, and CPU has multiple Gigabit ports, all have at least 4 Gigabit ports as MPC8548, MPC8572, MPC8641 etc. of Freescale (Freescale), also include at least A PCIe interface.

[0054] The test of the PCIe bus interface involved in the present invention includes bandwidth test and performance test of the PCIe bus interface. The bandwidth test specifically refers to the maximum bandwidth that can be achieved by one-way write operations, one-way read operations, two-way write operations, and two-way read operations on the PCIe interface. The performance test specifically includes the stability and reliability test of the data transmitted on the PCIe interface. When the bidirectional read and write operations on the PCIe bus interface reach the maximum bandwidth, test whether there is packet loss and error phenomenon on the PCIe bus interface.

[0055] like figure 1 Shown is the schematic di...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com