Method for managing chip verification test cases

A test case, verification test technology, applied in software testing/debugging, electrical digital data processing, special data processing applications, etc., can solve problems such as large labor costs, and achieve the effect of reducing labor costs, ensuring completeness, and improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

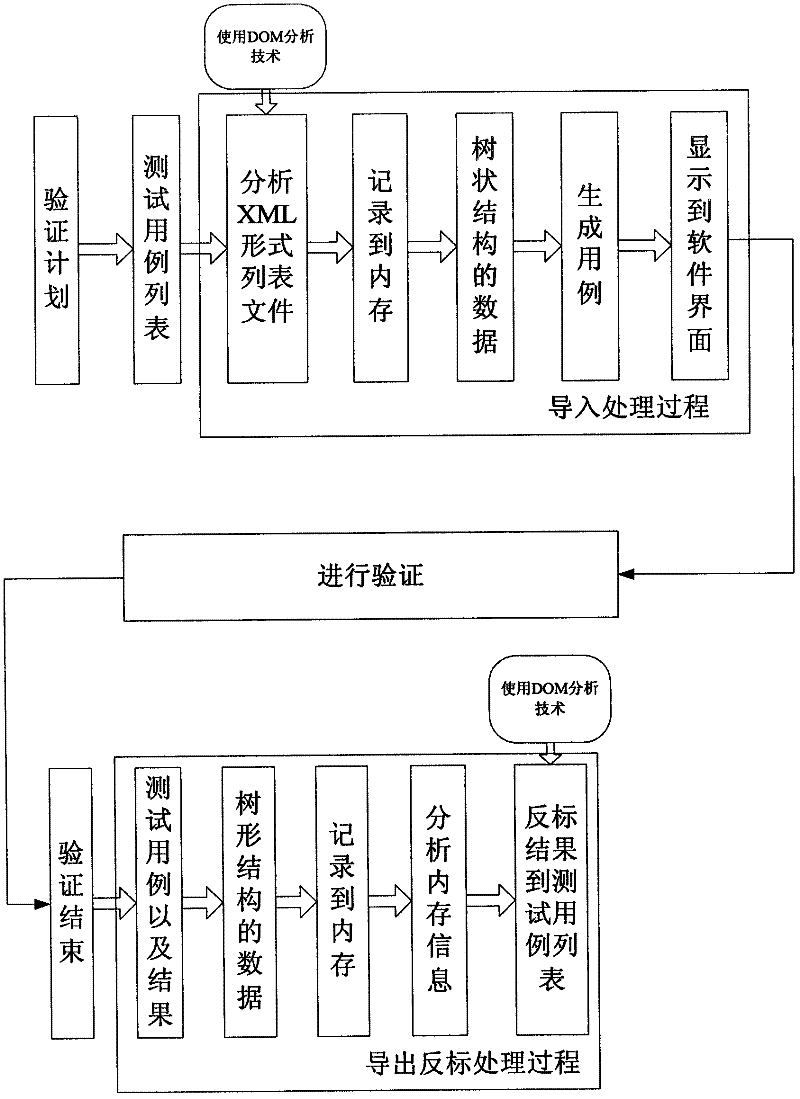

[0031] The present invention provides a management method of chip verification test cases, which can automatically complete the input of test cases and the reverse mark output of verification results, reduce the time for testers to check test cases during the test process, and greatly improve the efficiency of chip verification , and avoid the situation that is prone to omissions when manually constructing use cases, effectively ensuring the completeness of chip verification.

[0032] The chip verification test case management method provided by the present invention includes two steps of test case import and back-label output. The present invention will be described in detail below in conjunction with the accompanying drawings.

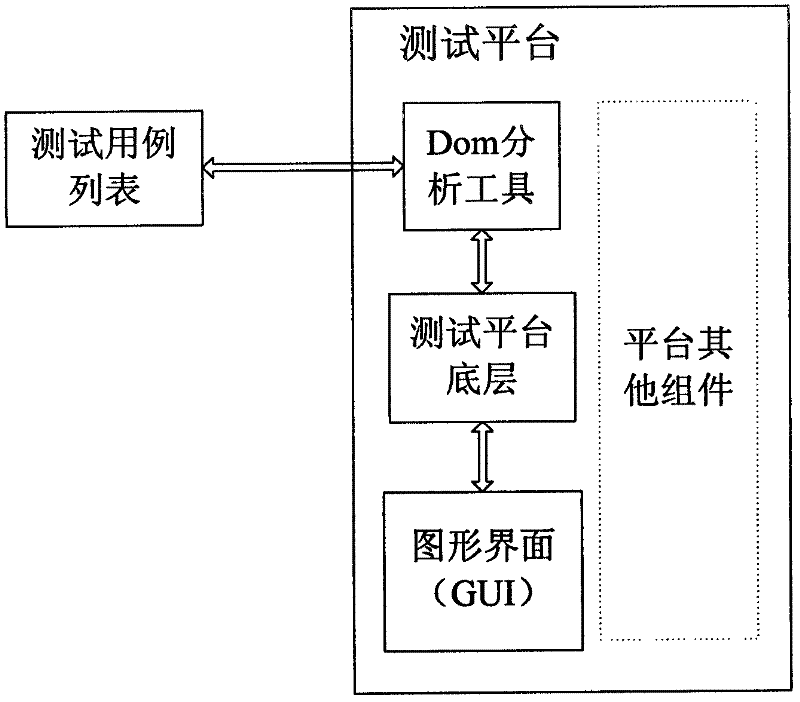

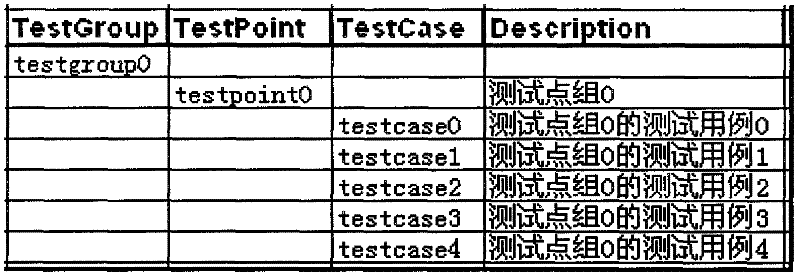

[0033] Import and export systems such as figure 1 As shown, it includes a Dom (Document Object Model) analysis tool, a component that interacts with the bottom layer of the test system platform, and a GUI graphical interface. The Dom analysis tool r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com