Signal sampling caching device used for field programmable gata array (FPGA) chip debugging

A signal sampling and caching technology, which is applied in memory systems, faulty computer hardware detection, memory address/allocation/relocation, etc., can solve problems such as limited storage depth, debugging logic insertion, and unsatisfactory timing, and achieve signal sampling The effect of large time span, high storage space utilization, and strong multi-signal sampling capability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

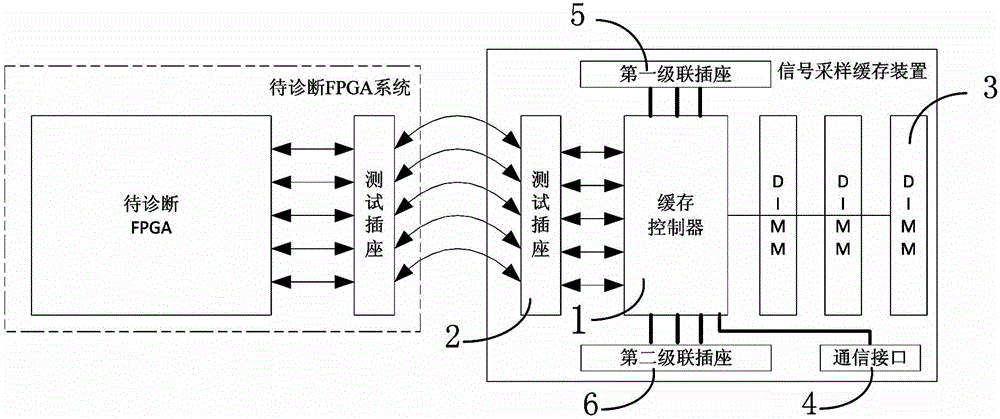

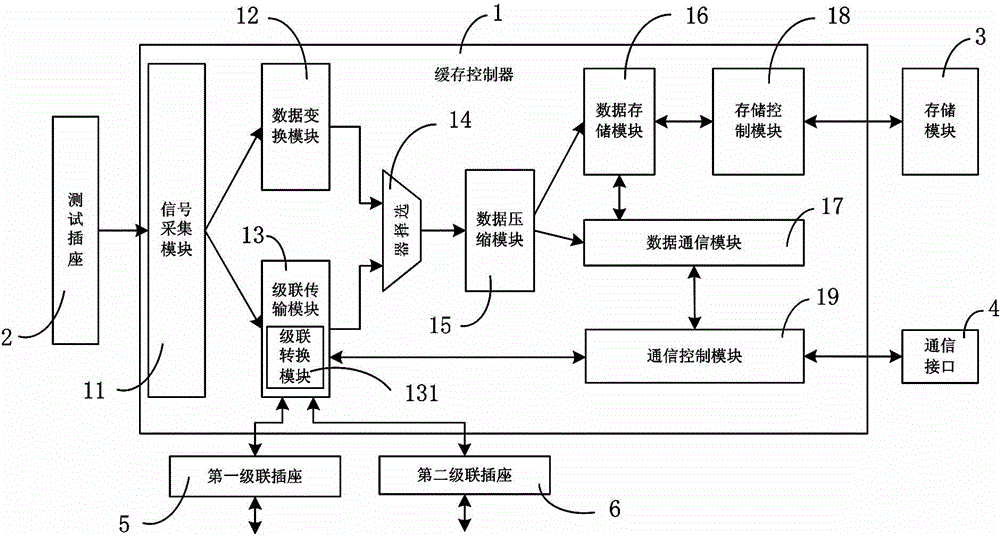

[0027] Such as figure 1 As shown, the signal sampling buffer device used for FPGA chip debugging in this embodiment includes a buffer controller 1, a test socket 2, a storage module 3, a communication interface 4 and a stage for realizing cascade connection between a plurality of signal sampling buffer devices The cascading socket module, the cache controller 1 is connected to the test socket 2, the storage module 3, and the communication interface 4 respectively, and the cascading socket module includes a signal sampling buffer device for connecting the upper level signal or the lower level signal respectively in the cascading working state. The first cascade socket 5 and the second cascade socket 6 of the sampling buffer device are connected to the cache controller 1 respectively. This embodiment aims at the problem that the internal signal observation and debugging tools provided by the existing FPGA manufacturers rely heavily on the scarce on-chip RAM resources inside the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com