SDRAM high-capacity image data register based on FPGA

An image data and buffer technology, applied in the field of data read and write controllers, can solve the problems of complex SDRAM read and write interfaces, unfavorable module migration, unfavorable operations, etc., and achieves the effects of low resource consumption, high timing performance, and easy migration.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Example Embodiment

[0020] The present invention will be further elaborated below in conjunction with the accompanying drawings.

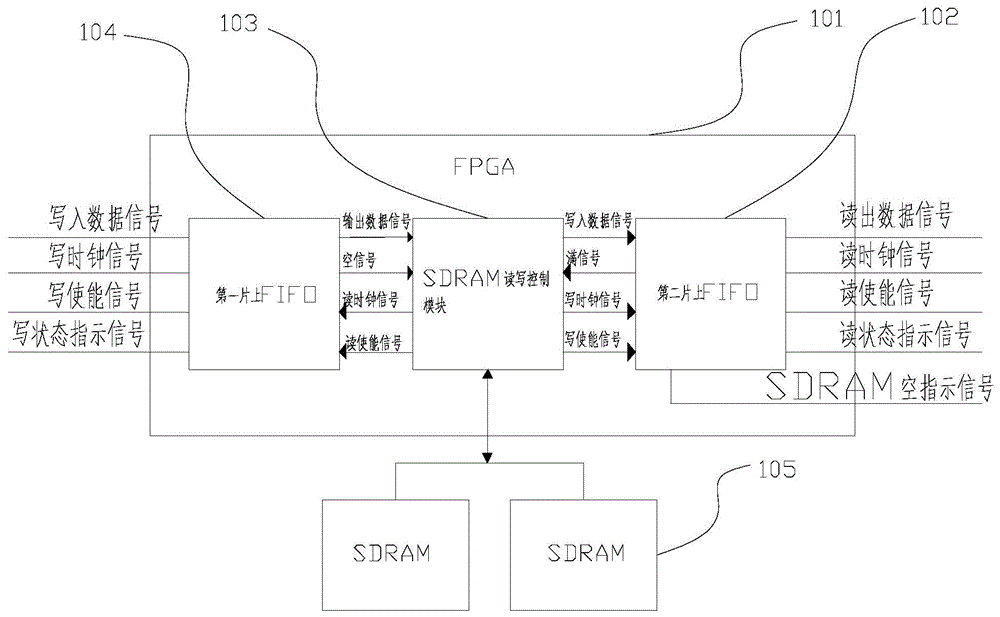

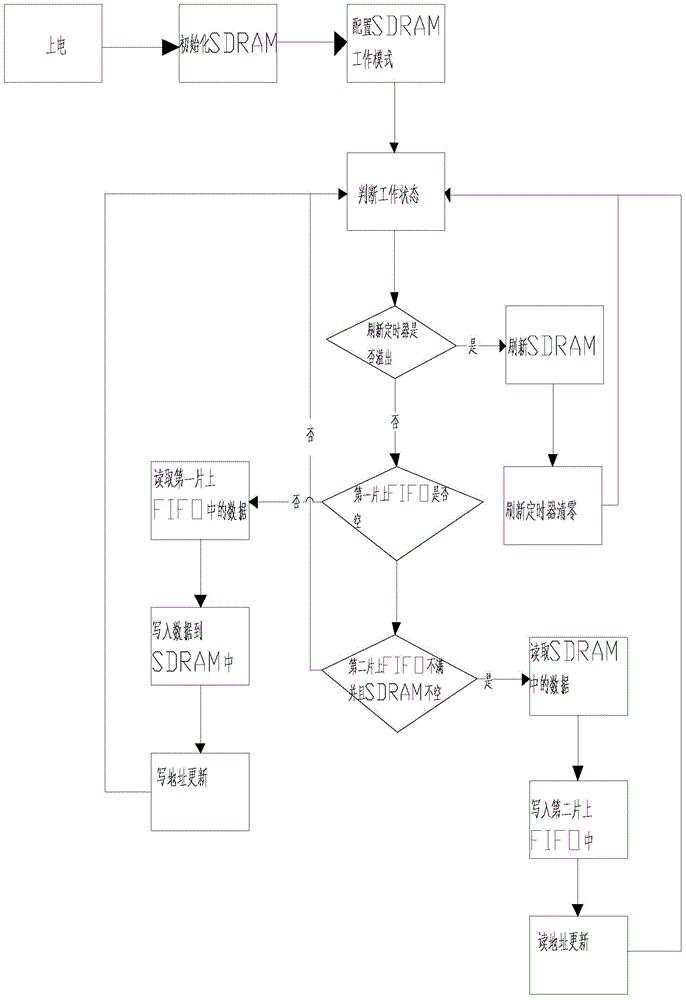

[0021] like figure 1 and figure 2 Shown, a kind of SDRAM large-capacity image data register based on FPGA, comprise FPGA101 and at least two SDRAM105 that are arranged on the outside of FPGA, described FPGA101 is connected with described SDRAM105, it is characterized in that: described FPGA101 includes for the first A first on-chip FIFO104 connected to the signal of the image data buffer write port, a second on-chip FIFO102 and SDRAM read-write controller 103 for connecting the second signal to the signal of the image data buffer read port, said The SDRAM read-write controller 103 is respectively connected to the first on-chip FIFO 104 and the second on-chip FIFO 102 .

[0022] According to an embodiment of the present invention, the first signal includes the input data signal of the first on-chip FIFO104, the write clock signal of the first on-chip FIFO104, the wr...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap