Composite error correction method for high-speed data acquisition system

A high-speed data acquisition and comprehensive error technology, applied in the direction of analog/digital conversion calibration/testing, can solve problems such as poor real-time performance, complex algorithms, and inability to adjust flexibly, and achieve the effects of strong versatility, improved accuracy and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The method of the present invention will be further described in detail below in conjunction with the accompanying drawings.

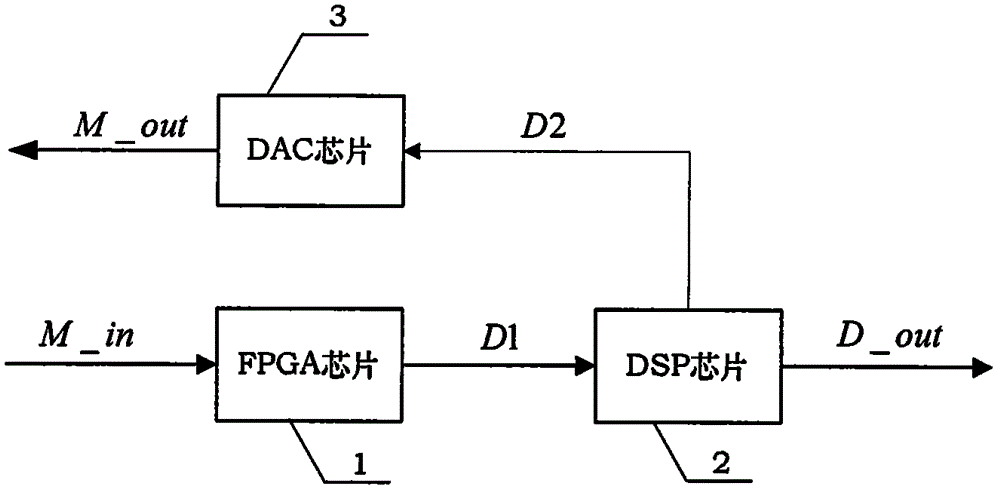

[0021] see figure 1 The shown hardware structure supporting the comprehensive error correction method used in the high-speed data acquisition system of the present invention is: including FPGA chip 1 , DSP chip 2 and DAC chip 3 . The DAC chip 3 is a D / A conversion integrated chip. The DSP chip 2 is a digital signal processor, which is a theory and technology for digitally representing and processing signals; DSP, Digital Signal Process. The interior of the DSP chip adopts the Harvard structure that separates the program and data, has a special hardware multiplier, widely uses pipeline operations, and provides special DSP instructions, which can be used to quickly implement various digital signal processing algorithms. The FPGA chip 1 is a field programmable gate array, which is a product further developed on the basis of programmable devices s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com