ADC built-in self-test circuit and test method in system on chip

A built-in self-test, system-on-chip technology, applied in the field of analog/mixed-signal integrated circuit testing, to achieve the effects of saving storage resources, improving computing accuracy, and reducing computing complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0066] In order to enable those skilled in the art to better understand the solutions of the embodiments of the present invention, the embodiments of the present invention will be further described in detail below in conjunction with the drawings and implementations.

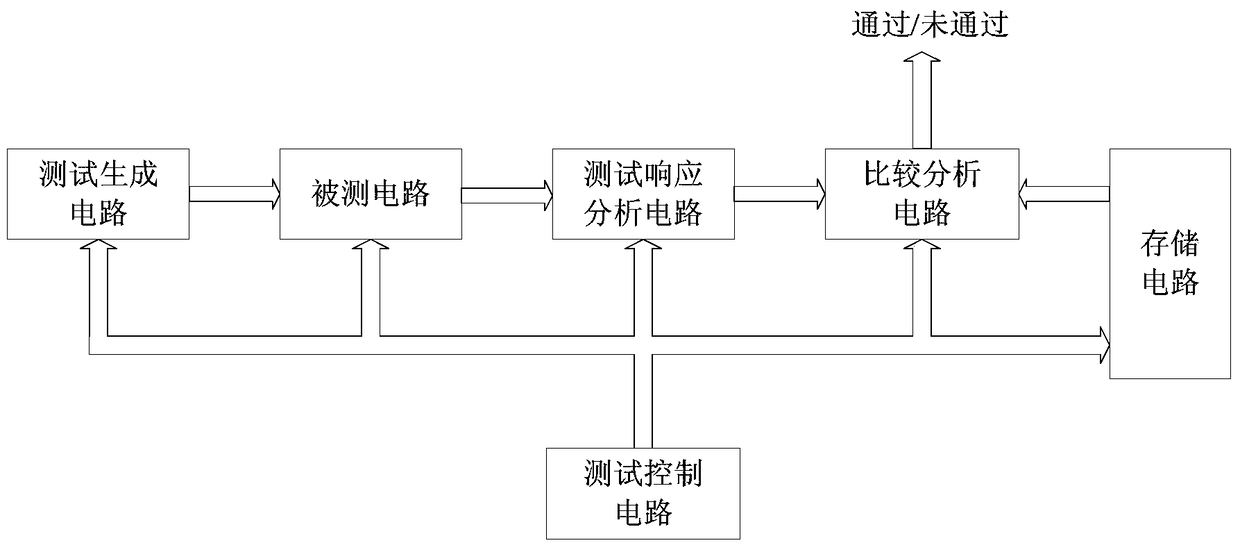

[0067] Such as figure 1 As shown, it is a schematic structural diagram of the ADC built-in self-test circuit in the system on chip of the embodiment of the present invention.

[0068] The circuit 100 includes: a control module 11 , a signal processing module 12 and a testing module 13 . in:

[0069] The control module 11 is configured to trigger the signal processing module 12 and the test module 13 to start working after the response signal output by the ADC to be tested is stable after the excitation signal is applied;

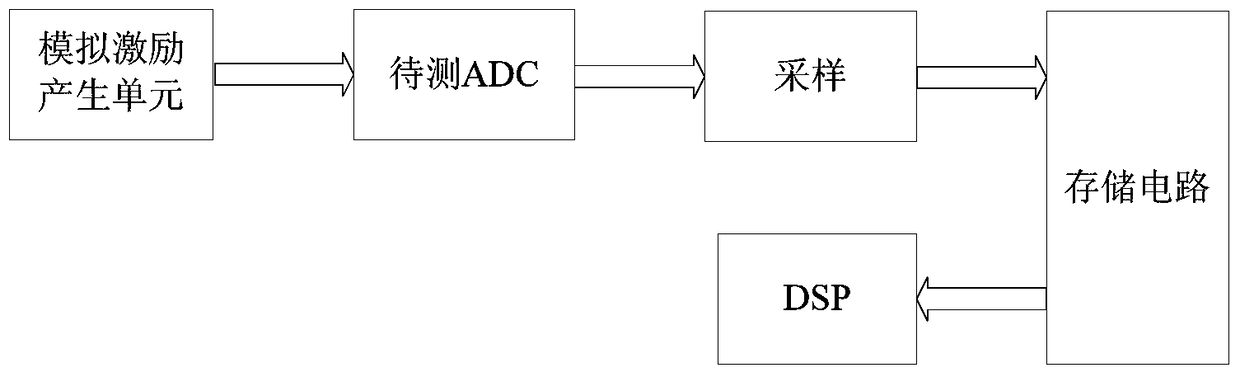

[0070] The signal processing module 12 is configured to sample the response signal, perform FFT transformation on the sampled value real sequence obtained by sampling, and obtain the spectru...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com