Partial scanning-based integrated circuit fault injection attack simulation method

A technology of fault injection and integrated circuits, applied in the direction of electronic circuit testing, measuring electricity, measuring electrical variables, etc., can solve the problems of high resource consumption and large resource consumption, and achieve the effect of low resource consumption and reduced resource consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The present invention will be further described below in conjunction with the accompanying drawings.

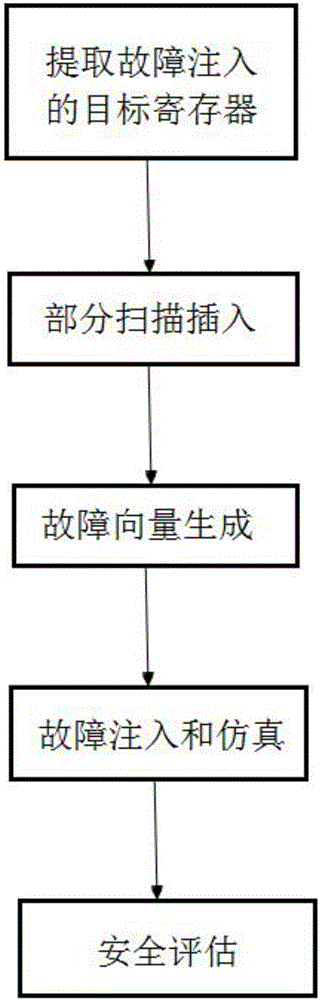

[0021] Such as figure 1 As shown, a partial scan-based integrated circuit fault injection attack simulation method of the present invention solves the problem of high resource consumption in the existing integrated circuit fault injection attack simulation method, and specifically includes the following steps:

[0022] Step 1, extract the target register of the fault injection

[0023] Synthesize the source code of the circuit design under test (that is, the source code of the hardware description for the circuit design under test) into the original netlist, set the target variable for fault injection, and extract the target register for fault injection.

[0024] Step 2, partial scan insertion

[0025] Use heuristic algorithm or other algorithms to select some registers from the original netlist as scan registers, insert scan chains and fault injection control module...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com