A Hardware Acceleration Circuit for Polygon Filling

A hardware-accelerated, polygon-based technology, applied to the details of image processing hardware, processor architecture/configuration, etc., can solve problems such as difficulty in meeting high-resolution and real-time application requirements, low polygon filling efficiency, and complex algorithms

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention will be described in detail below in conjunction with the accompanying drawings.

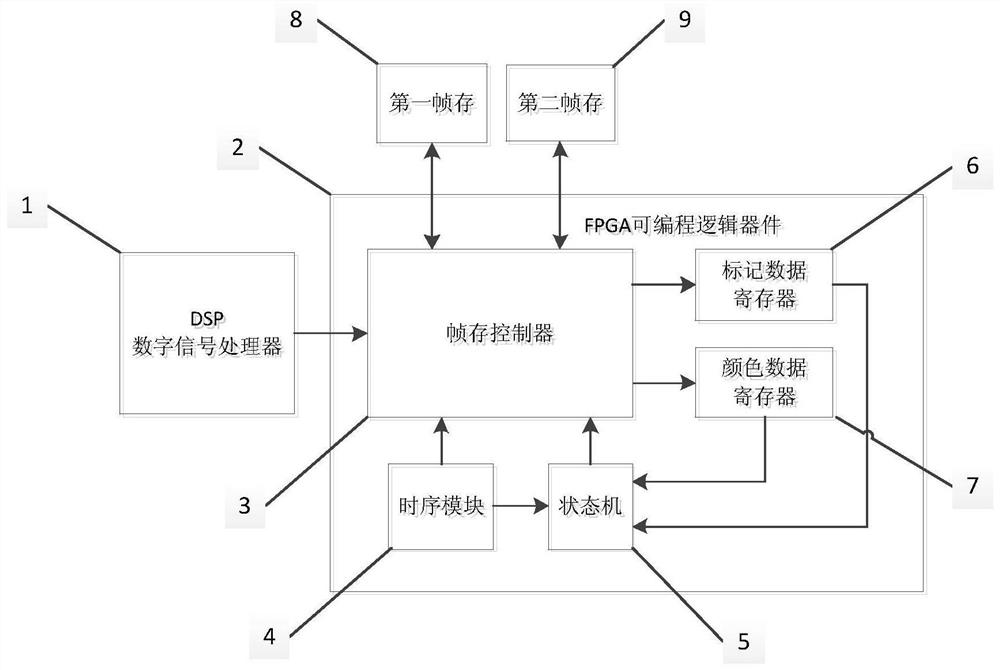

[0020] A hardware acceleration circuit for polygon filling, said circuit comprising: DSP digital signal processor 1, FPGA programmable logic device 2, first frame memory 8 and second frame memory 9;

[0021] The FPGA programmable logic device 2 includes a frame memory controller 3, a timing module 4, a state machine 5, a flag data register 6, and a color data register 7;

[0022] Wherein, the frame memory controller 3 is respectively connected with the DSP digital signal processor 1, the first frame memory 8, the second frame memory 9, the timing module 4, the state machine 5, the mark data register 6, and the color data register 7;

[0023] The timing module 4 , the mark data register 6 , and the color data register 7 are also connected to the state machine 5 respectively.

[0024] Described DSP digital signal processor 1 is used for carrying out drawing algorithm ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com