Fine-grained programmable sequential control logic module

A timing control and logic module technology, which is applied in the field of fine-grained programmable timing control logic modules, can solve problems such as many constraints, and achieve the effects of reducing failure rates, simple regulation, and efficient regulation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0045] In a first exemplary embodiment of the present disclosure, a fine-grain programmable timing control logic module is provided.

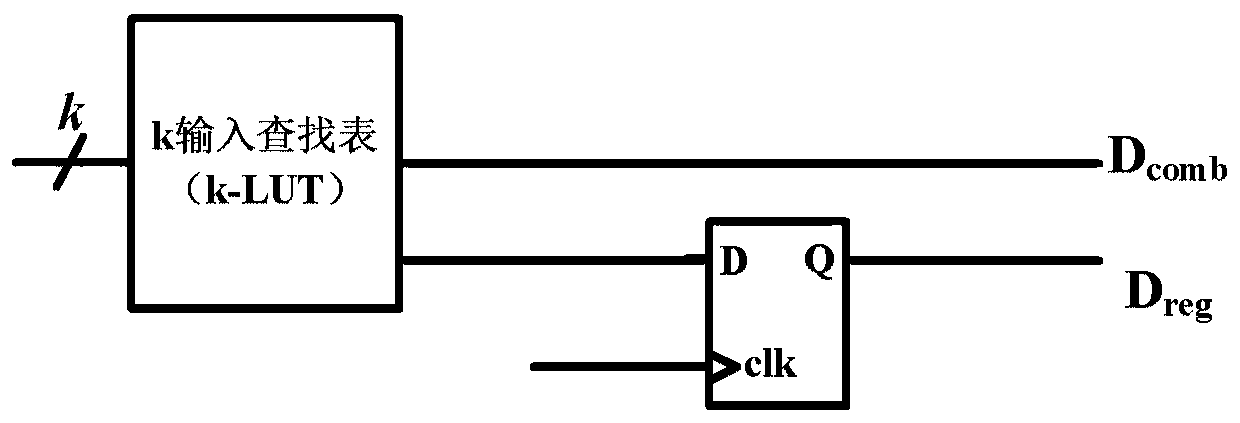

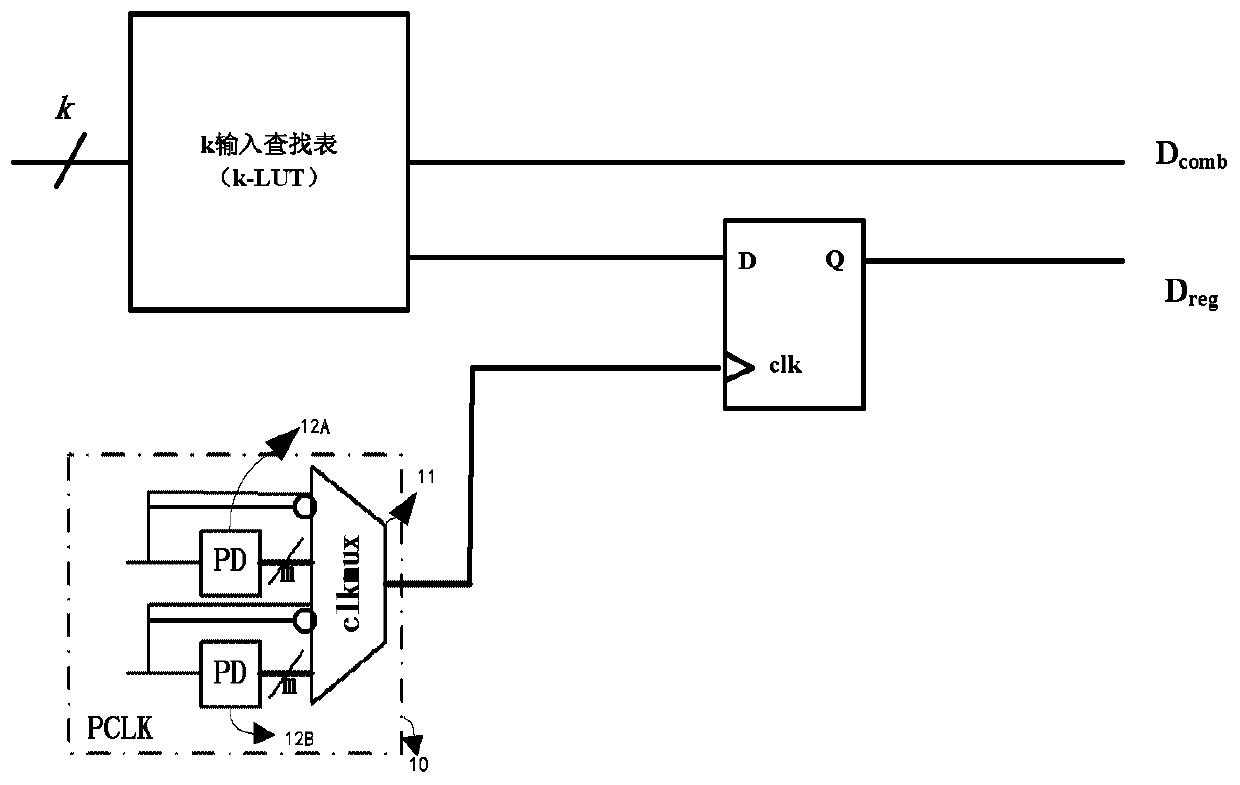

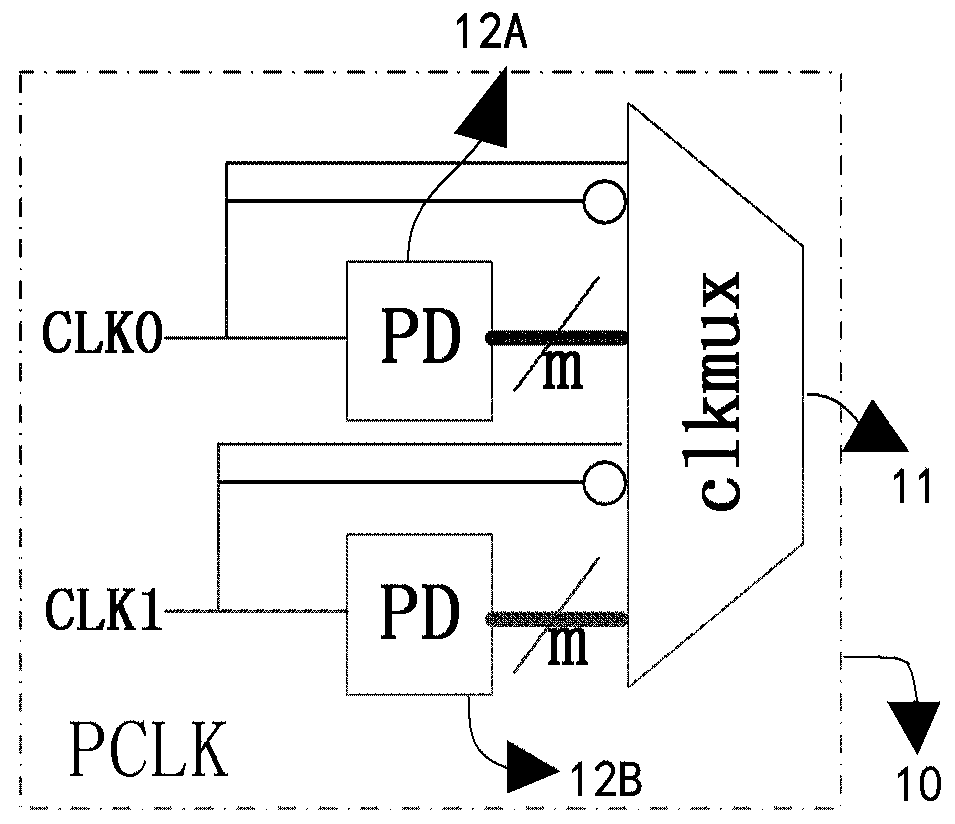

[0046] figure 2 It is a schematic structural diagram of a fine-grained programmable timing control logic module according to the first embodiment of the present disclosure.

[0047] refer to figure 2 As shown, the fine-grained programmable timing control logic module of the present disclosure includes: a programmable clock module, located on the internal clock path of the register in each programmable logic unit, and the register in a certain programmable logic unit does not meet the settling time In the case of setup and / or hold time, the programmable clock module of the internal clock path performs delay compensation to the register corresponding to the occurrence to meet the setup time and / or hold time.

[0048] In this example, if figure 2 As shown, the structure of a programmable logic unit is illustrated. The programmable logic unit...

no. 2 example

[0070] In a second exemplary embodiment of the present disclosure, a fine-grain programmable timing control logic module is provided. The fine-grained programmable timing control logic module of this embodiment is further optimized on the basis of the first embodiment.

[0071] Figure 9It is a schematic structural diagram of a fine-grained programmable timing control logic module according to the second embodiment of the present disclosure.

[0072] refer to Figure 9 As shown, in this embodiment, based on the structure of the first embodiment, a logic gate is provided at the control end of the register, and the logic gate is controlled by the SRAM to shield unnecessary control signals.

[0073] In this embodiment, the register is simultaneously controlled by the synchronous clear signal, the asynchronous clear signal, the synchronous number setting signal and the asynchronous number setting signal.

[0074] In some embodiments of the present disclosure, when among multipl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com