FPGA-based circuit module test method

A technology of circuit modules and testing methods, applied in digital circuit testing, electronic circuit testing, etc., can solve problems such as the inability to simulate the use environment of circuit modules such as IP cores, and achieve accurate test results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

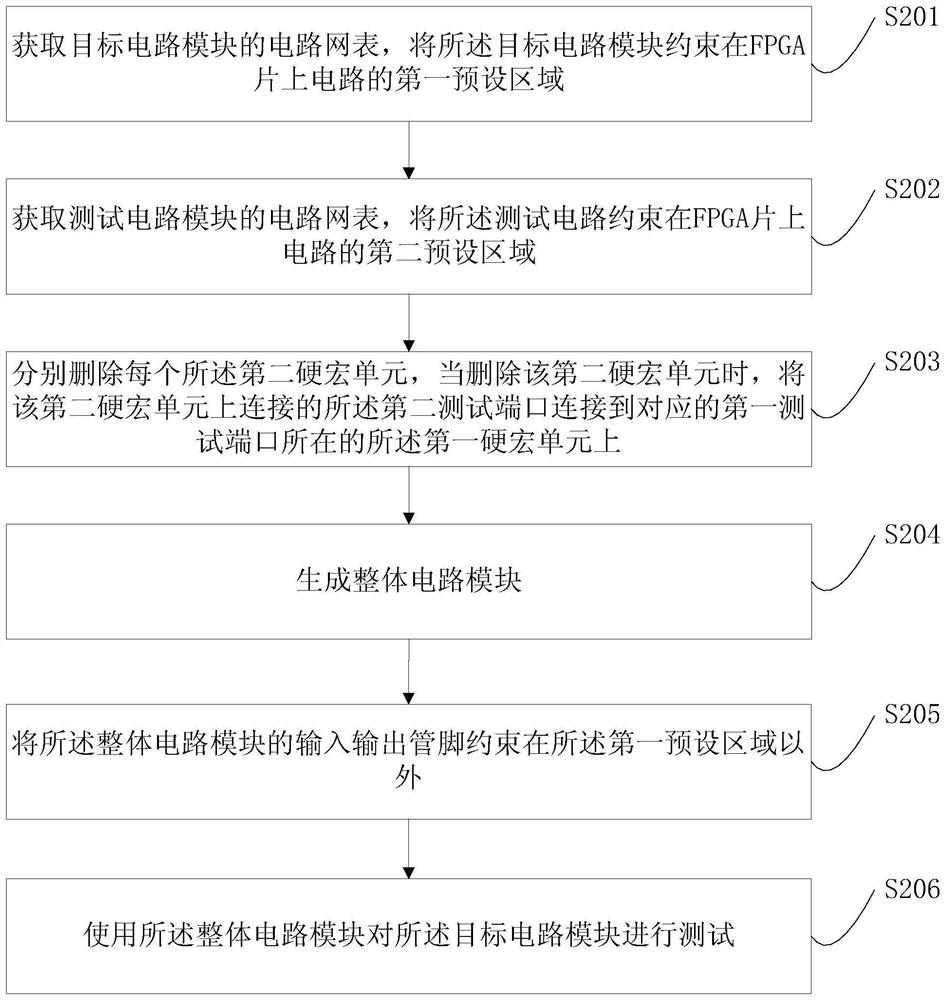

[0040] Such as figure 1 As shown, a kind of FPGA-based circuit module testing method provided by Embodiment 1 of the present invention comprises the following steps:

[0041] S101: Obtain a circuit netlist of a target circuit module, wherein at least one first test port of the target circuit module is led out to at least one first hard macrocell.

[0042] Here, the target circuit module is the circuit module to be tested in this embodiment, for example, an IP core that needs to be provided to the user.

[0043] S102: Obtain a circuit netlist of the test circuit module, wherein at least one second test port of the test circuit module is led out to at least one second hard macrocell.

[0044] Here, the test circuit module may include the call logic of the target circuit module, and may also include the test logic of the target circuit module.

[0045] In order to make the target circuit module and the test circuit module independent of each other, the circuit design of the tar...

Embodiment 2

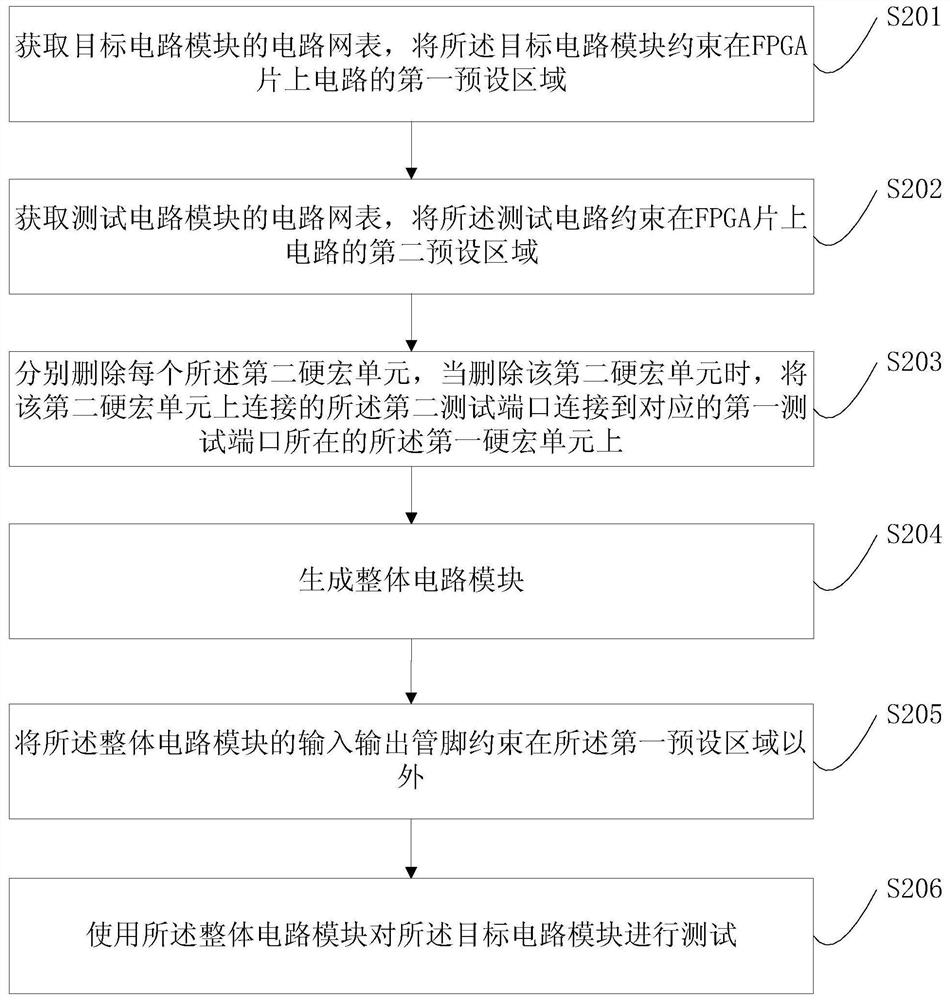

[0053] Such as figure 2 As shown, Embodiment 2 also provides another circuit module testing method, including the following steps:

[0054] S201: Obtain a circuit netlist of a target circuit module, and constrain the target circuit module to a first preset area of an FPGA on-chip circuit.

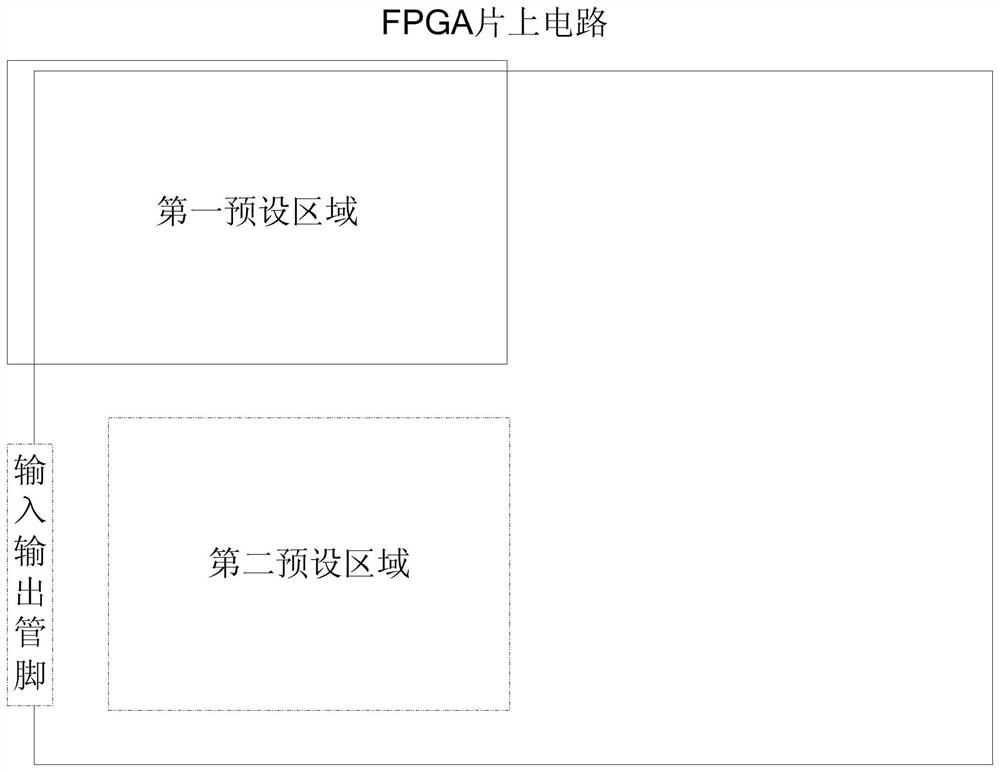

[0055] In order to further separate the target circuit module from the test circuit module, the target circuit module can be constrained in the first preset area of the FPGA on-chip circuit, for example, as image 3 As shown, the target circuit module is constrained to the upper left corner of the FPGA on-chip circuit. image 3 It is only a constraint method of the target circuit module, and it does not limit that the target circuit module must be constrained in the upper left corner. The target circuit module can be constrained in any position of the circuit on the FPGA chip. Since the target circuit module is usually a circuit that completes a specific function, and it is best to b...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap