Manufacturing method of three-dimensional memory and three-dimensional memory

A manufacturing method and memory technology, which are applied to semiconductor devices, electric solid-state devices, semiconductor/solid-state device components, etc., can solve problems such as damage to the control circuit structure and decrease in the reliability of three-dimensional memory, reduce static electricity, and enhance the effect of sharing and drainage. , the effect of enhancing structural stability and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

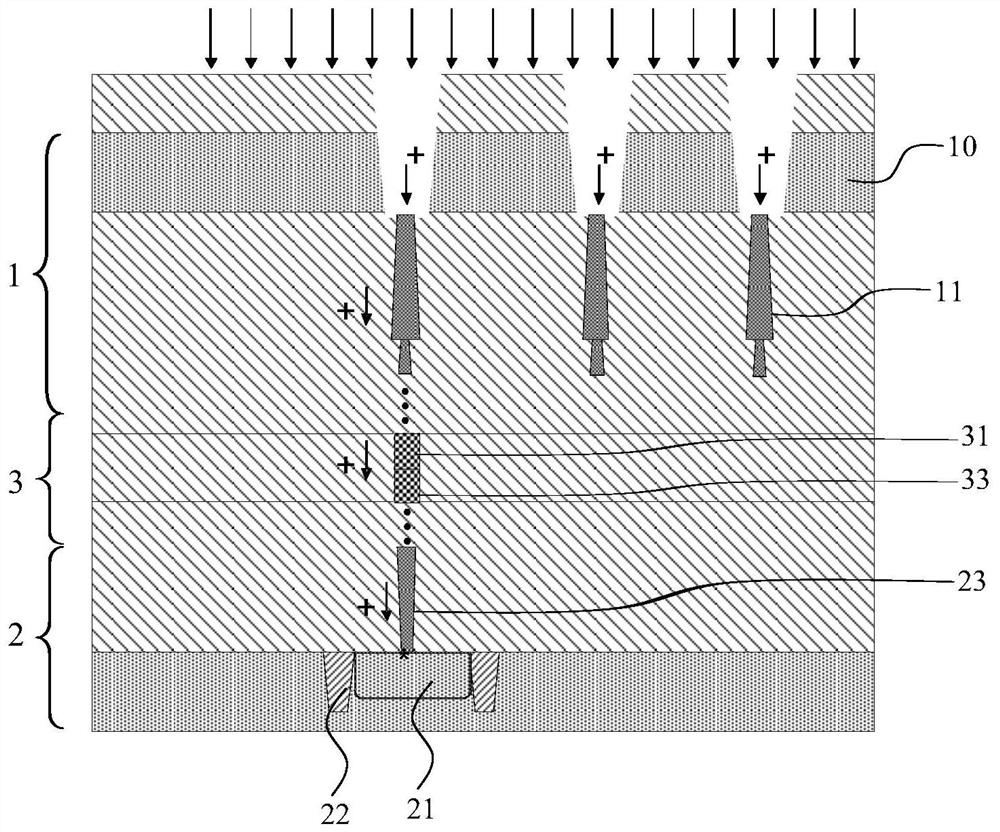

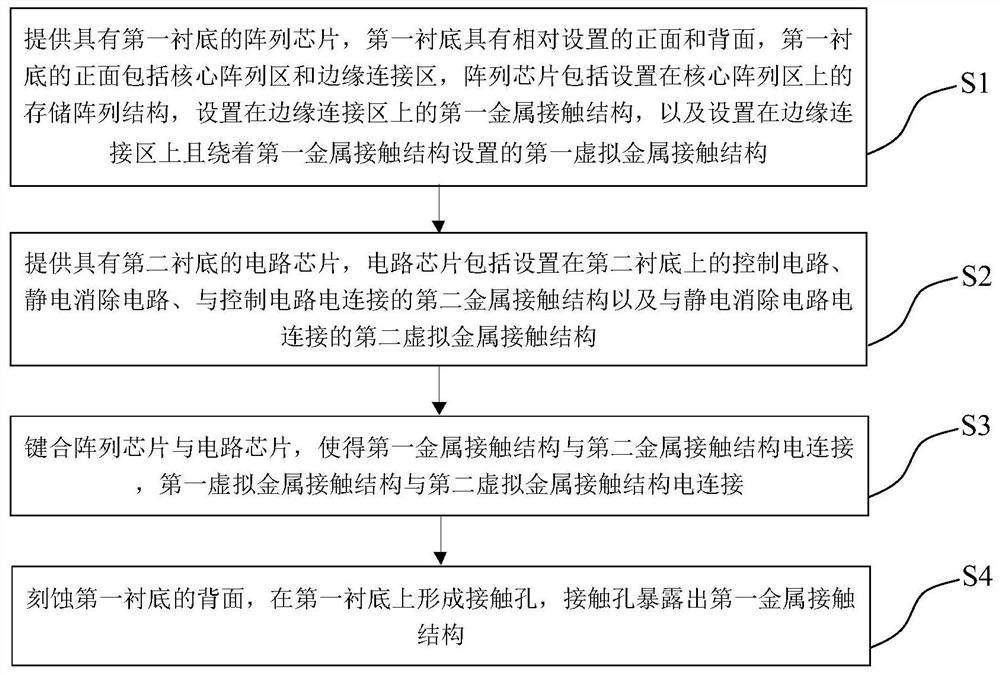

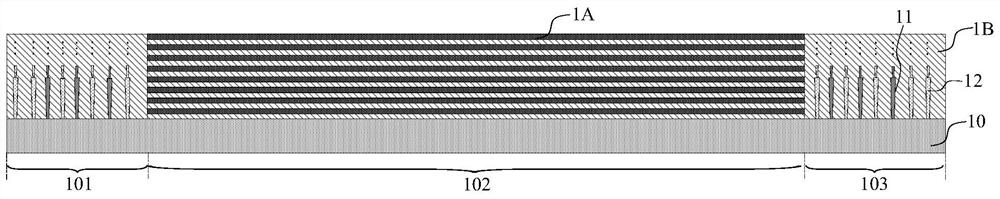

[0041] The inventor found that in the current manufacturing process of the three-dimensional memory, such as figure 1 As shown, after the array chip (i.e. storage array wafer) 1 and the circuit chip (i.e. CMOS circuit wafer) 2 are bonded through the bonding connection part 3, it is also necessary to etch the base 10 of the array chip 1, and the first metal The contact structure 11 is drawn out from the back of the array chip 1, which requires plasma etching, and the ions of plasma etching carry static electricity ( figure 1 middle "+" sign), static electricity will be conducted to the control circuit 21 on the circuit chip 2 along the first metal contact structure 11, the first pad 31, the third pad 33 and the second metal contact structure 23, a large amount of The accumulation of static electricity will cause structural damage to the control circuit 21, resulting in a decrease in the reliability of the three-dimensional memory.

[0042]Therefore, the present invention propo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com