System, method, device and processor for realizing large-scale FIFO data processing based on DDR, and storage medium thereof

A data processing, DDR4AXI technology, applied in the direction of electrical digital data processing, memory systems, instruments, etc., can solve the problems of not being able to make full use of the high-speed DDR interface bandwidth, long data transmission time, and large effective transmission time to meet the requirements of modular design demand, ensure continuous data collection, and improve the effect of time utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Example Embodiment

[0038] In order to be more clearly described, further description is made in conjunction with specific embodiments.

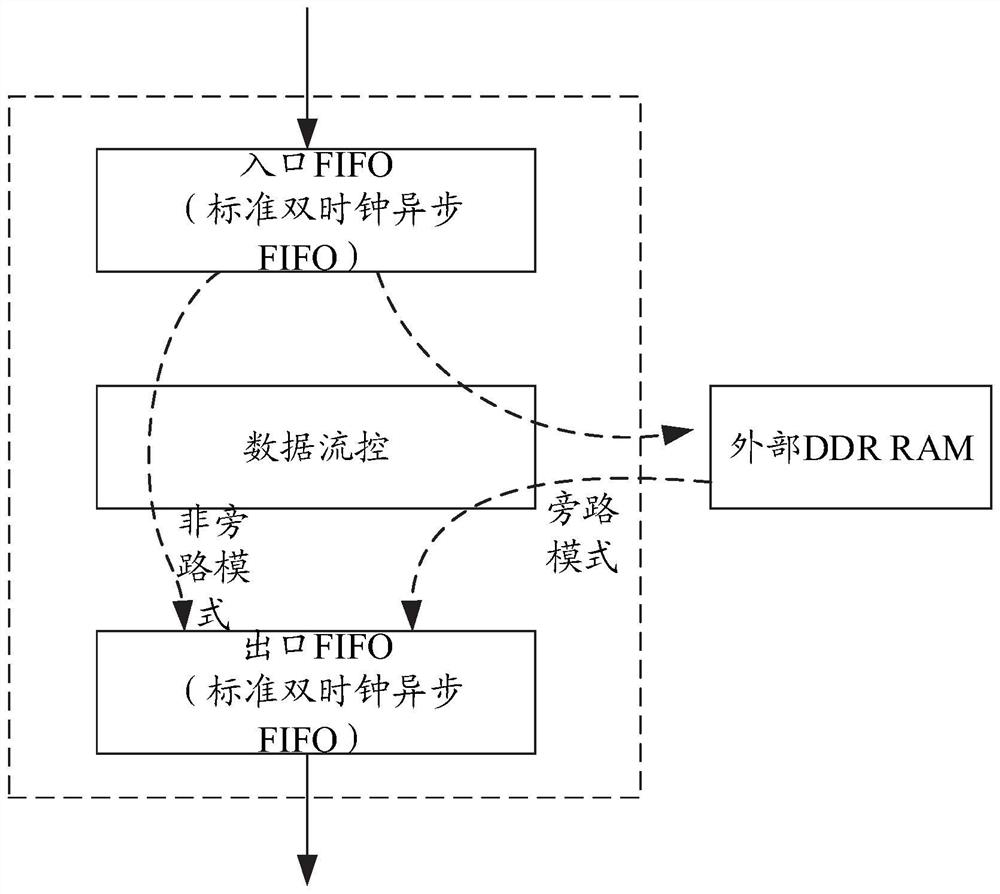

[0039] The DDR-based system-based system of the present invention implements a large-scale FIFO data, including:

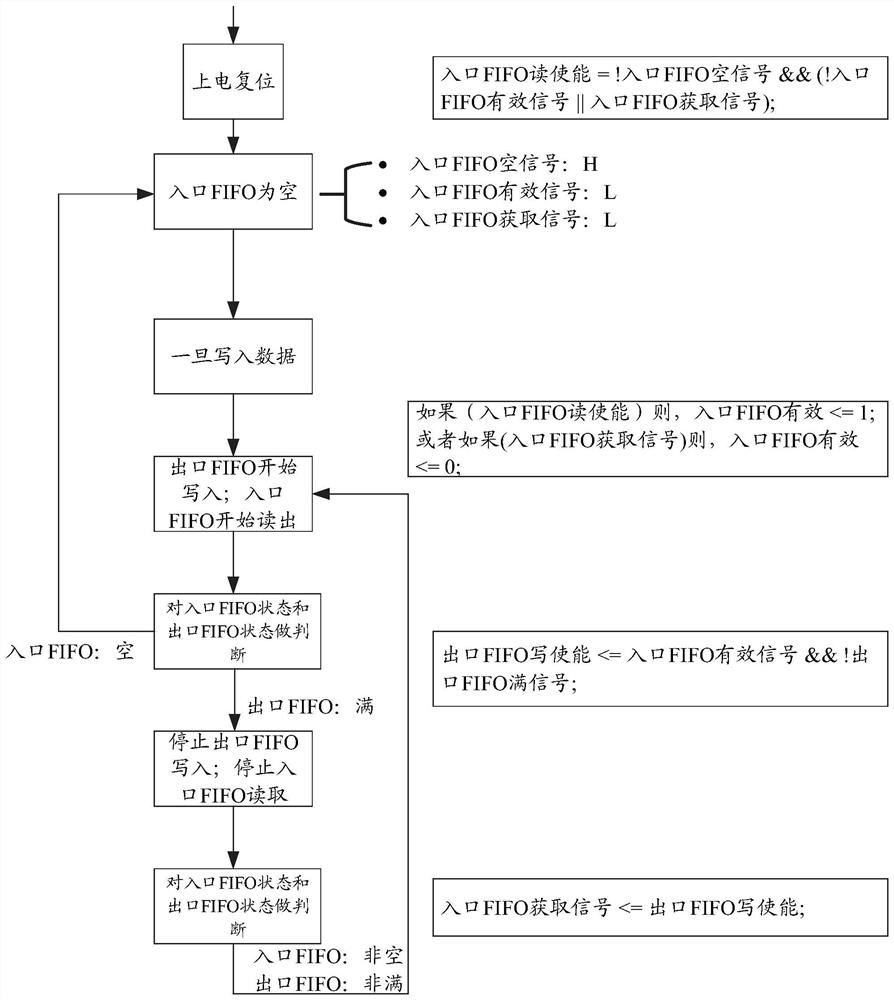

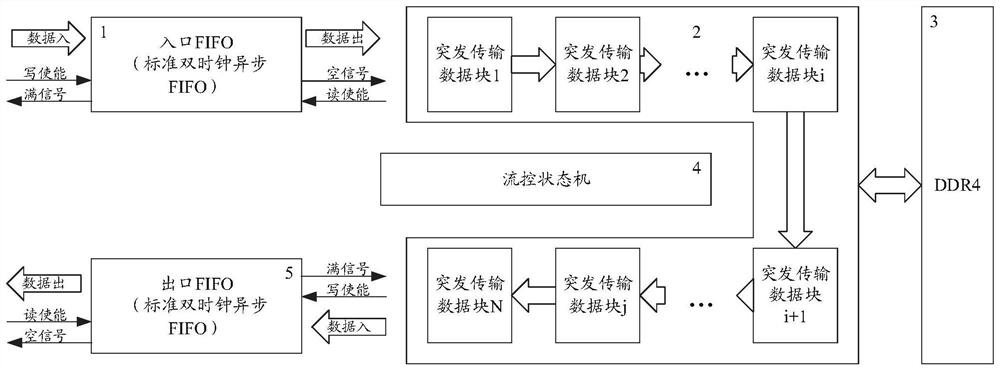

[0040] The entry asynchronous clock domain FIFO, has a separate write clock and read clock, independently sets the write data bit wide and read data bit wide, performing data writing operations;

[0041] The burst read and write data block is connected to the inlet asynchronous clock domain FIFO, and the data block list and the read data block list are written to the data block chain, and read the data block list.

[0042] The DDR4 AXI interface is connected to the burst read and write data block linked list for interaction with the flow control state machine and the burst reading.

[0043]Export asynchronous clock domain FIFO, is connected to the burst read and write data block linked table, configured to have a separate write clock and read clock, in...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap