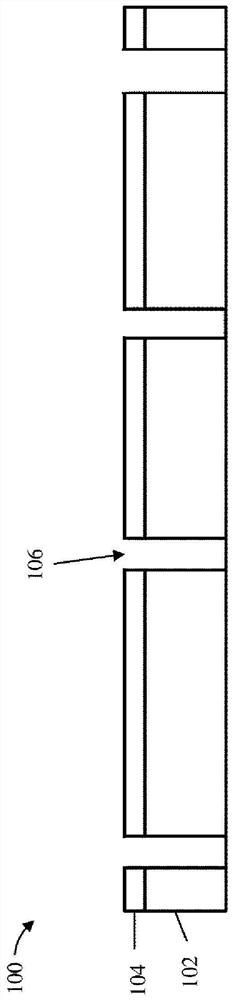

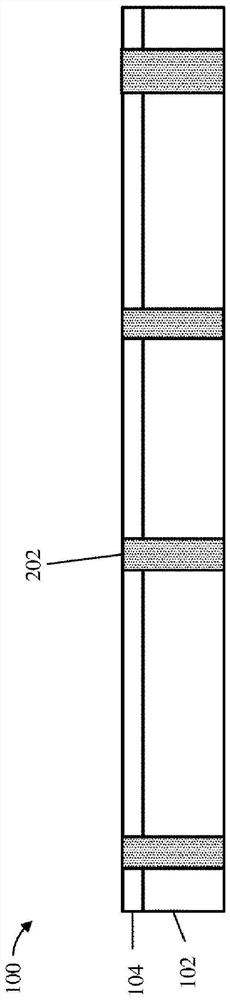

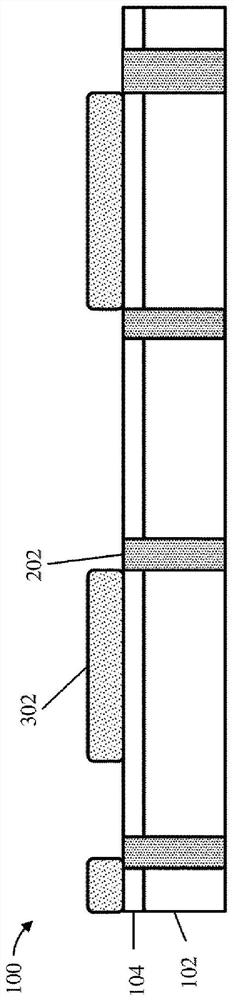

Wire end placement of top vias by selective growth of via mask from wire-cut dielectric

A technology of vias and masks, which is applied in the direction of circuits, electrical components, semiconductor/solid-state device components, etc., and can solve problems such as the complexity of the manufacturing process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] It is understood in advance that although example embodiments of the invention are described in connection with specific transistor architectures, embodiments of the invention are not limited to the specific transistor architectures or materials described in this specification. Rather, embodiments of the invention can be implemented in conjunction with any other type of transistor architecture or material now known or later developed.

[0026] For the sake of brevity, conventional techniques related to semiconductor device and integrated circuit (IC) fabrication may or may not be described in detail herein. Furthermore, the various tasks and process steps described herein may be incorporated into a more comprehensive procedure or process having additional steps or functionality not described in detail herein. In particular, various steps in the fabrication of semiconductor devices and semiconductor-based ICs are well known, and thus, for the sake of brevity, many conven...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com