Event-driven logic circuit

A logic circuit and event technology, applied in the field of logic circuits, can solve problems such as increased input load, increased activation rate of dynamic circuits, and high activation rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

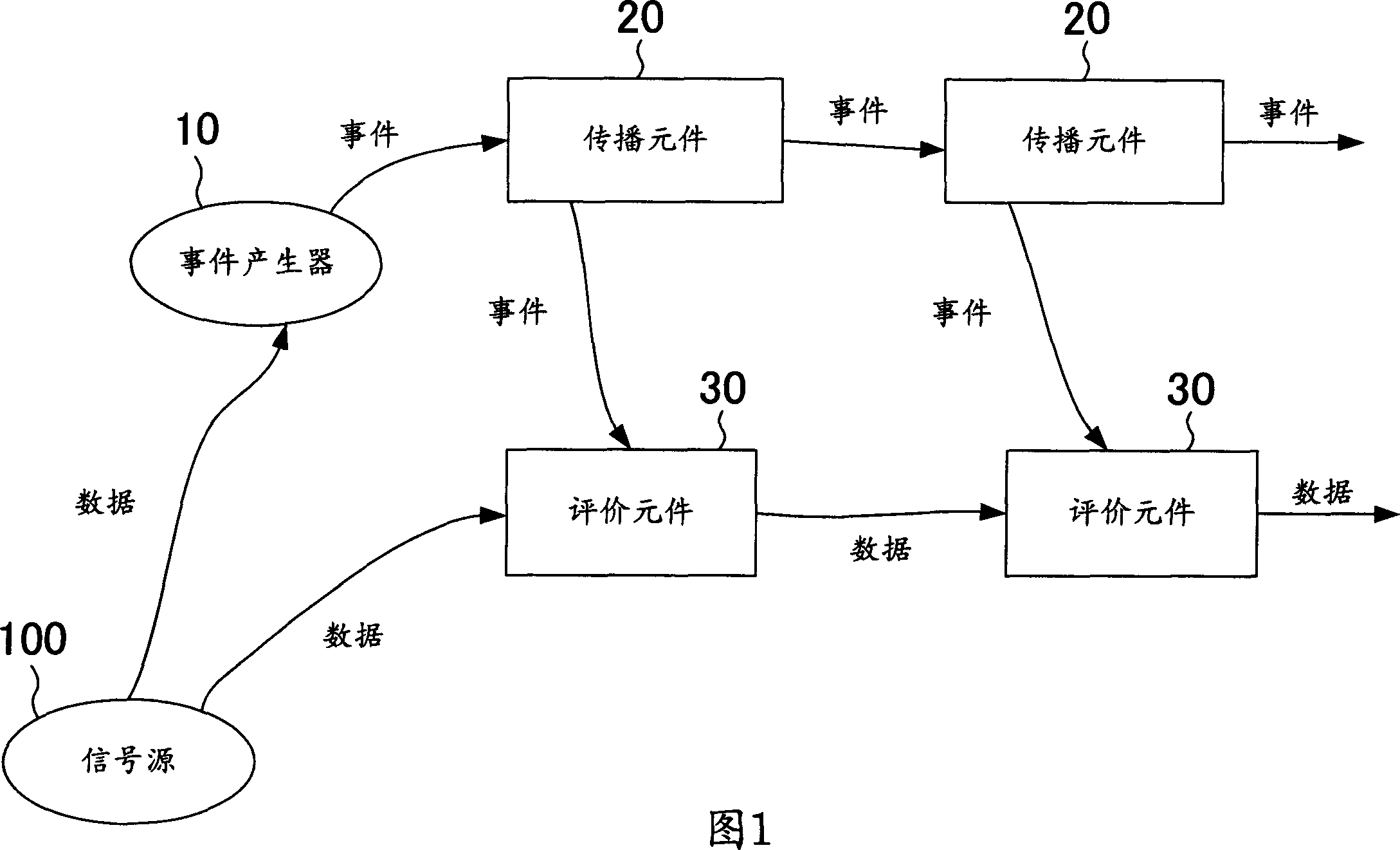

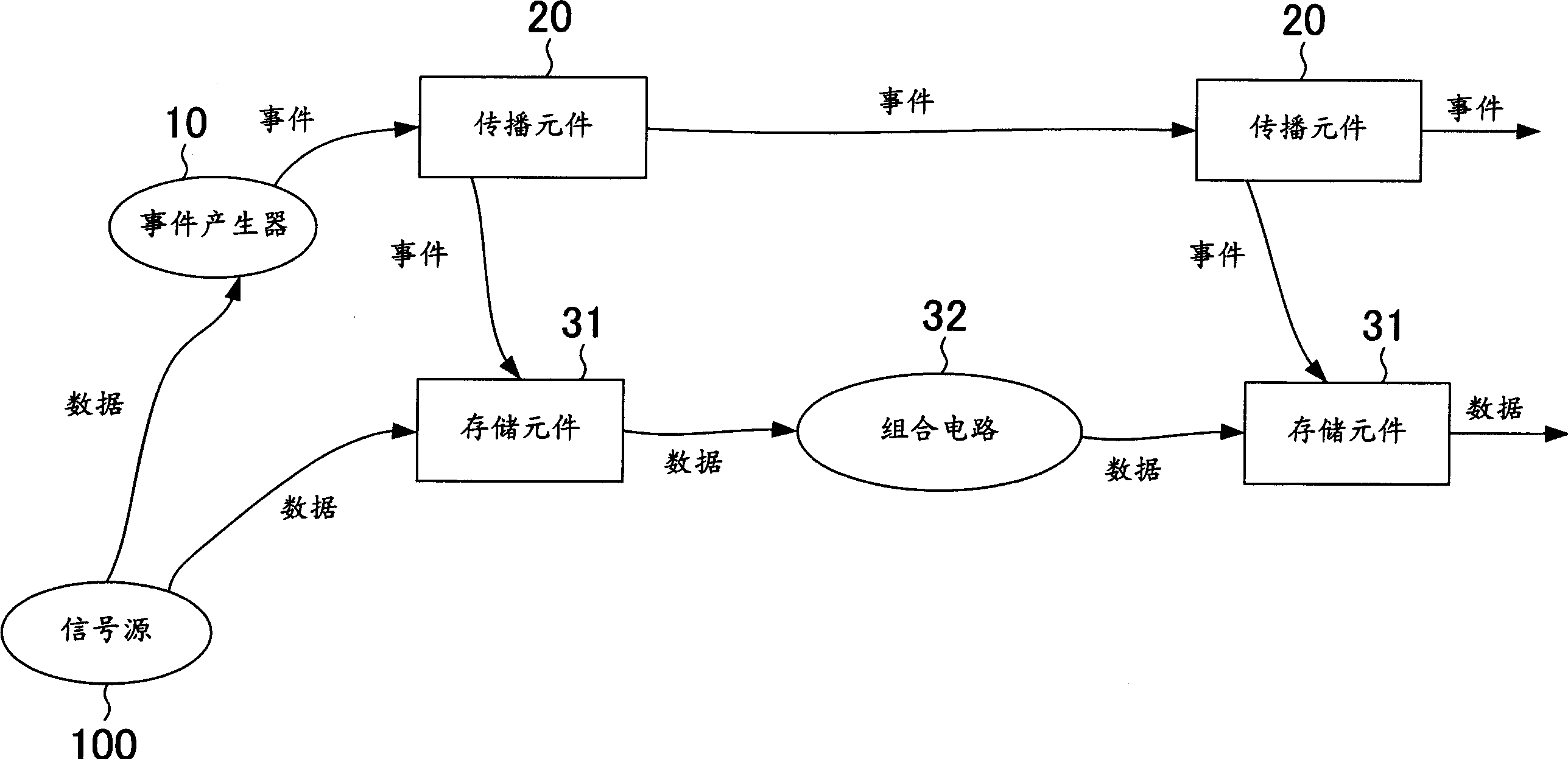

[0084] image 3 This is the schematic configuration of the logic circuit according to the first embodiment of the present invention. The logic circuit according to this embodiment includes a storage element 31 storing input data as an evaluation element. The operation of the logic circuit involved in this embodiment is as follows: First, as the output of the signal source 100 changes, the event generated in the event generator 10 is propagated in each propagation element 20 . The first-stage storage element 31 stores data output from the signal source 100 according to an event sent from the first-stage propagation element 20 . The data stored in the storage element 31 of the first stage is subjected to a logical operation by the combinational circuit 32, and the operation result is provided to the storage element 31 of the next stage. The next-level storage element 31 stores the data received from the combinational circuit 32 according to the event sent by the corresponding ...

no. 2 example

[0087] Figure 4 The circuit configuration of the evaluation element according to the second embodiment of the present invention is shown. The evaluation element according to this embodiment includes a capacitor 301, a charge and discharge controller 302 that controls charging and discharging of electric charges to and from the capacitor 301 according to events, a charging element 303 that charges the capacitor 301 under the control of the charge and discharge controller 302, and The discharge element 304 to be discharged determines the function-based discharge path evaluation logic circuit 305 and a static gate 306 such as an inverter. In addition, the capacitor 301 is preferably made of ferroelectric.

[0088] Next, refer to Figure 5 The timing chart of , illustrates the operation of the evaluation element involved in this embodiment. First, the charging element 303 operates by the generation of an event, and the charge holding state of the capacitor 301 is initialized. ...

no. 3 example

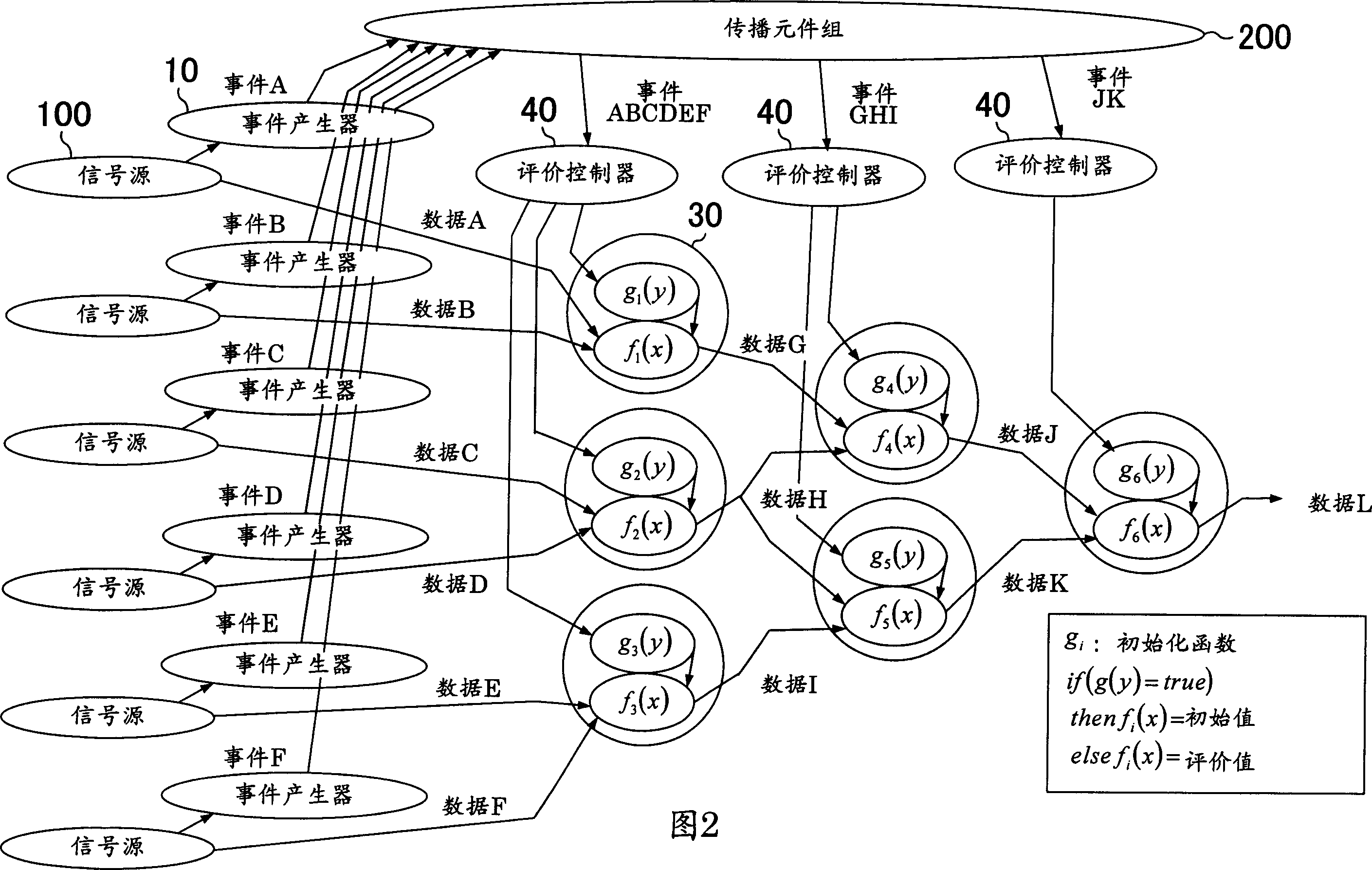

[0091] Image 6 A schematic configuration of a logic circuit according to a third embodiment of the present invention is shown. In the logic circuit according to the present embodiment, the evaluation element 30 includes an evaluation controller 40 that receives events from the propagation element 20 and outputs various control signals and substrate bias voltages, and inputs an input based on the control performed by the evaluation controller 40 . The evaluation unit 30' that evaluates the obtained data.

[0092] Figure 7 The circuit configuration of the evaluation element according to this example is shown. In addition, description of the evaluation controller is omitted. The evaluation element involved in this embodiment includes: an element 303 that controls the precharge operation according to the provided initialization control signal, an element 304 that controls the evaluation operation according to the provided evaluation control signal, and an evaluation logic cir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com