Redistribution Layer Design Tool Selection for PCB Layout

APR 7, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

PCB Redistribution Layer Design Background and Objectives

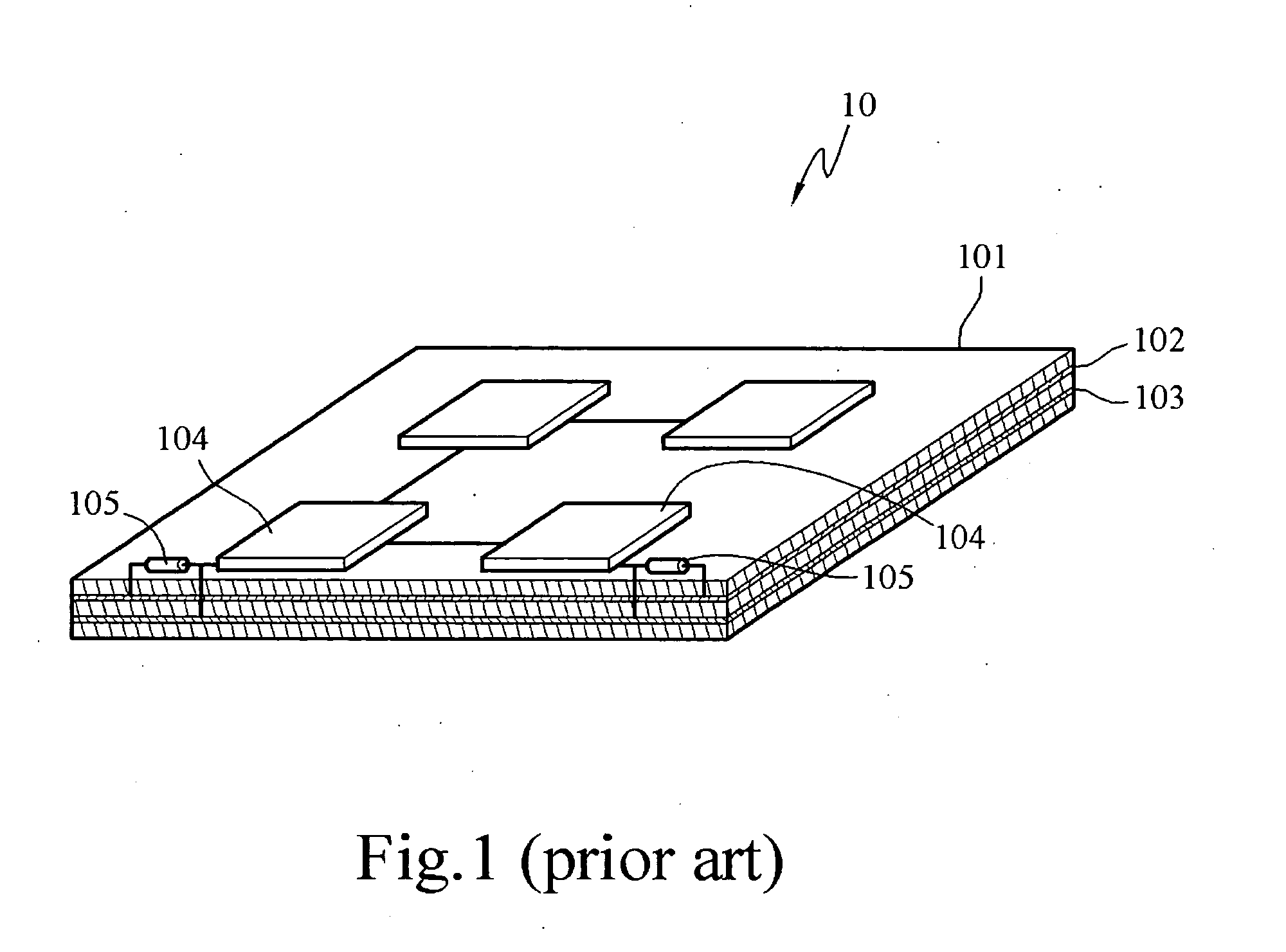

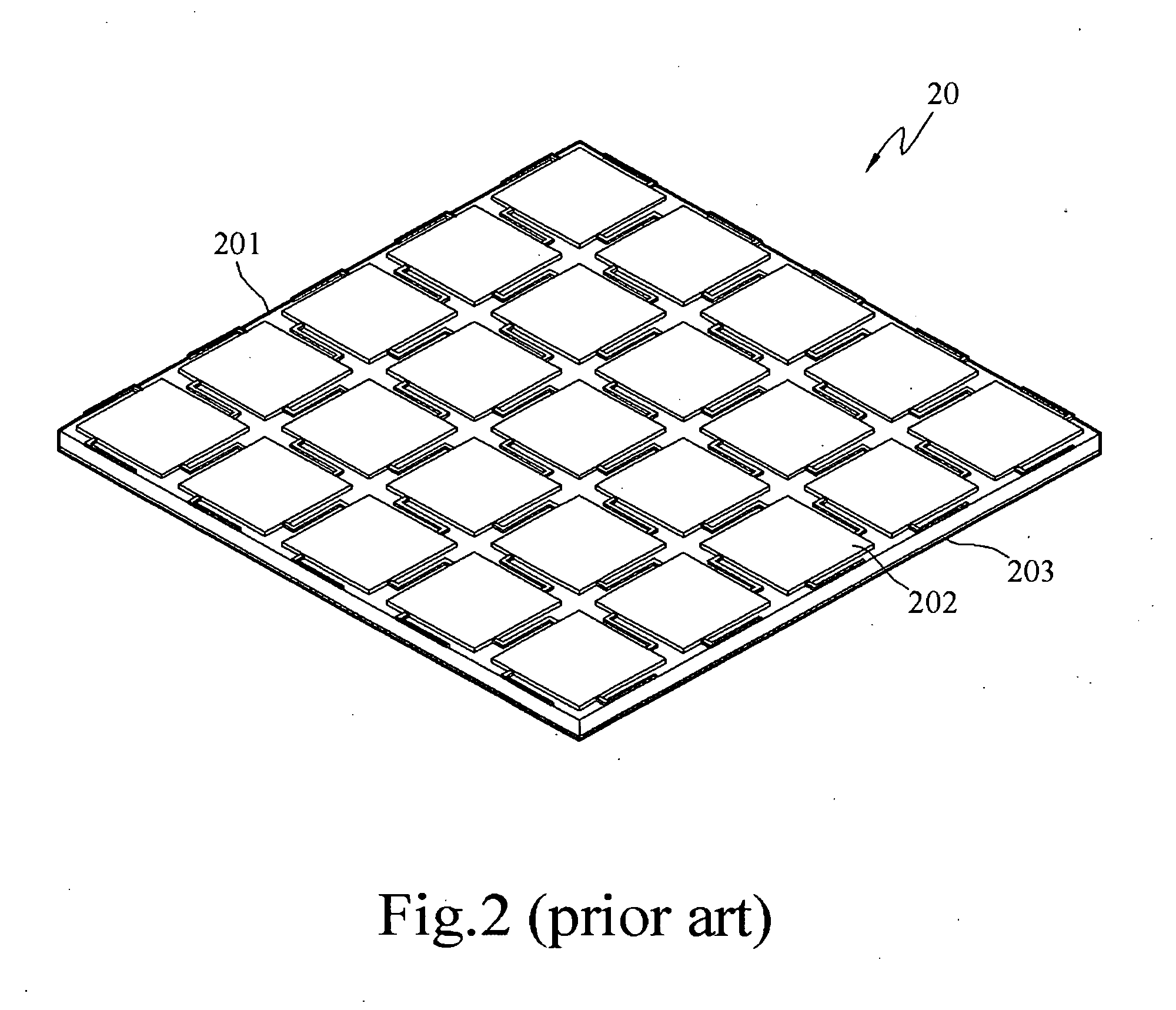

The evolution of printed circuit board (PCB) technology has witnessed a remarkable transformation from simple single-layer designs to complex multi-layer architectures capable of supporting high-density interconnections. As electronic devices continue to miniaturize while demanding increased functionality, the redistribution layer (RDL) has emerged as a critical component in advanced packaging solutions. This technology enables the rerouting of electrical connections from one pitch to another, facilitating the integration of fine-pitch components with standard PCB manufacturing processes.

The historical development of RDL technology traces back to the semiconductor packaging industry, where it was initially employed to redistribute bond pad locations on integrated circuits. Over the past two decades, this concept has been successfully adapted to PCB applications, particularly in high-density interconnect (HDI) boards and system-in-package (SiP) solutions. The technology has evolved from basic fan-out configurations to sophisticated multi-level redistribution architectures that support complex routing requirements.

Current market drivers for RDL implementation in PCB layouts include the proliferation of mobile devices, Internet of Things (IoT) applications, and advanced automotive electronics. These applications demand compact form factors while maintaining signal integrity and thermal performance. The increasing adoption of 5G technology and artificial intelligence processors further amplifies the need for sophisticated interconnection solutions that RDL technology can provide.

The primary technical objectives of RDL design encompass several critical aspects. Signal integrity preservation remains paramount, requiring careful consideration of impedance control, crosstalk minimization, and power delivery network optimization. Thermal management represents another crucial objective, as RDL structures must efficiently dissipate heat generated by high-performance components while maintaining structural integrity across varying temperature ranges.

Manufacturing feasibility and cost optimization constitute additional key objectives. RDL designs must align with existing fabrication capabilities while considering yield implications and production scalability. The selection of appropriate design tools becomes instrumental in achieving these objectives, as they directly impact design efficiency, accuracy, and manufacturability assessment capabilities.

Reliability and long-term performance objectives focus on ensuring robust interconnections that can withstand mechanical stress, thermal cycling, and environmental conditions throughout the product lifecycle. This requires sophisticated modeling capabilities and design verification tools that can predict and mitigate potential failure modes during the design phase.

The historical development of RDL technology traces back to the semiconductor packaging industry, where it was initially employed to redistribute bond pad locations on integrated circuits. Over the past two decades, this concept has been successfully adapted to PCB applications, particularly in high-density interconnect (HDI) boards and system-in-package (SiP) solutions. The technology has evolved from basic fan-out configurations to sophisticated multi-level redistribution architectures that support complex routing requirements.

Current market drivers for RDL implementation in PCB layouts include the proliferation of mobile devices, Internet of Things (IoT) applications, and advanced automotive electronics. These applications demand compact form factors while maintaining signal integrity and thermal performance. The increasing adoption of 5G technology and artificial intelligence processors further amplifies the need for sophisticated interconnection solutions that RDL technology can provide.

The primary technical objectives of RDL design encompass several critical aspects. Signal integrity preservation remains paramount, requiring careful consideration of impedance control, crosstalk minimization, and power delivery network optimization. Thermal management represents another crucial objective, as RDL structures must efficiently dissipate heat generated by high-performance components while maintaining structural integrity across varying temperature ranges.

Manufacturing feasibility and cost optimization constitute additional key objectives. RDL designs must align with existing fabrication capabilities while considering yield implications and production scalability. The selection of appropriate design tools becomes instrumental in achieving these objectives, as they directly impact design efficiency, accuracy, and manufacturability assessment capabilities.

Reliability and long-term performance objectives focus on ensuring robust interconnections that can withstand mechanical stress, thermal cycling, and environmental conditions throughout the product lifecycle. This requires sophisticated modeling capabilities and design verification tools that can predict and mitigate potential failure modes during the design phase.

Market Demand for Advanced PCB Layout Tools

The global PCB design software market has experienced substantial growth driven by the increasing complexity of electronic devices and the proliferation of advanced technologies such as 5G, IoT, artificial intelligence, and automotive electronics. Modern electronic products require sophisticated multilayer PCB designs with high-density interconnects, making traditional manual design approaches inadequate for meeting current industry demands.

The semiconductor packaging industry's evolution toward advanced packaging technologies, including system-in-package (SiP), chip-scale packages (CSP), and wafer-level packaging, has created significant demand for specialized redistribution layer design capabilities. These technologies require precise routing of fine-pitch interconnects and complex via structures that exceed the capabilities of conventional PCB layout tools.

Automotive electronics represents a particularly strong growth driver, with the shift toward electric vehicles and autonomous driving systems demanding PCBs with enhanced thermal management, signal integrity, and reliability characteristics. The automotive sector's stringent quality requirements and safety standards necessitate advanced design tools capable of comprehensive design rule checking and simulation capabilities.

The telecommunications infrastructure expansion, particularly 5G network deployment, has intensified demand for high-frequency PCB designs requiring sophisticated electromagnetic simulation and signal integrity analysis tools. These applications demand tools capable of handling complex impedance control, crosstalk analysis, and power delivery network optimization.

Consumer electronics manufacturers face increasing pressure to reduce product development cycles while improving performance and miniaturization. This market dynamic drives demand for automated design tools that can accelerate the redistribution layer design process while maintaining design quality and manufacturability.

The aerospace and defense sectors continue to require specialized PCB design capabilities for mission-critical applications, driving demand for tools with advanced reliability analysis, thermal simulation, and compliance verification features. These markets value tools that can ensure design robustness under extreme operating conditions.

Emerging applications in medical devices, wearable technology, and flexible electronics are creating new market segments requiring specialized design capabilities. These applications often involve unique substrate materials, flexible circuits, and biocompatibility considerations that traditional tools may not adequately address.

The market shows strong preference for integrated design environments that combine schematic capture, layout design, simulation, and manufacturing preparation capabilities. Tool interoperability and seamless data exchange between different design phases have become critical selection criteria for many organizations seeking to optimize their design workflows.

The semiconductor packaging industry's evolution toward advanced packaging technologies, including system-in-package (SiP), chip-scale packages (CSP), and wafer-level packaging, has created significant demand for specialized redistribution layer design capabilities. These technologies require precise routing of fine-pitch interconnects and complex via structures that exceed the capabilities of conventional PCB layout tools.

Automotive electronics represents a particularly strong growth driver, with the shift toward electric vehicles and autonomous driving systems demanding PCBs with enhanced thermal management, signal integrity, and reliability characteristics. The automotive sector's stringent quality requirements and safety standards necessitate advanced design tools capable of comprehensive design rule checking and simulation capabilities.

The telecommunications infrastructure expansion, particularly 5G network deployment, has intensified demand for high-frequency PCB designs requiring sophisticated electromagnetic simulation and signal integrity analysis tools. These applications demand tools capable of handling complex impedance control, crosstalk analysis, and power delivery network optimization.

Consumer electronics manufacturers face increasing pressure to reduce product development cycles while improving performance and miniaturization. This market dynamic drives demand for automated design tools that can accelerate the redistribution layer design process while maintaining design quality and manufacturability.

The aerospace and defense sectors continue to require specialized PCB design capabilities for mission-critical applications, driving demand for tools with advanced reliability analysis, thermal simulation, and compliance verification features. These markets value tools that can ensure design robustness under extreme operating conditions.

Emerging applications in medical devices, wearable technology, and flexible electronics are creating new market segments requiring specialized design capabilities. These applications often involve unique substrate materials, flexible circuits, and biocompatibility considerations that traditional tools may not adequately address.

The market shows strong preference for integrated design environments that combine schematic capture, layout design, simulation, and manufacturing preparation capabilities. Tool interoperability and seamless data exchange between different design phases have become critical selection criteria for many organizations seeking to optimize their design workflows.

Current State of Redistribution Layer Design Tools

The redistribution layer (RDL) design tool landscape for PCB layout has evolved significantly over the past decade, driven by increasing demands for miniaturization and higher interconnect density in electronic packaging. Current RDL design tools can be broadly categorized into three tiers: enterprise-level comprehensive solutions, specialized RDL-focused platforms, and integrated modules within traditional PCB design suites.

Enterprise-level solutions dominate the high-end market, with tools like Cadence Allegro Package Designer Plus and Mentor Graphics IC Packaging leading the segment. These platforms offer sophisticated capabilities for complex multi-layer RDL routing, advanced via optimization algorithms, and comprehensive design rule checking specifically tailored for wafer-level packaging applications. They typically feature integrated electromagnetic simulation engines and support for industry-standard file formats including GDSII and OASIS.

Specialized RDL design platforms have emerged to address specific packaging requirements, particularly for fan-out wafer-level packaging and system-in-package applications. Tools such as ASE Group's proprietary design suite and STATS ChipPAC's internal platforms focus exclusively on RDL optimization, offering streamlined workflows for rapid prototyping and production-ready designs. These solutions often incorporate machine learning algorithms for automatic routing optimization and thermal management.

Traditional PCB design tool vendors have expanded their offerings to include RDL capabilities, recognizing the convergence between PCB and package design domains. Altium Designer, KiCad, and Zuken CR-8000 have introduced RDL-specific features, though with varying degrees of sophistication compared to dedicated solutions.

The current technological landscape faces several constraints, including limited interoperability between different tool ecosystems, insufficient support for emerging packaging technologies like chiplet integration, and challenges in handling the increasing complexity of heterogeneous integration scenarios. Most existing tools struggle with real-time design optimization for manufacturability, particularly regarding yield prediction and process variation modeling.

Open-source initiatives are gaining traction, with projects like OpenROAD beginning to incorporate RDL design capabilities, though these remain primarily in research and development phases. The integration of artificial intelligence and machine learning into RDL design tools represents an emerging trend, with several vendors developing predictive routing algorithms and automated design optimization features.

Enterprise-level solutions dominate the high-end market, with tools like Cadence Allegro Package Designer Plus and Mentor Graphics IC Packaging leading the segment. These platforms offer sophisticated capabilities for complex multi-layer RDL routing, advanced via optimization algorithms, and comprehensive design rule checking specifically tailored for wafer-level packaging applications. They typically feature integrated electromagnetic simulation engines and support for industry-standard file formats including GDSII and OASIS.

Specialized RDL design platforms have emerged to address specific packaging requirements, particularly for fan-out wafer-level packaging and system-in-package applications. Tools such as ASE Group's proprietary design suite and STATS ChipPAC's internal platforms focus exclusively on RDL optimization, offering streamlined workflows for rapid prototyping and production-ready designs. These solutions often incorporate machine learning algorithms for automatic routing optimization and thermal management.

Traditional PCB design tool vendors have expanded their offerings to include RDL capabilities, recognizing the convergence between PCB and package design domains. Altium Designer, KiCad, and Zuken CR-8000 have introduced RDL-specific features, though with varying degrees of sophistication compared to dedicated solutions.

The current technological landscape faces several constraints, including limited interoperability between different tool ecosystems, insufficient support for emerging packaging technologies like chiplet integration, and challenges in handling the increasing complexity of heterogeneous integration scenarios. Most existing tools struggle with real-time design optimization for manufacturability, particularly regarding yield prediction and process variation modeling.

Open-source initiatives are gaining traction, with projects like OpenROAD beginning to incorporate RDL design capabilities, though these remain primarily in research and development phases. The integration of artificial intelligence and machine learning into RDL design tools represents an emerging trend, with several vendors developing predictive routing algorithms and automated design optimization features.

Existing Redistribution Layer Design Solutions

01 Automated routing and trace optimization for redistribution layers

Design tools that automatically generate and optimize routing patterns for redistribution layers in semiconductor packaging. These tools analyze design constraints, spacing requirements, and electrical parameters to create efficient interconnect layouts. The automation reduces manual design time and improves routing density while ensuring signal integrity and manufacturability compliance.- Automated routing and trace optimization for redistribution layers: Design tools that automatically generate and optimize routing patterns for redistribution layers in semiconductor packaging. These tools analyze design constraints, spacing requirements, and electrical parameters to create efficient interconnect layouts. The automation reduces manual design time and improves routing density while ensuring signal integrity and manufacturability compliance.

- Design rule checking and verification for RDL structures: Tools that perform comprehensive design rule checking specifically tailored for redistribution layer geometries and constraints. These verification systems validate spacing, width, via placement, and layer-to-layer alignment requirements. The tools identify potential manufacturing issues early in the design process and ensure compliance with foundry specifications and electrical performance requirements.

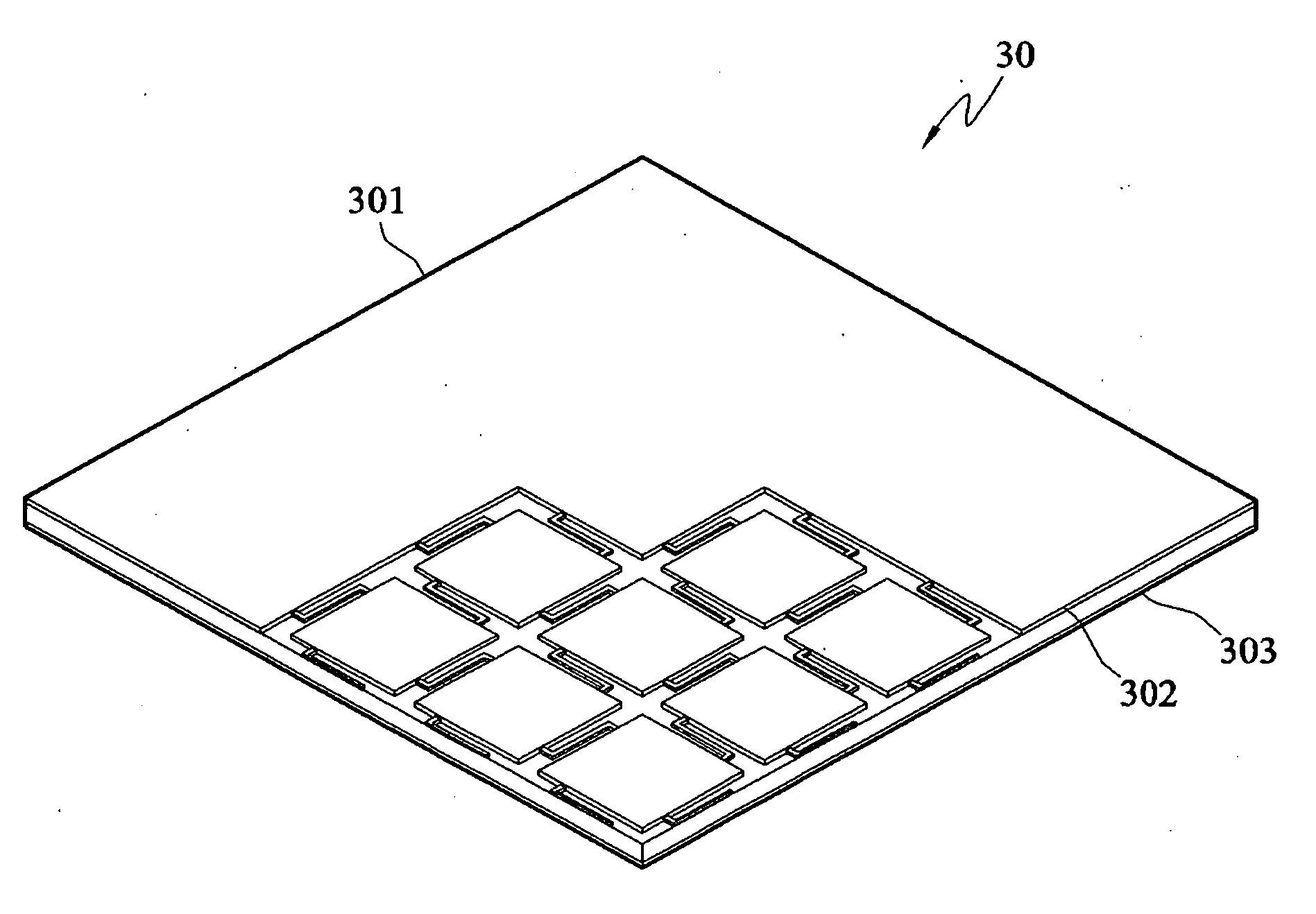

- 3D visualization and layout planning for multi-layer RDL: Design tools providing three-dimensional visualization capabilities for complex multi-layer redistribution structures. These systems enable designers to view and manipulate RDL layouts in 3D space, facilitating better understanding of layer interactions and potential conflicts. The visualization aids in planning bump placement, via stacking, and overall package architecture optimization.

- Electrical simulation and analysis integration: Tools that integrate electrical simulation capabilities directly into the RDL design environment. These systems perform parasitic extraction, signal integrity analysis, power distribution network analysis, and thermal simulation for redistribution layer structures. The integration allows designers to evaluate electrical performance during layout creation and make informed design decisions to meet specifications.

- Library management and reusable RDL design blocks: Design tools featuring comprehensive library systems for storing and managing reusable redistribution layer components and templates. These systems maintain databases of verified RDL patterns, standard cell configurations, and design building blocks. The library approach accelerates design cycles by enabling designers to leverage proven solutions and maintain consistency across multiple projects.

02 Design rule checking and verification for RDL structures

Tools that perform comprehensive design rule checking specifically tailored for redistribution layer geometries and constraints. These verification systems validate spacing, width, via placement, and layer-to-layer alignment requirements. The tools identify potential manufacturing issues early in the design process and ensure compliance with foundry specifications and electrical requirements.Expand Specific Solutions03 3D visualization and modeling of redistribution layer architectures

Design tools providing three-dimensional visualization capabilities for complex redistribution layer structures. These systems enable designers to view and manipulate multi-layer RDL configurations, analyze cross-sectional views, and detect potential conflicts. The visualization aids in understanding spatial relationships and facilitates communication between design and manufacturing teams.Expand Specific Solutions04 Electrical simulation and analysis for RDL performance

Simulation tools that model electrical characteristics of redistribution layer designs including resistance, capacitance, and inductance. These tools perform signal integrity analysis, power distribution network simulation, and thermal analysis. The electrical modeling helps optimize performance parameters and predict behavior under various operating conditions before physical implementation.Expand Specific Solutions05 Library management and template generation for RDL components

Design tools featuring comprehensive libraries of pre-designed redistribution layer components and parametric template generation capabilities. These systems store reusable design elements such as standard via patterns, pad configurations, and routing templates. The library-based approach accelerates design cycles by enabling rapid assembly of proven components while maintaining consistency across multiple projects.Expand Specific Solutions

Key Players in PCB Design Tool Industry

The PCB redistribution layer design tool market represents a mature segment within the broader electronic design automation (EDA) industry, currently valued at several billion dollars and experiencing steady growth driven by increasing semiconductor complexity and miniaturization demands. The competitive landscape is dominated by established EDA giants like Cadence Design Systems and Siemens Industry Software, who offer comprehensive layout solutions with advanced redistribution layer capabilities. Technology maturity varies significantly across players - while Cadence and Siemens provide production-proven tools with decades of development, specialized companies like AnaGlobe Technology focus on niche automatic IC layout solutions. Manufacturing leaders including Taiwan Semiconductor Manufacturing Company, Applied Materials, and Micron Technology drive tool requirements through their advanced packaging needs, while system integrators like Huawei, Hon Hai Precision, and Inventec influence market demand through their complex PCB design requirements for consumer electronics and enterprise systems.

Applied Materials, Inc.

Technical Solution: Applied Materials focuses on manufacturing process solutions for redistribution layer fabrication rather than design tools. Their expertise lies in advanced lithography and deposition equipment used in the physical creation of redistribution layers in semiconductor packaging. While they don't provide PCB layout design software, their process development kits and design-for-manufacturing guidelines significantly influence redistribution layer design rules and constraints. Their collaboration with EDA vendors ensures that design tools incorporate manufacturability considerations specific to their advanced packaging processes, particularly for fan-out wafer-level packaging applications.

Strengths: Deep manufacturing process expertise and strong industry partnerships. Weaknesses: Limited direct design tool offerings, primarily focused on manufacturing equipment.

Siemens Industry Software, Inc.

Technical Solution: Siemens provides comprehensive PCB design solutions through their Mentor Graphics portfolio, including advanced redistribution layer design tools integrated within their Xpedition and PADS platforms. Their tools feature automated routing algorithms specifically optimized for high-density interconnect (HDI) designs, supporting complex via structures and microvias essential for redistribution layers. The software includes advanced constraint management systems that ensure signal integrity and power delivery optimization across multiple redistribution layers, with built-in design rule checking (DRC) and electrical rule checking (ERC) capabilities tailored for advanced packaging applications.

Strengths: Industry-leading signal integrity analysis and comprehensive constraint management. Weaknesses: High licensing costs and steep learning curve for new users.

Core Innovations in PCB Layout Automation

Layout design of multilayer printed circuit board

PatentInactiveUS20080072204A1

Innovation

- Implementing an EBG structure only on the linear transmission path between ports of integrated circuits on the power or ground layer of a multilayer PCB, while maintaining the rest of the layer as a plain, thereby reducing self-impedance and transfer-impedance.

Current redistribution in a printed circuit board

PatentActiveUS20200107452A1

Innovation

- The implementation of a power plane layer with discontinuous patterns of conductive material, such as hatched, directional, or slot patterns, to selectively steer current away from overutilized vias and towards underutilized ones, creating varying resistances that redistribute current flow and alleviate current density issues.

Industry Standards for PCB Design Tools

The PCB design industry operates under a comprehensive framework of international and regional standards that govern tool development, functionality, and interoperability. The Institute for Printed Circuits (IPC) serves as the primary standards organization, establishing fundamental guidelines through IPC-2221 for generic PCB design requirements and IPC-2222 for sectional design standards. These standards define essential parameters including trace width calculations, via specifications, layer stackup requirements, and design rule constraints that all professional PCB design tools must support.

IEEE standards complement IPC guidelines by addressing electronic design automation (EDA) tool interoperability and data exchange protocols. IEEE 1076 (VHDL) and IEEE 1364 (Verilog) establish hardware description language standards, while IEEE 1149.1 defines boundary scan testing requirements that influence tool-based testability features. The JEDEC organization contributes component packaging standards that directly impact how design tools handle component libraries and footprint generation for redistribution layer applications.

International standards such as ISO 9001 quality management systems and ISO 14001 environmental management standards influence tool development processes and certification requirements. Regional standards including EN 61188 (European) and JIS C 5012 (Japanese) provide additional compliance frameworks that global PCB design tools must accommodate. These standards ensure consistent design practices across different geographical markets and regulatory environments.

Tool certification processes require compliance with electromagnetic compatibility (EMC) standards such as IEC 61000 series, which affects how design tools implement signal integrity analysis and electromagnetic interference mitigation features. Safety standards including IEC 61010 for electrical equipment influence tool-based safety analysis capabilities and automated design rule checking functions.

The emergence of Industry 4.0 and IoT applications has driven the development of new standards for high-density interconnect (HDI) designs and advanced packaging technologies. Standards organizations continuously update requirements to address evolving technologies such as embedded components, flexible-rigid PCBs, and 3D packaging solutions, ensuring that redistribution layer design tools remain current with industry needs and technological advancement.

IEEE standards complement IPC guidelines by addressing electronic design automation (EDA) tool interoperability and data exchange protocols. IEEE 1076 (VHDL) and IEEE 1364 (Verilog) establish hardware description language standards, while IEEE 1149.1 defines boundary scan testing requirements that influence tool-based testability features. The JEDEC organization contributes component packaging standards that directly impact how design tools handle component libraries and footprint generation for redistribution layer applications.

International standards such as ISO 9001 quality management systems and ISO 14001 environmental management standards influence tool development processes and certification requirements. Regional standards including EN 61188 (European) and JIS C 5012 (Japanese) provide additional compliance frameworks that global PCB design tools must accommodate. These standards ensure consistent design practices across different geographical markets and regulatory environments.

Tool certification processes require compliance with electromagnetic compatibility (EMC) standards such as IEC 61000 series, which affects how design tools implement signal integrity analysis and electromagnetic interference mitigation features. Safety standards including IEC 61010 for electrical equipment influence tool-based safety analysis capabilities and automated design rule checking functions.

The emergence of Industry 4.0 and IoT applications has driven the development of new standards for high-density interconnect (HDI) designs and advanced packaging technologies. Standards organizations continuously update requirements to address evolving technologies such as embedded components, flexible-rigid PCBs, and 3D packaging solutions, ensuring that redistribution layer design tools remain current with industry needs and technological advancement.

Cost-Benefit Analysis of Tool Selection

The cost-benefit analysis of redistribution layer design tool selection requires a comprehensive evaluation framework that balances initial investment against long-term operational advantages. Organizations must consider both direct costs, including software licensing fees, hardware requirements, and training expenses, alongside indirect costs such as implementation time, workflow disruption, and ongoing maintenance requirements.

Initial acquisition costs vary significantly across tool categories, with enterprise-level solutions typically requiring substantial upfront investments ranging from tens of thousands to hundreds of thousands of dollars annually. However, these premium tools often provide advanced automation capabilities, comprehensive design rule checking, and sophisticated optimization algorithms that can substantially reduce design cycle times and minimize costly redesign iterations.

The quantifiable benefits of advanced redistribution layer design tools manifest through improved design efficiency, reduced time-to-market, and enhanced product quality. Automated routing capabilities can decrease manual design time by 40-60%, while advanced simulation features help identify potential issues early in the design process, preventing expensive manufacturing defects and reducing prototype iterations.

Return on investment calculations must account for productivity gains achieved through streamlined workflows and reduced design errors. Organizations typically observe payback periods of 12-18 months for comprehensive tool suites, with ongoing benefits including improved designer productivity, standardized design processes, and enhanced collaboration capabilities across distributed teams.

Risk mitigation represents another critical benefit dimension, as sophisticated tools provide robust design validation, comprehensive documentation generation, and version control capabilities that reduce project risks and ensure regulatory compliance. The cost of design failures in high-volume production scenarios often exceeds tool investment costs by orders of magnitude, making quality assurance features particularly valuable.

Long-term strategic considerations include tool scalability, vendor stability, and technology roadmap alignment. While lower-cost alternatives may appear attractive initially, limitations in handling complex designs or integration with existing workflows can result in higher total cost of ownership over multi-year periods, necessitating careful evaluation of future requirements and growth projections.

Initial acquisition costs vary significantly across tool categories, with enterprise-level solutions typically requiring substantial upfront investments ranging from tens of thousands to hundreds of thousands of dollars annually. However, these premium tools often provide advanced automation capabilities, comprehensive design rule checking, and sophisticated optimization algorithms that can substantially reduce design cycle times and minimize costly redesign iterations.

The quantifiable benefits of advanced redistribution layer design tools manifest through improved design efficiency, reduced time-to-market, and enhanced product quality. Automated routing capabilities can decrease manual design time by 40-60%, while advanced simulation features help identify potential issues early in the design process, preventing expensive manufacturing defects and reducing prototype iterations.

Return on investment calculations must account for productivity gains achieved through streamlined workflows and reduced design errors. Organizations typically observe payback periods of 12-18 months for comprehensive tool suites, with ongoing benefits including improved designer productivity, standardized design processes, and enhanced collaboration capabilities across distributed teams.

Risk mitigation represents another critical benefit dimension, as sophisticated tools provide robust design validation, comprehensive documentation generation, and version control capabilities that reduce project risks and ensure regulatory compliance. The cost of design failures in high-volume production scenarios often exceeds tool investment costs by orders of magnitude, making quality assurance features particularly valuable.

Long-term strategic considerations include tool scalability, vendor stability, and technology roadmap alignment. While lower-cost alternatives may appear attractive initially, limitations in handling complex designs or integration with existing workflows can result in higher total cost of ownership over multi-year periods, necessitating careful evaluation of future requirements and growth projections.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!