3D IC Packaging: Stacking Dies for Higher Performance and Lower Power

JUN 27, 2025 |

In the ever-evolving landscape of semiconductor technology, the push for greater performance, reduced power consumption, and enhanced functionality continues to drive innovation. One of the most promising advancements in this realm is 3D Integrated Circuit (IC) packaging. By stacking die vertically, 3D IC packaging offers a compelling solution to the limitations of traditional planar semiconductor design, providing a path to more powerful, energy-efficient, and compact electronic devices.

Understanding 3D IC Packaging

The concept of 3D IC packaging involves the vertical integration of multiple semiconductor dies within a single package. Unlike the conventional 2D IC design, where dies are placed side by side on a flat substrate, 3D IC technology stacks dies on top of each other, interconnected with through-silicon vias (TSVs) and other advanced interconnect technologies. This approach not only conserves space but also significantly shortens the distance for signal travel, leading to reduced latency and improved performance.

Advantages of Die Stacking

One of the most significant benefits of 3D IC packaging is the enhancement of device performance. The reduced distance between dies leads to faster signal transmission, resulting in quicker processing speeds and improved overall performance. Additionally, by minimizing the space required for individual components, more functionality can be packed into a smaller footprint, making devices more compact and versatile.

Moreover, 3D IC packaging contributes to lower power consumption, a critical factor in the design of modern electronic devices. The shorter interconnect paths reduce the power required to drive signals between components. This reduction in power consumption not only extends battery life in portable applications but also helps in managing heat dissipation more effectively, a common challenge in densely packed circuits.

Challenges in 3D IC Packaging

Despite its advantages, 3D IC packaging is not without its challenges. The manufacturing process is more complex and requires high precision to ensure that the vertically stacked dies are perfectly aligned and interconnected. The inclusion of TSVs introduces additional considerations, such as managing thermal expansion and stress within the package.

Thermal management is another significant challenge, as the stacked dies generate heat that must be efficiently dissipated to prevent damage and ensure reliable operation. Advanced cooling solutions and innovative thermal interface materials are often necessary to address these concerns.

Applications and Future Prospects

3D IC packaging is poised to revolutionize various sectors, from consumer electronics to high-performance computing and telecommunications. In smartphones and tablets, 3D ICs enable the integration of more features and capabilities without increasing device size. In data centers and servers, the technology provides the opportunity to enhance processing capabilities while reducing energy consumption and space requirements.

Looking forward, the prospects for 3D IC packaging are promising. As the technology continues to mature, further reductions in costs and improvements in reliability are expected. Research into new materials and cooling technologies will also play a crucial role in overcoming current limitations, paving the way for even broader adoption.

Conclusion

3D IC packaging represents a significant leap forward in semiconductor design, offering tangible benefits in performance, power efficiency, and miniaturization. While challenges remain, the potential of this technology to transform the electronics industry is undeniable. As advancements continue, 3D IC packaging is set to play a pivotal role in meeting the growing demands for more capable and energy-efficient electronic devices.

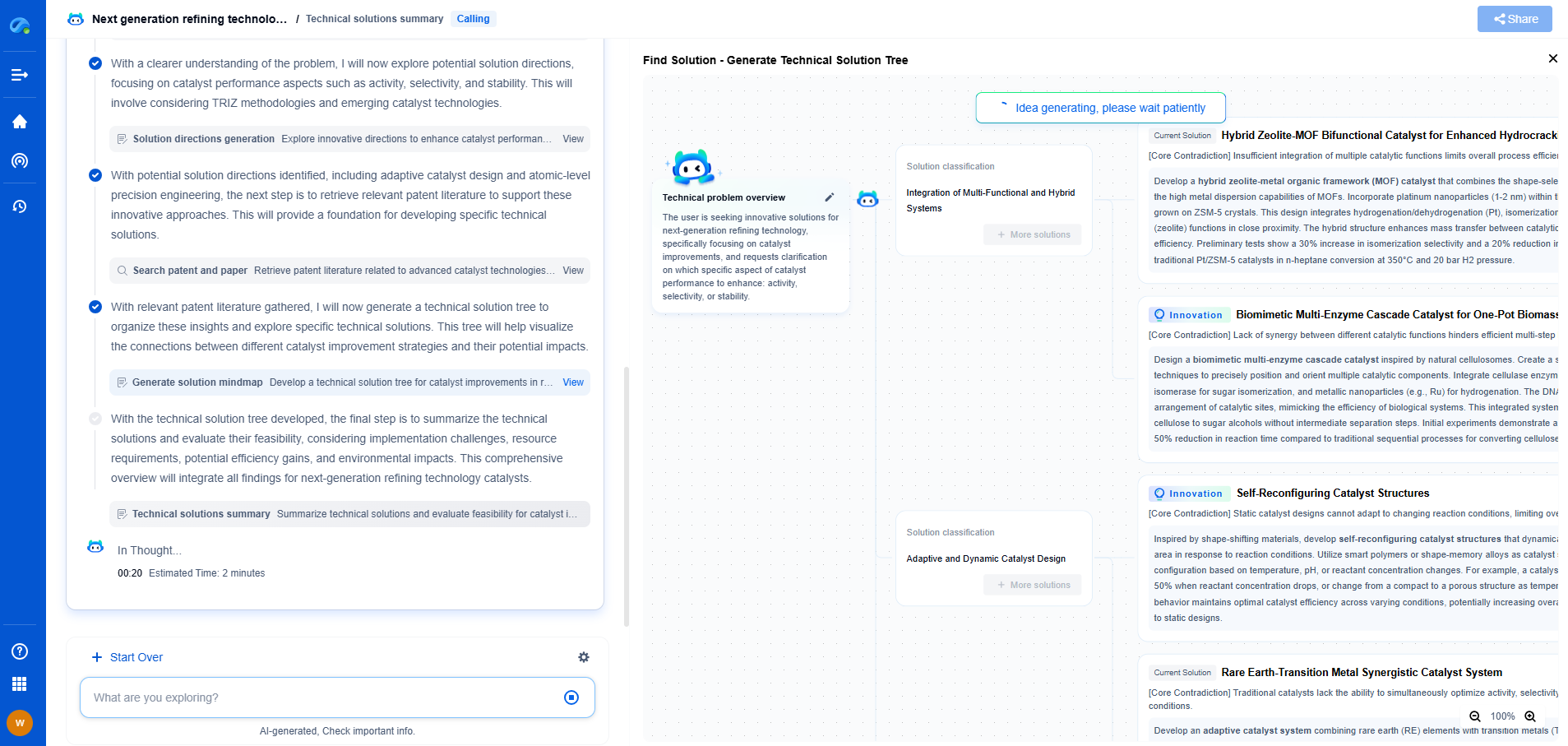

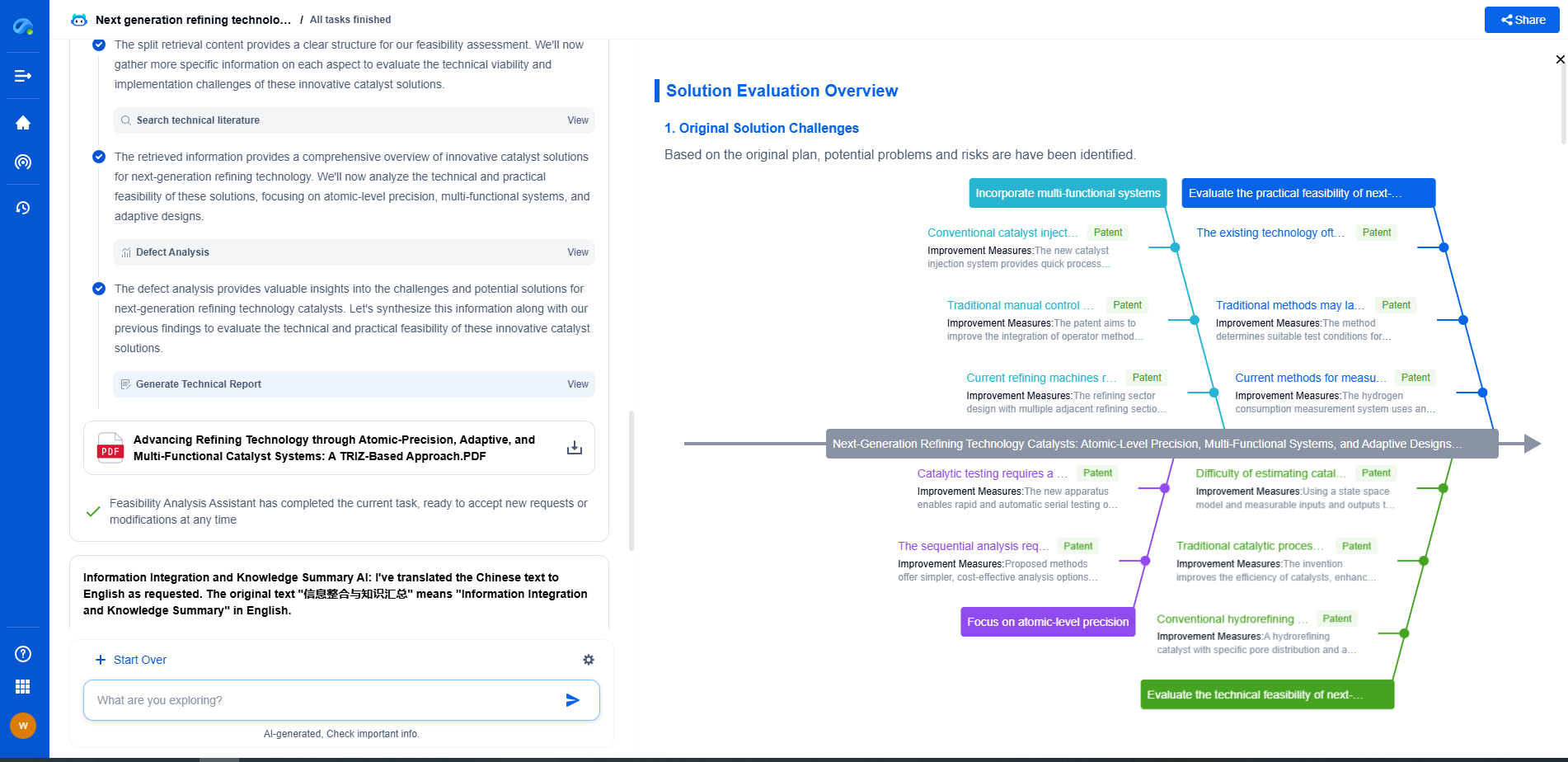

Empower Your Breakthroughs in Basic Electric Components with Patsnap Eureka

From resistors, capacitors, and inductors to fuses, connectors, superconductors, and nano-scale materials—basic electric elements may be the building blocks of modern electronics, but the innovation behind them is anything but simple. As device miniaturization accelerates and materials science pushes new frontiers, R&D and IP teams face increasing complexity in staying on top of technical advancements, patent activity, and competitive landscapes.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

🔧 Whether you’re optimizing energy storage, improving thermal resistance, or creating the next leap in circuit efficiency, Patsnap Eureka is your AI copilot for high-efficiency, high-precision R&D and IP strategy.

👉 Experience how Patsnap Eureka can revolutionize your R&D and IP strategy. Request a demo today and power up your next breakthrough.