Bridging Defect Reduction: Resist Reflow Process Optimization

JUL 28, 2025 |

In the ever-evolving landscape of semiconductor manufacturing, one of the most critical challenges lies in optimizing processes to minimize defects and maximize yield. As technology nodes continue to shrink, the complexity of photolithography processes has increased significantly. One emerging area of focus is the optimization of the resist reflow process, which plays a crucial role in defect reduction. This article explores the intricacies of the resist reflow process, its impact on defect reduction, and the strategies for optimizing this vital step in semiconductor fabrication.

Understanding Resist Reflow

The resist reflow process involves thermally treating a photoresist film to modify its shape and properties, thereby enhancing the lithographic performance. This step is particularly useful in improving critical dimension (CD) uniformity, line edge roughness, and resolution of the features on a wafer. However, the resist reflow process is delicate, and without careful optimization, it can introduce defects such as bridging, pinching, or footing. Therefore, understanding and controlling the parameters of this process is crucial for achieving high yields and reliable device performance.

Challenges in Defect Reduction

Defect reduction in semiconductor manufacturing is paramount, as defects can lead to device failures and decreased performance. In the resist reflow process, several factors can contribute to defect formation, including temperature fluctuations, resist thickness variations, and surface interactions. Bridging defects, where resist between adjacent features connects unintentionally, are particularly problematic as they can cause short circuits in integrated circuits. Addressing these challenges requires a comprehensive approach that combines precise process control, advanced metrology, and robust simulation tools.

Optimizing the Resist Reflow Process

1. Precise Temperature Control

Temperature is a critical parameter in the resist reflow process. Optimizing the temperature profile during reflow can significantly impact defect reduction. Precise temperature control ensures that the resist flows adequately without over-reflowing, which can lead to bridging defects. Incorporating advanced thermal management systems and real-time monitoring can help achieve the desired temperature consistency across the wafer.

2. Uniform Resist Thickness

Uniformity in resist thickness is vital for consistent reflow results. Variations in thickness can lead to uneven reflow, resulting in defects. Implementing advanced coating techniques and in-situ thickness measurement systems can ensure that the resist layer is uniform across the wafer. This uniformity aids in achieving consistent reflow behavior and reduces the risk of bridging defects.

3. Surface Treatment and Materials

The interaction between the resist and the underlying substrate plays a significant role in the reflow process. Surface treatments can modify the adhesion properties, impacting the resist flow. Utilizing anti-reflective coatings and surface conditioning techniques can enhance the reflow characteristics, minimizing defect formation. Additionally, selecting resist materials with favorable flow properties and thermal stability can further optimize the reflow process.

4. Simulation and Modeling

Leveraging advanced simulation and modeling tools can provide valuable insights into the resist reflow process. By simulating different process conditions, manufacturers can predict defect formation and identify optimal parameters for reflow. These tools enable a deeper understanding of the complex interactions within the process, facilitating targeted adjustments and improvements.

Conclusion

In the quest for higher yields and reduced defects in semiconductor manufacturing, optimizing the resist reflow process stands as a pivotal strategy. Through precise temperature control, uniform resist thickness, surface treatment, and advanced simulation, manufacturers can significantly reduce bridging and other reflow-related defects. As technology continues to advance, ongoing research and innovation in resist materials and process optimization will be critical in meeting the demands of next-generation semiconductor devices. By bridging the gap between defect reduction and resist reflow process optimization, the industry can continue to push the boundaries of what is possible in semiconductor fabrication.

As photolithography continues to push the boundaries of nanoscale patterning, from EUV and DUV advancements to multi-patterning and maskless lithography, innovation cycles are accelerating—and the IP landscape is becoming more complex than ever.

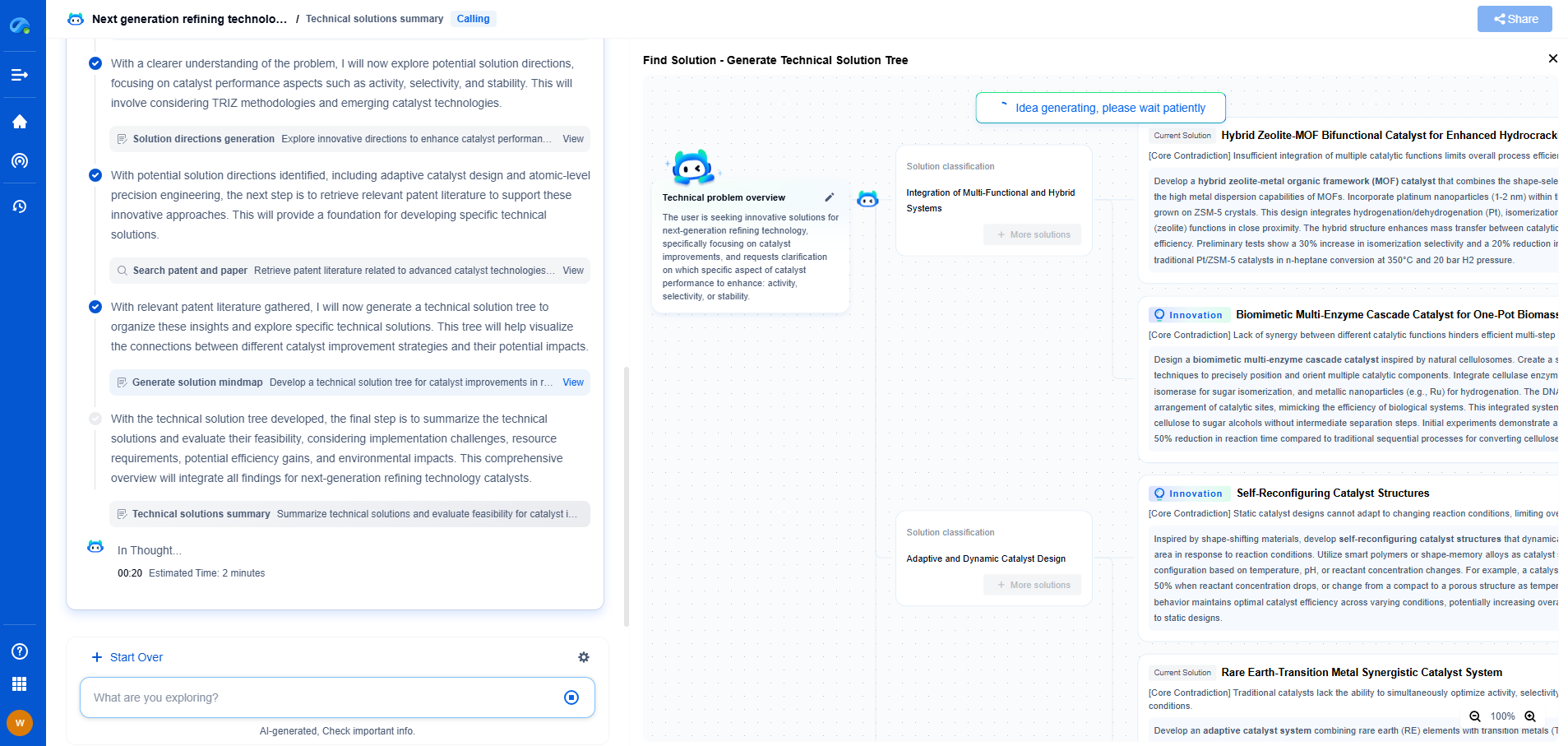

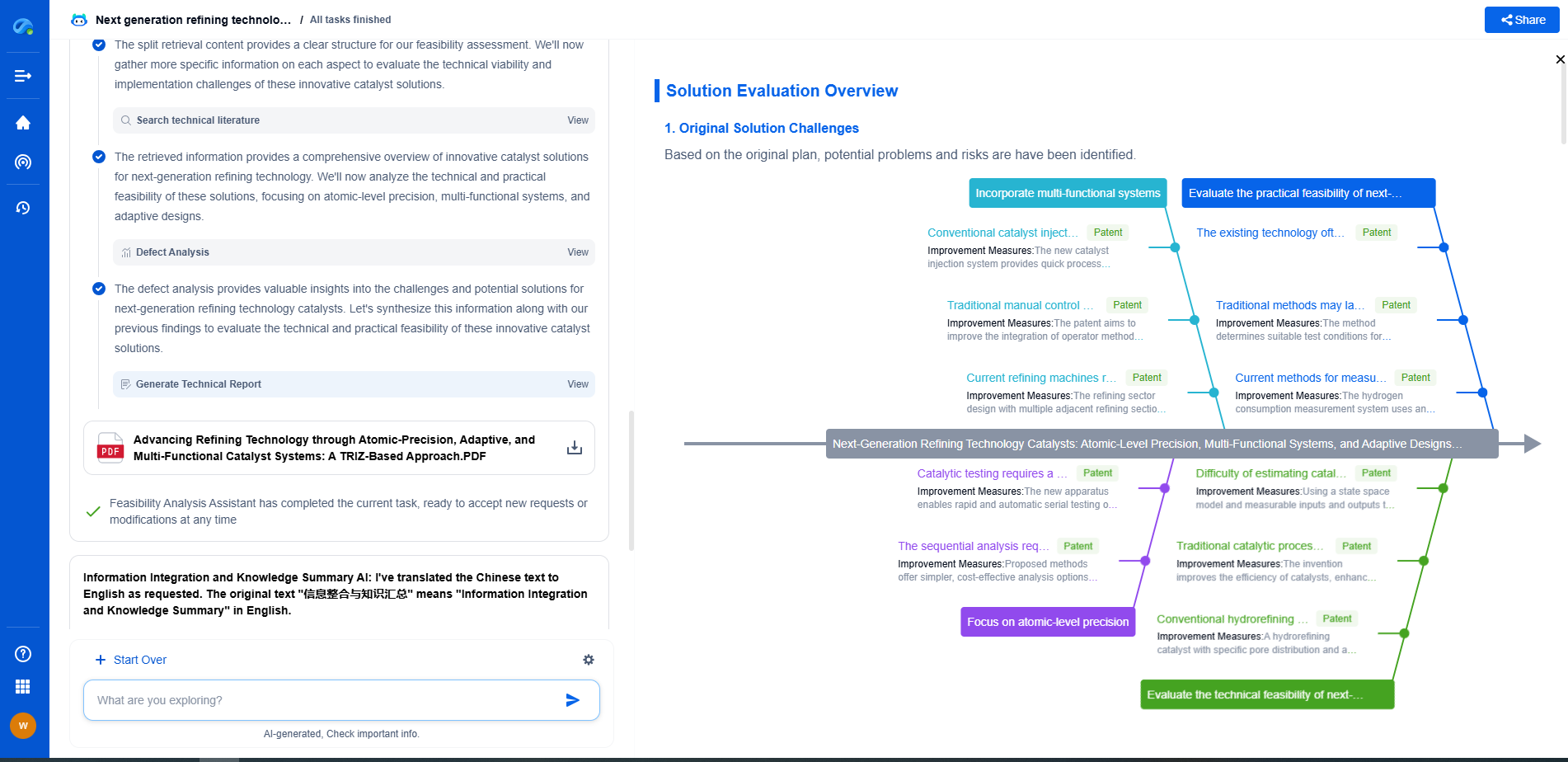

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Whether you're optimizing lithography depth of focus or exploring new materials for sub-3nm nodes, Patsnap Eureka empowers you to make smarter decisions, faster—combining AI efficiency with domain-specific insight.

💡 Start your free trial today and see how Eureka transforms how you discover, evaluate, and act on innovation in photolithography—from idea to impact.

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com