Capacitance-Voltage (C-V) Profiling: Analyzing Semiconductor Interfaces

JUL 9, 2025 |

Capacitance-voltage (C-V) profiling is a pivotal analytical technique utilized in the field of semiconductor physics to investigate the electronic properties of semiconductor interfaces. This method offers invaluable insights into the interface quality, doping profiles, and potential distributions. Given the ever-evolving complexity of semiconductor devices, mastering C-V profiling is essential for both researchers and engineers involved in semiconductor design and fabrication.

The Basics of Capacitance-Voltage Profiling

At its core, C-V profiling involves measuring the capacitance of a semiconductor device as a function of the applied voltage. Typically, this is performed on metal-oxide-semiconductor (MOS) structures, where the capacitance of the oxide layer varies with the applied voltage due to changes in the depletion region width. The C-V curve provides critical information about the semiconductor, including the doping concentration, oxide thickness, and interface trap density.

Understanding the C-V Curve

Analyzing the C-V curve is fundamental to deciphering semiconductor properties. In an ideal scenario, the C-V curve exhibits distinct regions corresponding to accumulation, depletion, and inversion. The accumulation region occurs when a positive voltage attracts majority carriers, increasing capacitance. The depletion region, identified by a decrease in capacitance, reflects the widening of the depletion layer as the applied voltage increases. Lastly, the inversion region, significant in MOSFET applications, occurs when a further increase in voltage leads to an inversion layer forming at the semiconductor surface, creating a high capacitance.

Applications in Semiconductor Interfaces

C-V profiling is instrumental in characterizing semiconductor interfaces. By analyzing the C-V measurements, one can infer the quality of the oxide layer and the presence of interface traps. Interface trap densities can be determined by observing deviations from the ideal C-V characteristics, providing insights into defects and impurities at the interface. This information is crucial for optimizing device performance, particularly in advanced semiconductor technologies such as FinFETs and GaN-based devices.

Advanced Techniques in C-V Profiling

While traditional C-V measurements offer substantial information, advanced techniques can yield even deeper insights. High-frequency C-V measurements minimize the effects of interface traps, offering a clearer picture of the semiconductor's intrinsic properties. Additionally, deep-level transient spectroscopy (DLTS) can be employed in conjunction with C-V profiling to identify and quantify deep-level defects within the semiconductor.

Challenges and Limitations

Despite its efficacy, C-V profiling is not without challenges. The technique is sensitive to measurement conditions, requiring meticulous control of temperature and measurement frequency to ensure accurate results. Furthermore, interpreting C-V curves for complex structures, such as heterojunctions, can be challenging due to their intricate electronic properties. Overcoming these challenges necessitates a thorough understanding of semiconductor physics and a careful experimental setup.

Conclusion

Capacitance-voltage profiling remains a cornerstone technique for analyzing semiconductor interfaces, offering a wealth of information about the electronic properties and quality of semiconductor devices. As semiconductor technology continues to advance, the importance of C-V profiling in research and development will only grow, necessitating ongoing exploration and refinement of this powerful analytical tool. By mastering C-V profiling, researchers and engineers can significantly contribute to the innovation and optimization of future semiconductor technologies.

Navigating the evolving world of electrical measurement—from high-precision signal integrity to advanced test protocols like BERT or TDR—demands more than just expertise; it demands smart tools.

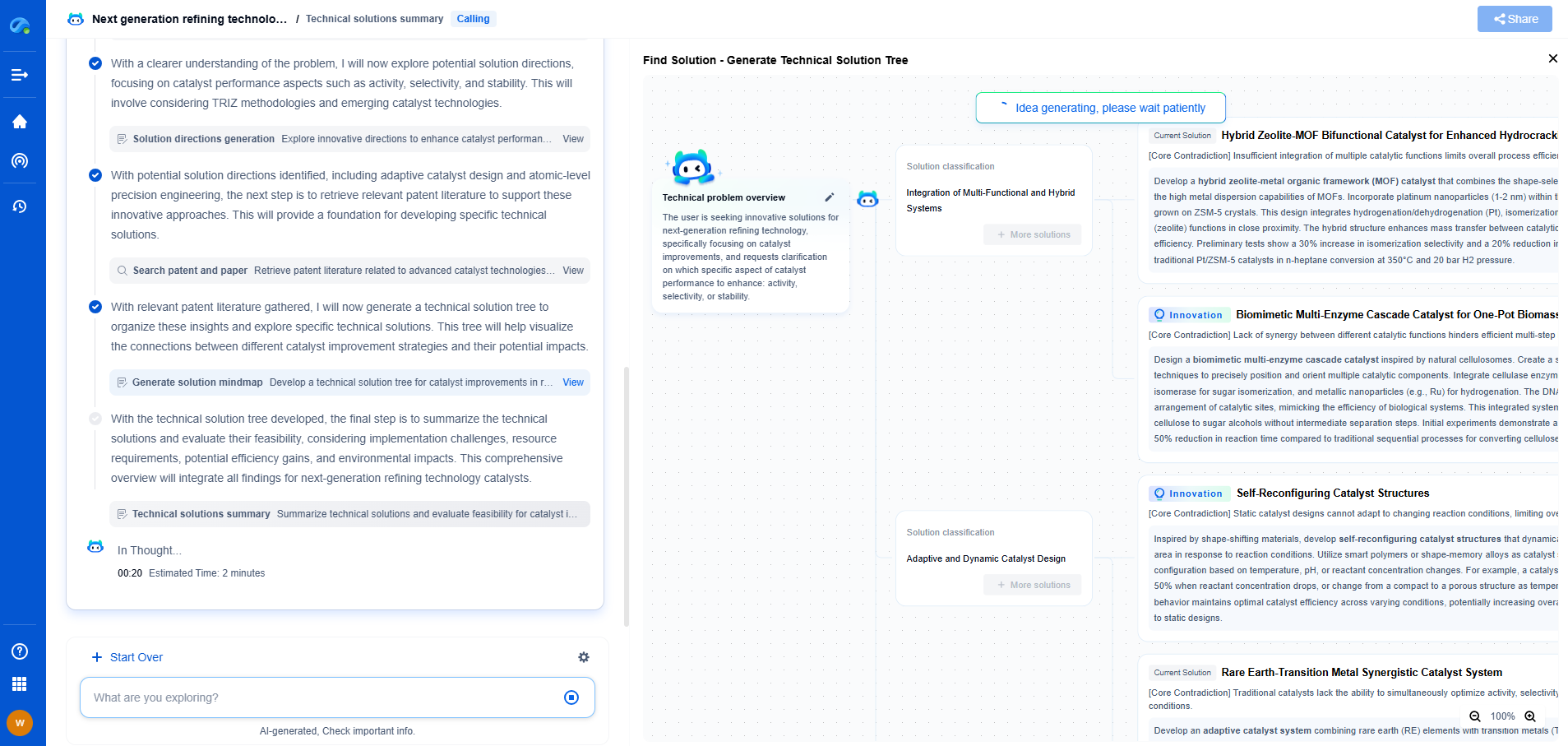

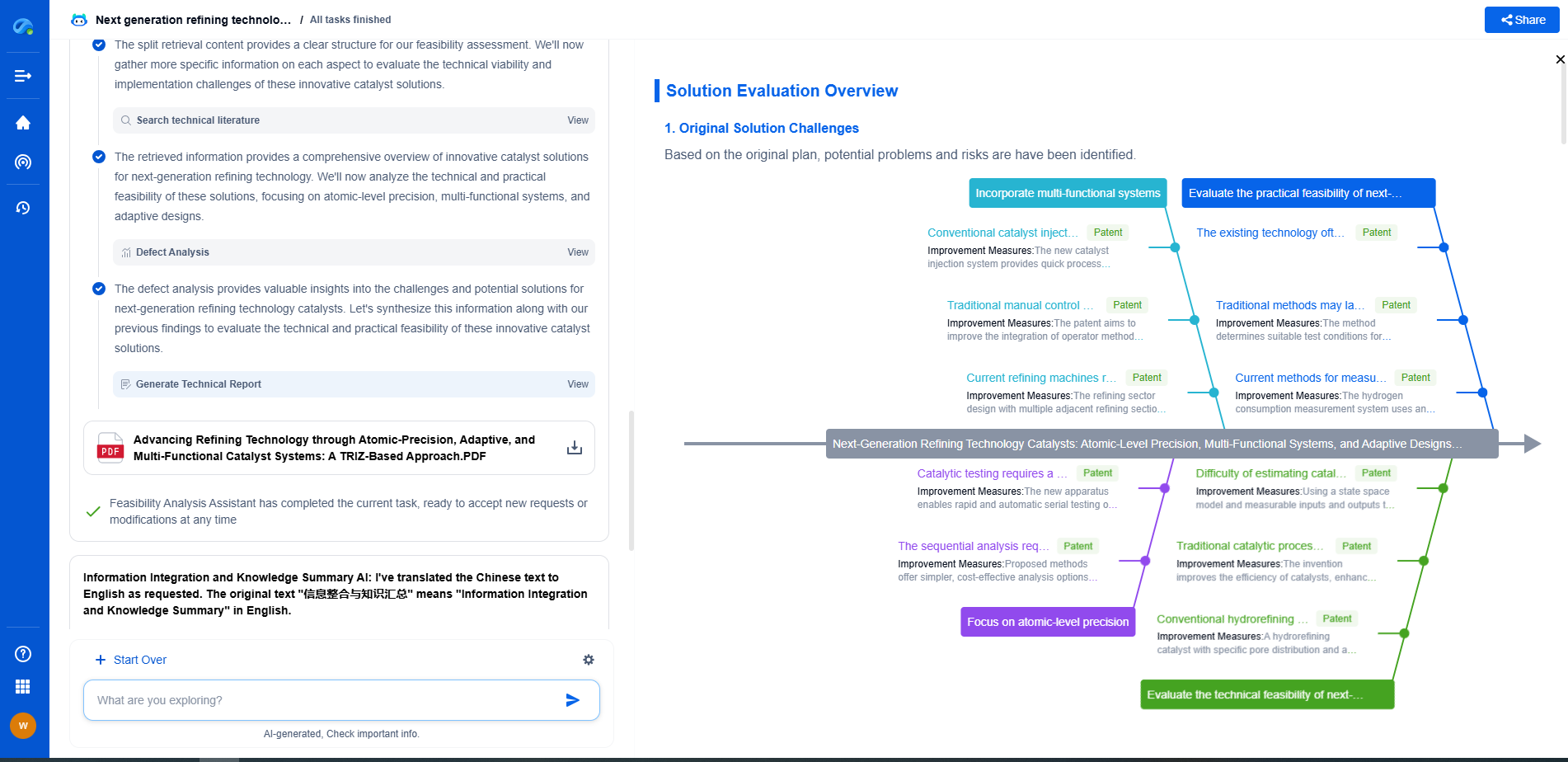

Patsnap Eureka empowers you to keep up—by turning complex patent data, technical parameters, and industry signals into actionable insight. It’s your AI partner for exploring what’s next in test, measurement, and electrical diagnostics.

💡 Try Patsnap Eureka for free and see how it transforms the way you work with electrical measurement technologies.