CTE Mismatch in PCBs: Causes and Mitigation Strategies

JUN 27, 2025 |

Coefficient of Thermal Expansion (CTE) mismatch is a critical aspect in the design and manufacturing of printed circuit boards (PCBs). CTE is the measure of how much a material expands or contracts when exposed to temperature changes. In the context of PCBs, mismatches in CTE between different materials can lead to mechanical stress, warping, and ultimately, failure in electronic components. Understanding the causes and implementing effective mitigation strategies is essential for ensuring the reliability and longevity of PCBs.

Causes of CTE Mismatch

CTE mismatch is primarily caused by the use of multiple materials within a PCB, each with different thermal expansion properties. The most common materials found in PCBs include substrates like FR-4, copper, solder, and various dielectric materials. Each has its own CTE value, and when these materials are bonded together, even slight differences in their thermal expansion rates can result in stress.

Design complexity also contributes to CTE mismatch. As electronic devices become more compact and sophisticated, PCBs often incorporate multilayer constructions. These layers might include diverse materials, further complicating the CTE dynamics. Additionally, varying thicknesses and orientations can exacerbate the mismatch, resulting in differential stress across the board.

Temperature fluctuations during operation are another key factor. Electronic components generate heat during use, leading to constant expansion and contraction cycles. If the different materials expand at varying rates, it can lead to mechanical strain and potential delamination or cracking.

Mitigation Strategies

To address CTE mismatch effectively, several strategies can be employed, ranging from material selection to advanced design techniques.

Material Selection

Choosing materials with compatible CTE values is the first line of defense against mismatch. Manufacturers often opt for substrates like high-performance laminates that offer lower CTE values closer to those of copper. Additionally, using materials that can withstand high temperatures without significant expansion, such as ceramics or specific polymers, can help minimize mismatch.

Layered Design and Construction

Designing PCBs with careful consideration of layer stacking and orientation can mitigate CTE mismatch. Techniques such as symmetrical layering ensure that expansion and contraction are uniform across the board, reducing the likelihood of warping or delamination. Using thinner layers or incorporating compliance layers can also absorb expansion stresses.

Thermal Management

Implementing effective thermal management systems can drastically reduce the impact of CTE mismatch. Heat sinks, thermal vias, and advanced cooling systems help dissipate heat, reducing the thermal cycling that exacerbates mismatch issues. Keeping operating temperatures within optimal ranges can limit the expansion and contraction of materials, preserving the integrity of the PCB.

Use of Advanced Materials and Technologies

The electronics industry is continuously developing new materials and technologies to combat CTE mismatch. Innovations such as nano-engineered materials and composite substrates are designed to offer better thermal stability while maintaining electrical performance. Additionally, advanced bonding techniques, including anisotropic conductive films and flexible adhesives, allow for better accommodation of differential expansion without compromising connectivity.

Stress Simulation and Testing

Before full-scale production, conducting stress simulations and testing can identify potential CTE mismatch issues. Using software tools to model thermal expansion and stress distribution in the PCB design phase can help engineers predict problem areas and adjust designs accordingly. Physical testing, such as thermal cycling tests, can validate these models and ensure robustness in real-world applications.

Conclusion

CTE mismatch remains a significant challenge in PCB design and manufacturing, but understanding its causes and implementing strategic mitigation techniques can enhance the reliability and performance of electronic devices. By focusing on material selection, design optimization, thermal management, and leveraging advanced technologies, manufacturers can effectively address CTE mismatch problems, paving the way for more durable and dependable electronic products.

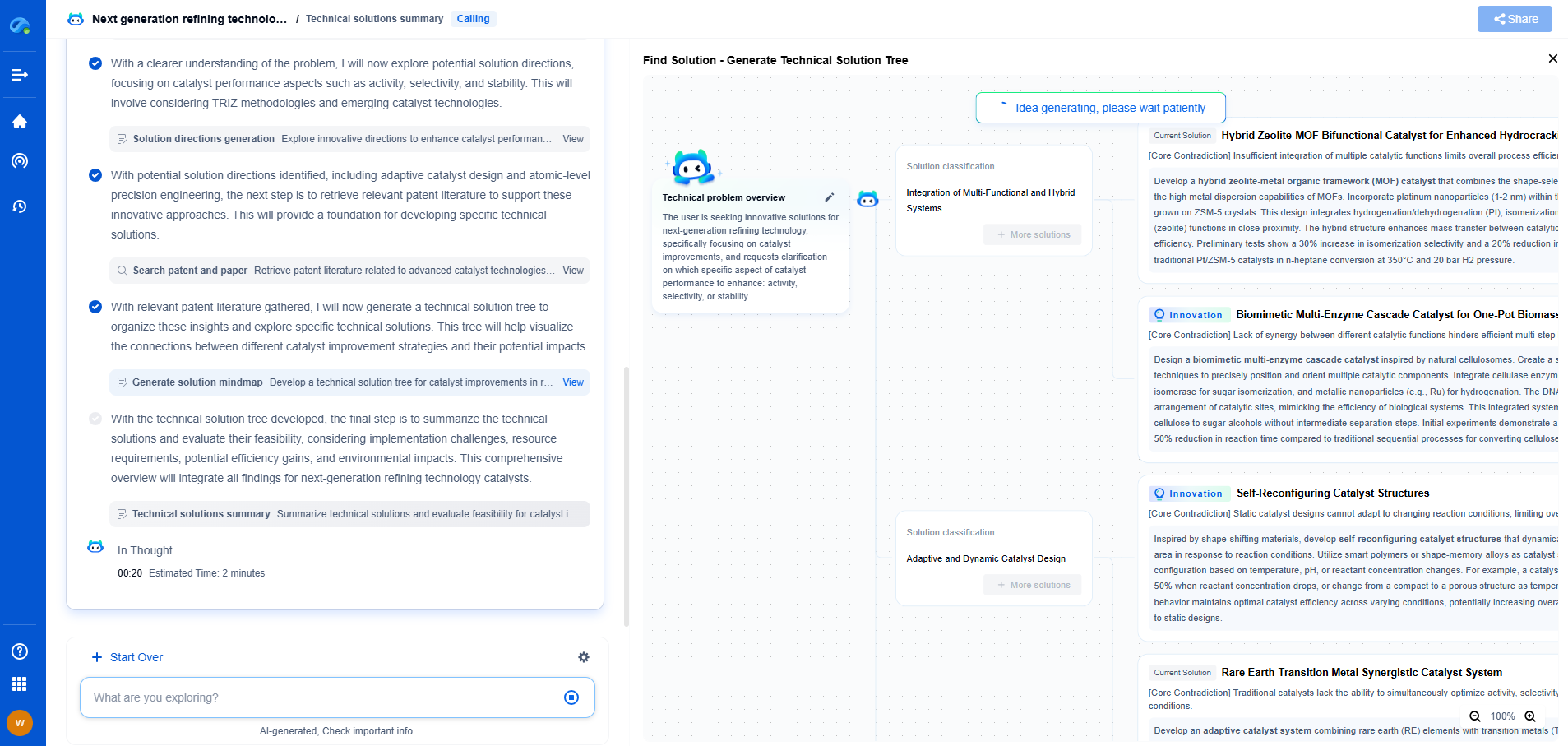

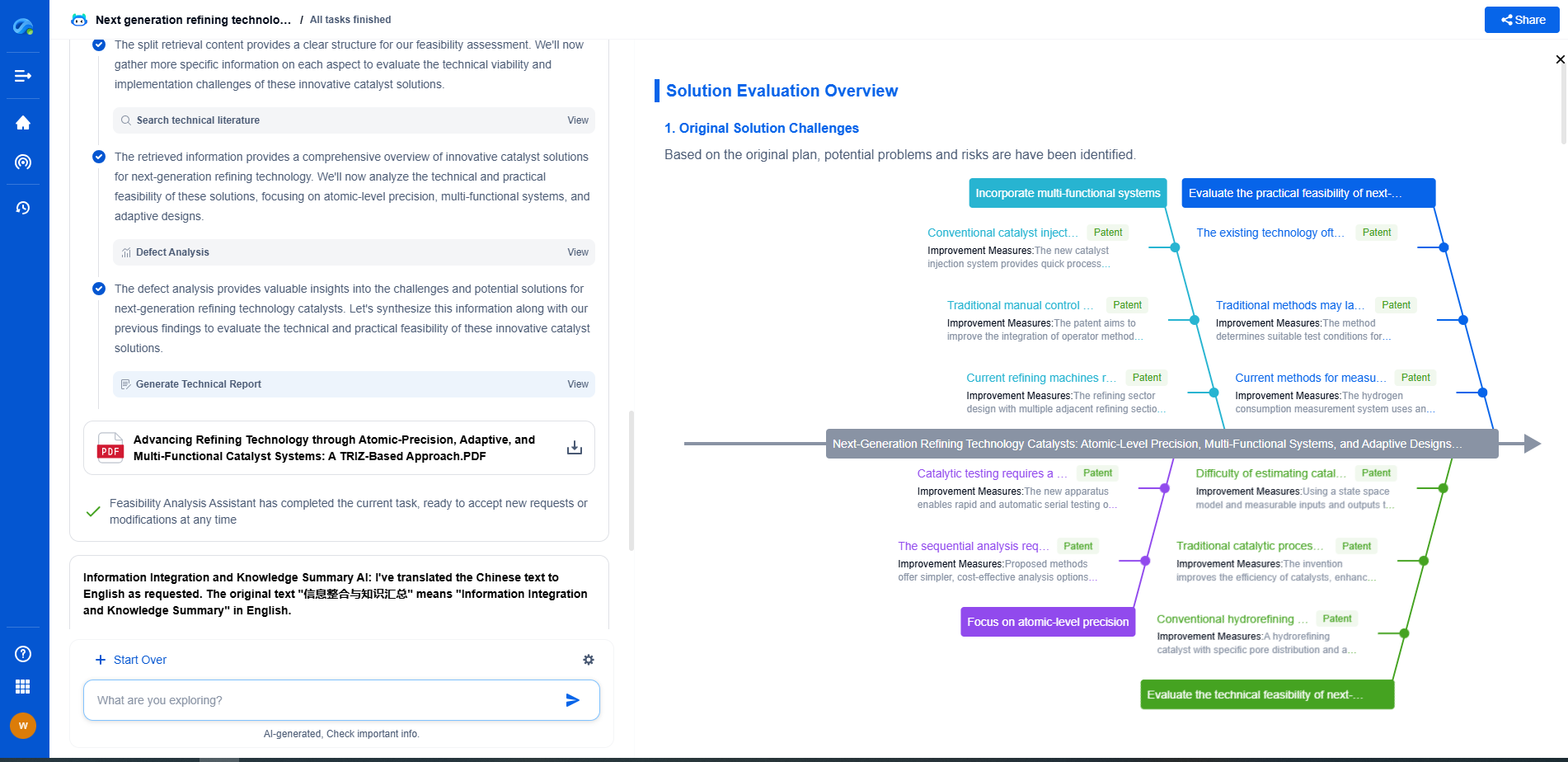

Unlock Next-Gen Innovation in Communication Technology with Patsnap Eureka

The field of communication technology is evolving at breakneck speed—from 5G and satellite systems to next-gen wireless protocols and quantum communications. Staying ahead demands more than just information—it requires strategic insights, real-time patent intelligence, and a deep understanding of technological trajectories.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface. Whether you're optimizing signal processing designs, navigating 3GPP standards, or exploring IP strategies for IoT and 6G networks, Eureka helps you move faster, think deeper, and innovate smarter.

Try Patsnap Eureka today—and see how it can transform the way you work across the entire communication technology innovation lifecycle.

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com