EUV Single Exposure vs DUV Multi-Patterning: LER Differences

JUL 28, 2025 |

As semiconductor technology advances, the demand for smaller, more efficient, and more powerful microchips remains unrelenting. A critical aspect of this advancement is the lithography process, which determines the precision and reliability of integrated circuits. Two prominent methods in the current technological landscape are Extreme Ultraviolet (EUV) lithography and Deep Ultraviolet (DUV) multi-patterning. These approaches differ fundamentally in their methodology, and an essential parameter that emerges from their comparison is Line Edge Roughness (LER). This article explores the differences in LER between EUV single exposure and DUV multi-patterning, and how these differences impact the overall semiconductor manufacturing process.

Understanding Line Edge Roughness (LER)

LER is a measure of the deviation of the edge of a line from its intended path. In semiconductor manufacturing, achieving minimal LER is crucial because it directly affects the performance and reliability of microchips. Higher LER can lead to variations in electrical properties, impacting device performance and yield. Therefore, understanding and controlling LER is a primary focus in lithography.

EUV Single Exposure: A Breakthrough in Precision

EUV lithography represents a significant leap forward in the drive towards smaller feature sizes. Operating at a wavelength of 13.5 nm, EUV allows for single exposure patterning of extremely fine lines, reducing the need for complex multi-patterning techniques. The advantage of having a single exposure lies in its ability to achieve lower LER due to fewer processing steps, which inherently reduces potential sources of roughness.

The inherent shorter wavelength of EUV results in a higher resolution capability, which means the edges of the patterns are more precise and less susceptible to variability. This precision is critical as devices scale down to 7nm and below, where the margin for error becomes increasingly narrow.

DUV Multi-Patterning: An Established Yet Complex Approach

Contrastingly, DUV lithography has been the workhorse of the semiconductor industry for several decades. Operating at wavelengths around 193 nm, DUV does not naturally achieve the same resolution as EUV. To overcome this limitation, the industry has relied on multi-patterning techniques, such as double or quadruple patterning, to achieve smaller feature sizes.

While multi-patterning extends the life of DUV lithography, it adds complexity to the manufacturing process. Each additional patterning step introduces more opportunities for errors and variations, which can increase LER. The cumulative effect of these processes often results in higher LER compared to a single exposure EUV process. The need to align multiple masks precisely adds to the challenge, making it difficult to maintain low LER across all features.

Comparative Analysis: EUV versus DUV

When comparing EUV and DUV in terms of LER, the advantages of EUV become apparent. The reduced need for multiple patterning steps in EUV leads to a cleaner, more precise pattern, with fewer opportunities for edge roughness to develop. Furthermore, the photochemical processes involved in EUV lithography are inherently different from those in DUV, potentially offering improved material properties and less variability.

On the other hand, despite its shortcomings in LER, DUV multi-patterning remains a viable option due to its cost-effectiveness and the extensive existing infrastructure. However, as the industry pushes towards smaller nodes, the pressure to adopt EUV increases due to its ability to produce lower LER and higher precision patterns.

Conclusion

The battle between EUV single exposure and DUV multi-patterning in the realm of semiconductor manufacturing is a nuanced one. While EUV offers significant advantages in terms of reduced LER and process simplicity, DUV continues to hold its ground through established practices and cost efficiencies. Ultimately, the choice between these technologies depends on the specific needs of the manufacturing process, cost considerations, and the desired device performance. As we forge ahead into smaller nodes, the importance of understanding and controlling LER will remain a key factor in the success of next-generation semiconductor technologies.

As photolithography continues to push the boundaries of nanoscale patterning, from EUV and DUV advancements to multi-patterning and maskless lithography, innovation cycles are accelerating—and the IP landscape is becoming more complex than ever.

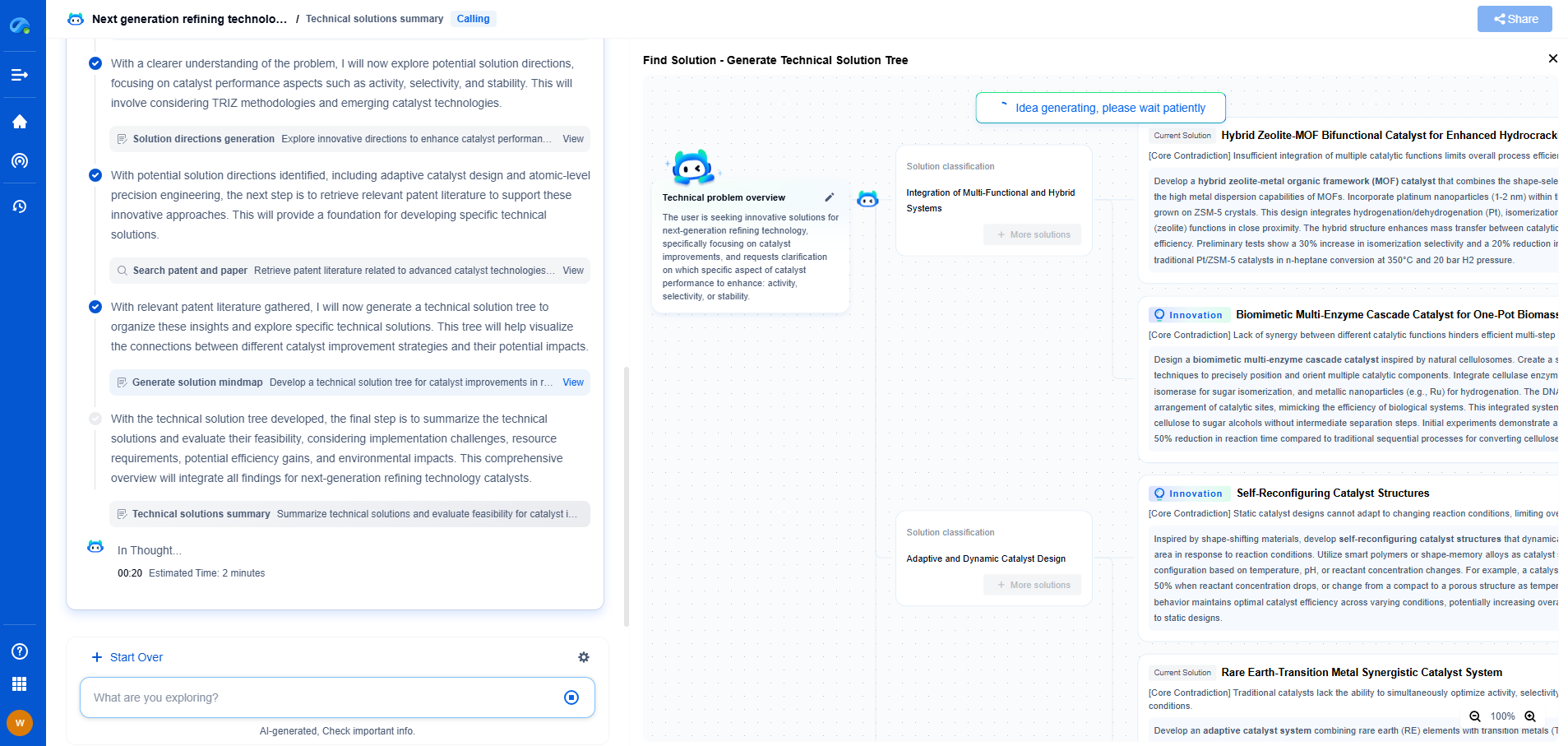

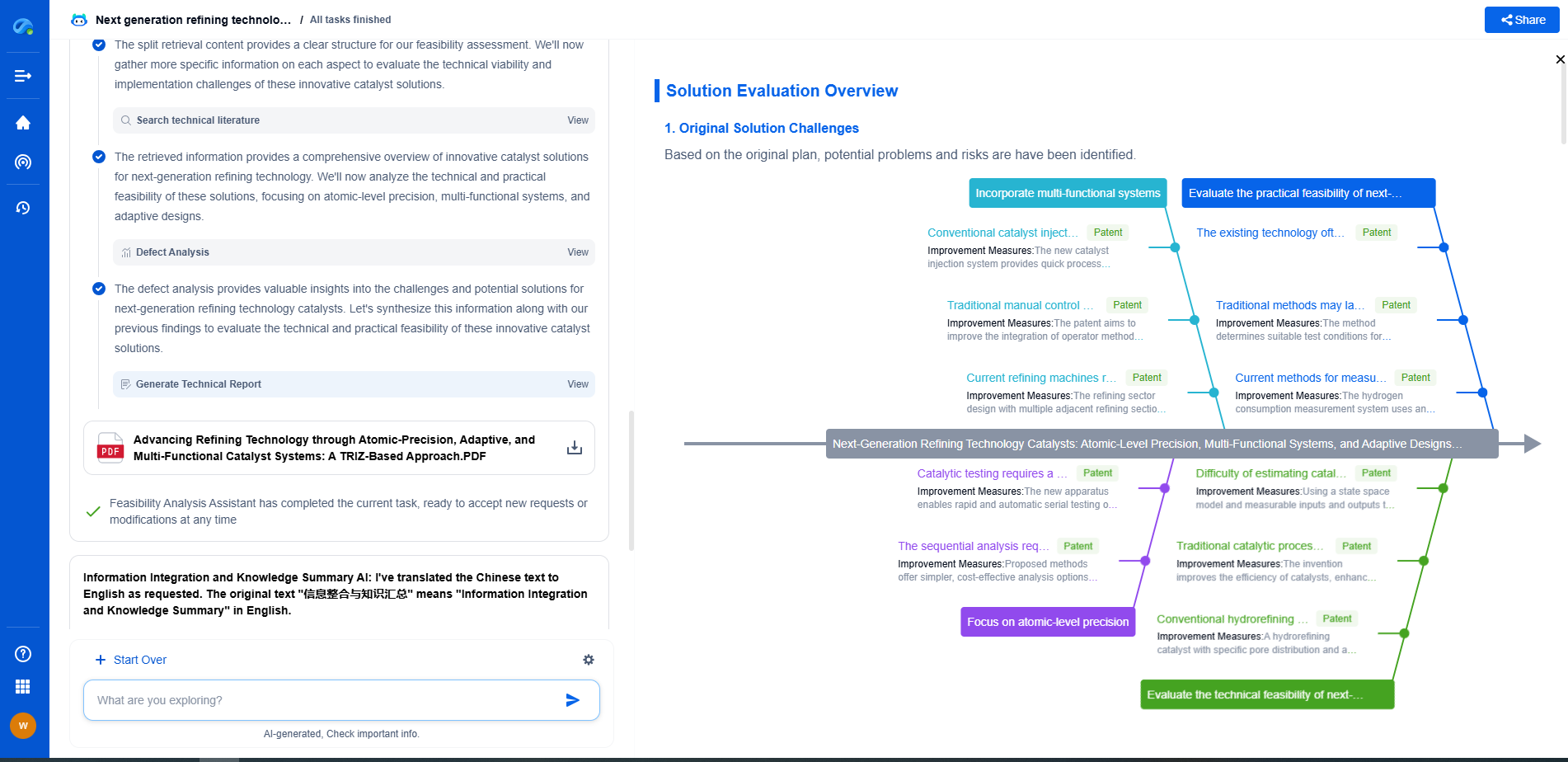

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Whether you're optimizing lithography depth of focus or exploring new materials for sub-3nm nodes, Patsnap Eureka empowers you to make smarter decisions, faster—combining AI efficiency with domain-specific insight.

💡 Start your free trial today and see how Eureka transforms how you discover, evaluate, and act on innovation in photolithography—from idea to impact.

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com