FPGA Implementation of LTE Physical Layer: Challenges and Solutions

JUL 14, 2025 |

Understanding LTE Physical Layer Requirements

The LTE physical layer is responsible for the transmission and reception of data over the radio interface, making it a cornerstone of LTE technology. It involves complex signal processing tasks such as modulation, demodulation, channel coding, and decoding. These processes demand high computational power and real-time processing capabilities, which FPGAs are well-suited to provide due to their parallel processing capabilities and flexibility in hardware configuration.

Challenges in FPGA Implementation

1. Computational Complexity

The LTE physical layer involves highly complex algorithms that require extensive computational resources. Implementing these algorithms on an FPGA can be challenging due to the need to balance between resource utilization and processing speed. The parallel nature of FPGA architectures offers an advantage, but designing efficient architectures that can process large amounts of data in real-time remains a significant challenge.

2. Resource Utilization

FPGAs have a finite amount of resources such as logic blocks, memory, and I/O pins. Implementing the entire LTE physical layer can consume a significant portion of these resources, which might limit the scalability and flexibility of the design. Resource allocation and optimization are crucial to ensure that the FPGA can handle the demands of the LTE physical layer without exhausting its capabilities.

3. Timing Constraints

Meeting timing constraints is another major challenge in FPGA implementation. The LTE physical layer requires precise timing to ensure accurate data transmission and reception. Delays in processing or data transfer can lead to errors and degraded performance. Achieving the necessary timing performance involves careful design and optimization of the FPGA architecture and timing paths.

Solutions to Overcome Implementation Challenges

1. Parallel Processing and Pipelining

One effective solution to address computational complexity is to utilize parallel processing and pipelining techniques. By distributing tasks across multiple processing units and executing them concurrently, FPGAs can significantly enhance processing speed. Pipelining, on the other hand, allows different stages of a process to be executed in parallel, reducing latency and improving throughput.

2. Resource Optimization Techniques

Resource optimization is critical for efficient FPGA implementation. Techniques such as resource sharing, where multiple functions use the same hardware resources, and folding, which reuses resources in different timeslots, can help minimize the overall resource usage. Additionally, using high-level synthesis tools can automate resource optimization, leading to more efficient designs.

3. Timing Optimization Strategies

To meet stringent timing constraints, designers can employ various timing optimization strategies. These include optimizing the placement of logic and routing paths to minimize delays, using clock domain crossing techniques to manage the transfer of data between different clock domains, and employing advanced timing analysis tools to identify and resolve bottlenecks in the design.

Conclusion

The implementation of the LTE physical layer on FPGAs presents a host of challenges, primarily due to the complexity and stringent performance requirements of the system. However, by leveraging FPGA's inherent strengths in parallel processing and adopting innovative design and optimization techniques, these challenges can be effectively addressed. As mobile communication technologies continue to advance, the role of FPGAs in supporting these developments will remain crucial, driving the need for continuous improvement in design methodologies and implementation strategies. Through collaboration, research, and innovation, the challenges of FPGA implementation can be transformed into opportunities for technological advancement in the realm of mobile communications.

From 5G NR to SDN and quantum-safe encryption, the digital communication landscape is evolving faster than ever. For R&D teams and IP professionals, tracking protocol shifts, understanding standards like 3GPP and IEEE 802, and monitoring the global patent race are now mission-critical.

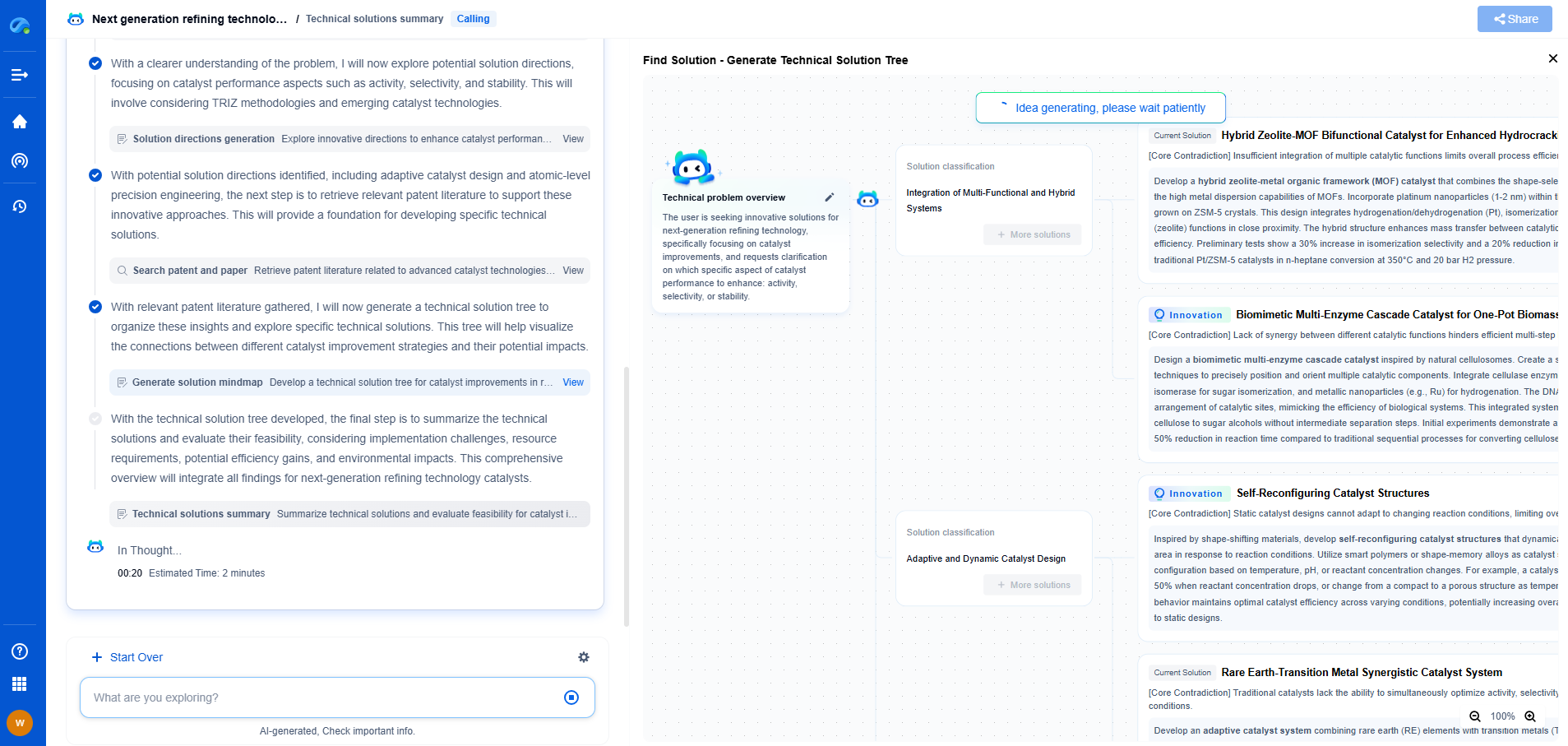

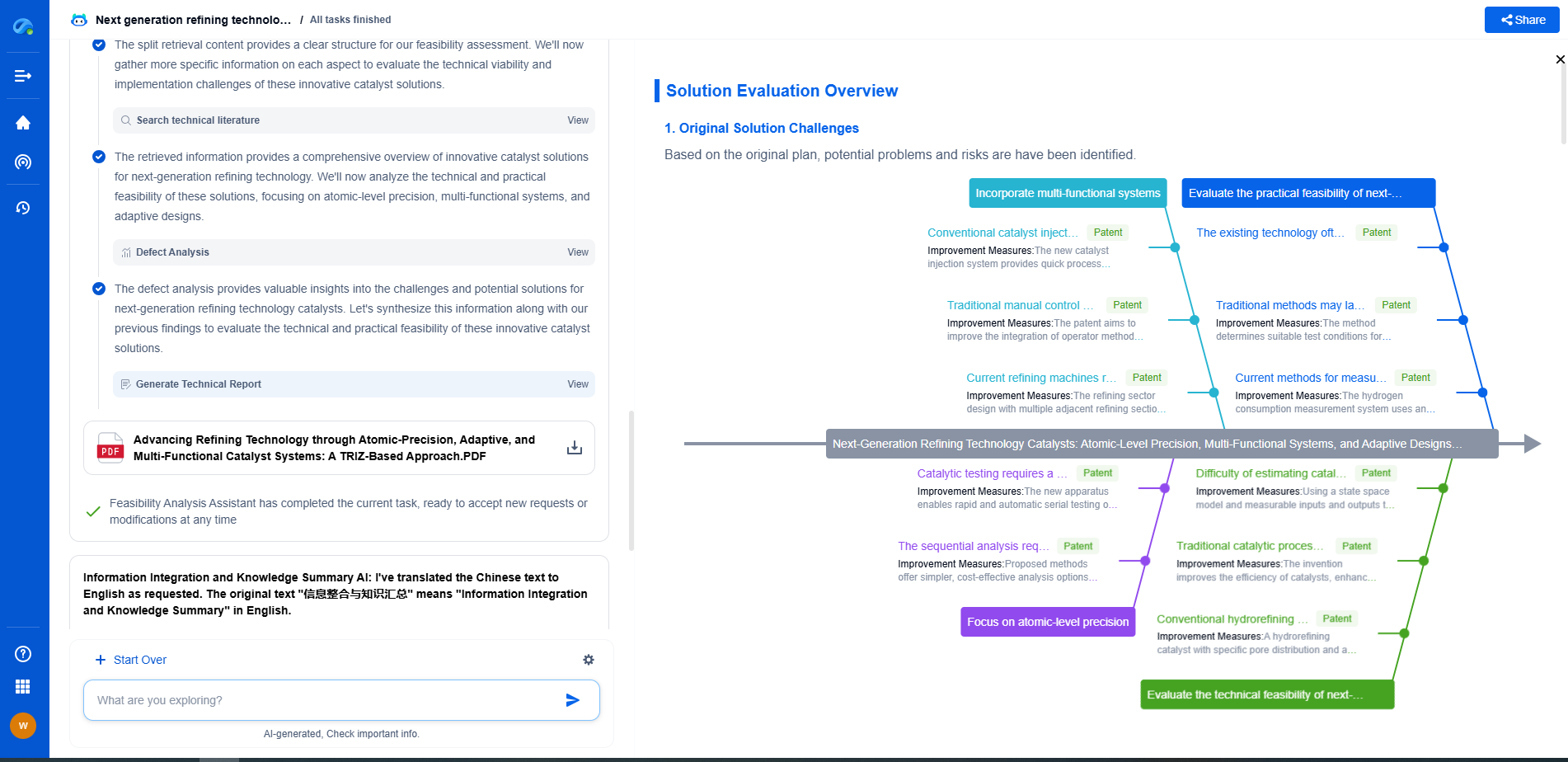

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

📡 Experience Patsnap Eureka today and unlock next-gen insights into digital communication infrastructure, before your competitors do.

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com