FPGA Timing Closure Challenges in High-Speed SerDes Designs

JUL 14, 2025 |

The design landscape of high-speed Serializers/Deserializers (SerDes) in Field-Programmable Gate Arrays (FPGAs) is characterized by increasing complexity and performance demands. As data rates soar and bandwidth requirements skyrocket, achieving timing closure becomes a paramount challenge for engineers. Timing closure is crucial to ensure that all signals in a design meet their required performance criteria, particularly in the high-speed domain where minute discrepancies can lead to significant operational issues. This blog explores key timing closure challenges encountered in high-speed SerDes designs using FPGAs and strategies to address these challenges.

Understanding Timing Closure in FPGAs

At its core, timing closure involves aligning the actual signal timing with the intended design specifications. In FPGA designs, this includes managing setup and hold times, clock skews, and propagation delays. High-speed SerDes further complicates this with their stringent timing requirements. Accurate timing closure in SerDes FPGA designs ensures reliable data transmission and reception, crucial for applications like telecommunications, data centers, and high-performance computing.

Challenges in High-Speed SerDes Timing Closure

1. Clock Domain Crossing

One of the foremost challenges in high-speed SerDes designs is managing clock domain crossings. FPGAs often need to handle multiple clock domains, especially when interfacing with external high-speed components. The risk of data corruption at these crossings mandates meticulous attention to timing constraints. Techniques such as using asynchronous FIFOs and implementing appropriate handshake mechanisms are often employed to safely manage clock domain crossings.

2. Signal Integrity and Jitter

Signal integrity is a significant hurdle in achieving timing closure for high-speed designs. As frequencies increase, the effects of parasitic inductance and capacitance become more pronounced, leading to reflections, crosstalk, and increased jitter. Jitter, the deviation from the ideal timing of a signal, can severely impact the performance of SerDes links. Design practices such as impedance matching, careful layout planning, and the use of low-jitter clock sources are essential to mitigate signal integrity issues.

3. Floorplanning and Placement

Effective floorplanning and placement are crucial in high-speed SerDes designs to minimize delays and skew. Poorly planned layouts can result in longer interconnect paths, leading to increased propagation delays and timing violations. Utilizing features like FPGA-specific placement tools and adhering to best practices for design partitioning can help optimize layout and enhance timing performance.

4. Power Supply Noise

Power supply noise, including voltage droop and ground bounce, can introduce timing uncertainties. High-speed operations often lead to significant transient currents, affecting the power distribution network within the FPGA. Implementing robust decoupling strategies and designing an efficient power delivery network are critical to minimize the effects of power supply noise on timing closure.

5. PVT Variations

Process, Voltage, and Temperature (PVT) variations pose inherent challenges in FPGA designs. These variations can lead to unpredictable changes in delay and timing, necessitating designs that are resilient to such variations. Employing on-chip monitoring systems and adaptive calibration techniques can help mitigate the impacts of PVT variations on timing closure.

Strategies for Achieving Timing Closure

1. Constraint Management

Effectively managing and applying timing constraints is fundamental to achieving timing closure. This includes defining appropriate setup and hold times, specifying multicycle paths, and managing false paths. Utilizing advanced constraint management tools provided by FPGA vendors can streamline this process and enhance the accuracy of timing analysis.

2. Incremental Compilation

Incremental compilation allows designers to make changes to specific parts of a design without recompiling the entire project, saving time and preserving timing closure in unaffected areas. This approach can be particularly beneficial in large, complex designs where maintaining timing closure across the board is challenging.

3. Advanced Simulation and Verification

Thorough simulation and verification are indispensable for identifying and addressing timing issues early in the design process. Utilizing high-fidelity models and comprehensive testbenches can help designers uncover potential timing bottlenecks and refine their designs accordingly.

Conclusion

Achieving timing closure in high-speed SerDes FPGA designs is a multifaceted challenge that demands careful consideration of various factors, from signal integrity to power supply noise and PVT variations. By employing strategic design practices, leveraging advanced tools, and maintaining a proactive approach to timing analysis, engineers can navigate these challenges and achieve reliable, high-performance SerDes implementations. As technology continues to advance, staying abreast of emerging techniques and tools will be crucial for maintaining success in this dynamic field.

From 5G NR to SDN and quantum-safe encryption, the digital communication landscape is evolving faster than ever. For R&D teams and IP professionals, tracking protocol shifts, understanding standards like 3GPP and IEEE 802, and monitoring the global patent race are now mission-critical.

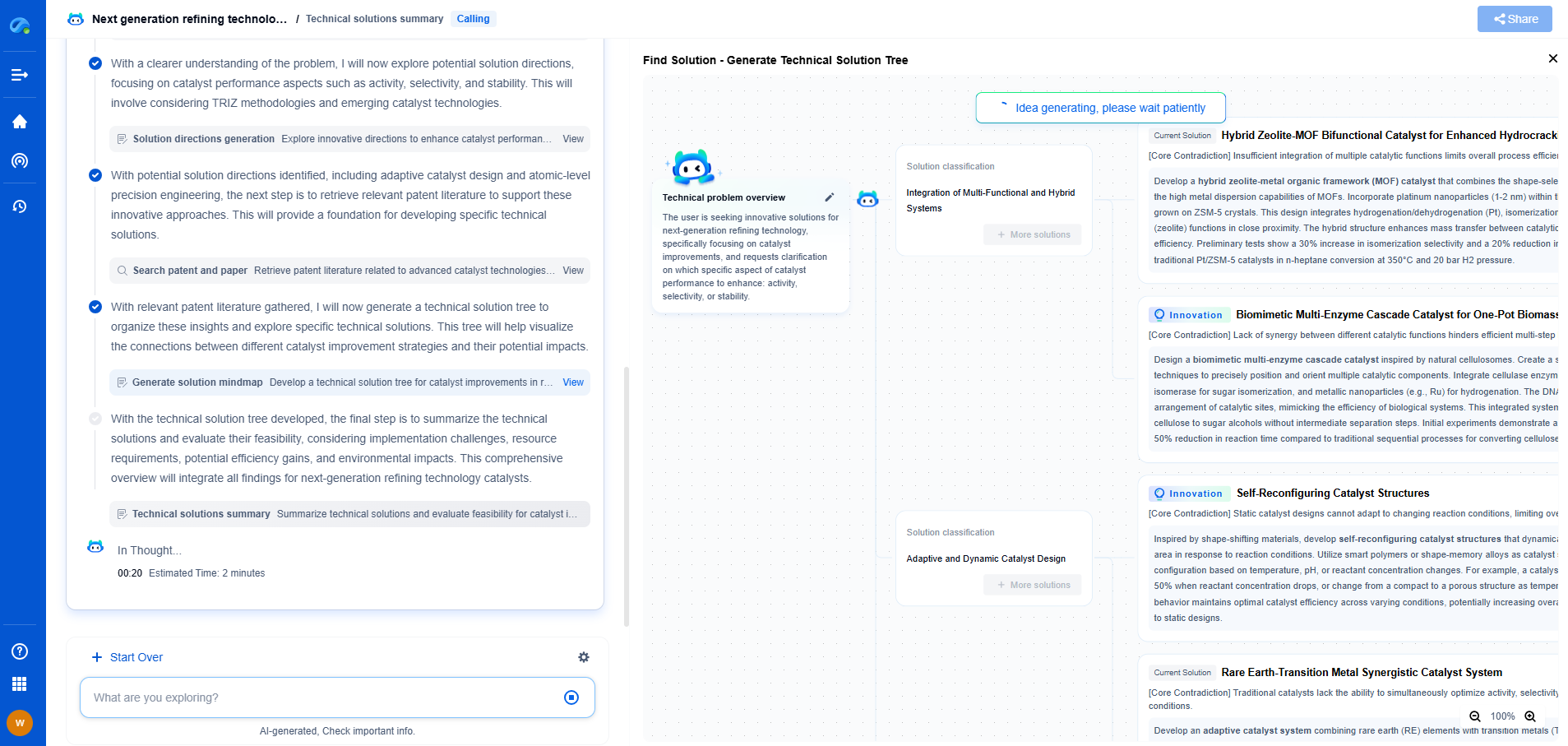

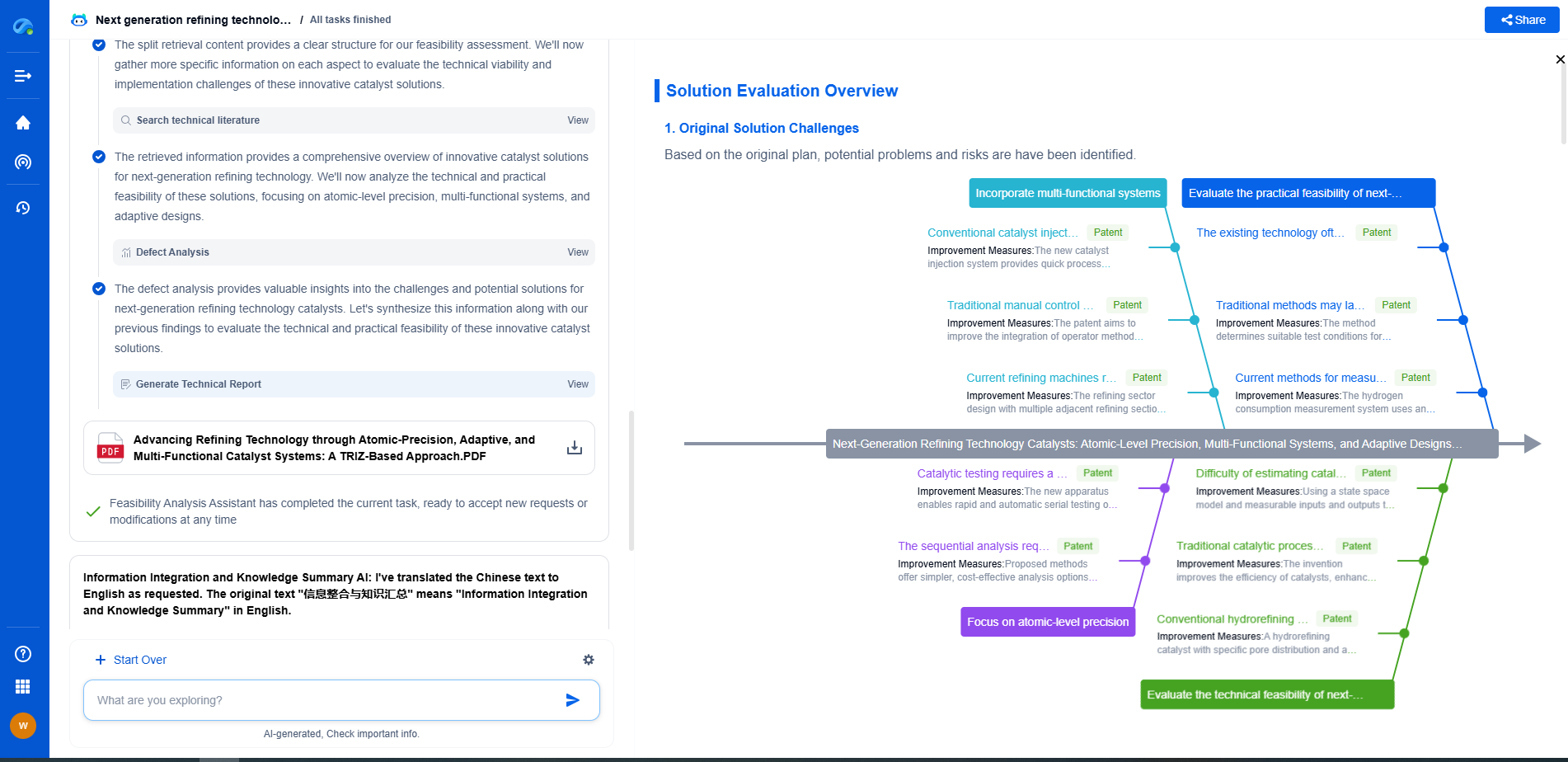

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

📡 Experience Patsnap Eureka today and unlock next-gen insights into digital communication infrastructure, before your competitors do.

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com