FPGA Timing Violations: How to Fix Metastability Issues

JUL 2, 2025 |

Field Programmable Gate Arrays (FPGAs) are popular for their versatility and reconfigurable nature, making them an excellent choice for a wide range of applications. However, one challenge that often arises when working with FPGAs is timing violations, particularly metastability issues. Metastability occurs when a flip-flop or latch experiences an undefined state, typically due to a violation of setup or hold time requirements. This can lead to unreliable system behavior and is a critical issue to address in FPGA design.

Understanding Metastability

Metastability is a phenomenon where a digital circuit fails to settle into a stable '0' or '1' state within a specified time frame. It occurs when an input signal changes too close to the clock edge, violating the setup or hold time constraints of a flip-flop. As a result, the flip-flop enters a transient state, which can propagate through the system and cause unpredictable behavior. Understanding how metastability arises and manifests is crucial in developing effective strategies to mitigate its impact.

Identifying Timing Violations

The first step in addressing metastability is identifying timing violations in your FPGA design. Timing analysis tools, such as those provided by FPGA vendors, can help detect paths that might be prone to timing issues. Pay special attention to paths with tight setup and hold margins and those that cross clock domains, as these are common sources of metastability. By thoroughly analyzing your design, you can pinpoint the critical areas that need attention.

Strategies to Mitigate Metastability

1. **Clock Domain Crossing (CDC) Techniques**: Metastability often occurs at clock domain boundaries. Implementing CDC techniques like double-flop synchronization can significantly reduce the risk. This involves using two or more flip-flops in series to resynchronize the signal into the new clock domain, allowing time for any metastable states to resolve before the signal is used.

2. **Adjusting Timing Constraints**: Tightening the timing constraints during synthesis and implementation can help ensure that your design meets the necessary setup and hold times. This might involve adjusting the clock frequency or changing the placement of critical paths to reduce delay.

3. **Pipeline Registers**: Adding pipeline registers to your data paths can help absorb unexpected delays, giving signals more time to stabilize before they are used. This is particularly useful in designs with long combinational paths where timing slack is limited.

4. **Using Robust Design Practices**: Employing robust design practices, such as avoiding asynchronous resets and using synchronous design techniques, can help prevent metastability. Ensuring that all inputs to flip-flops are synchronized with the clock can minimize the risk of timing violations.

5. **Simulating and Testing**: Simulating your design under different conditions can help identify potential timing issues before deployment. Use tools to inject random delays and simulate worst-case scenarios to ensure your design is resilient to metastability.

Real-world Examples and Case Studies

Illustrating the impact of metastability through real-world examples can be enlightening. Consider discussing case studies where metastability was successfully mitigated, highlighting the strategies used and their effectiveness. This can provide valuable insights and practical guidance for engineers facing similar challenges.

Conclusion

Metastability in FPGAs is a critical issue that can compromise the reliability of digital systems. By understanding the nature of metastability and employing effective mitigation strategies, designers can significantly reduce the risk of timing violations. Through careful analysis, robust design practices, and thorough testing, it is possible to create stable and reliable FPGA designs that perform as intended. Addressing metastability not only enhances the performance of your design but also ensures its long-term reliability in real-world applications.

Ready to Reinvent How You Work on Control Systems?

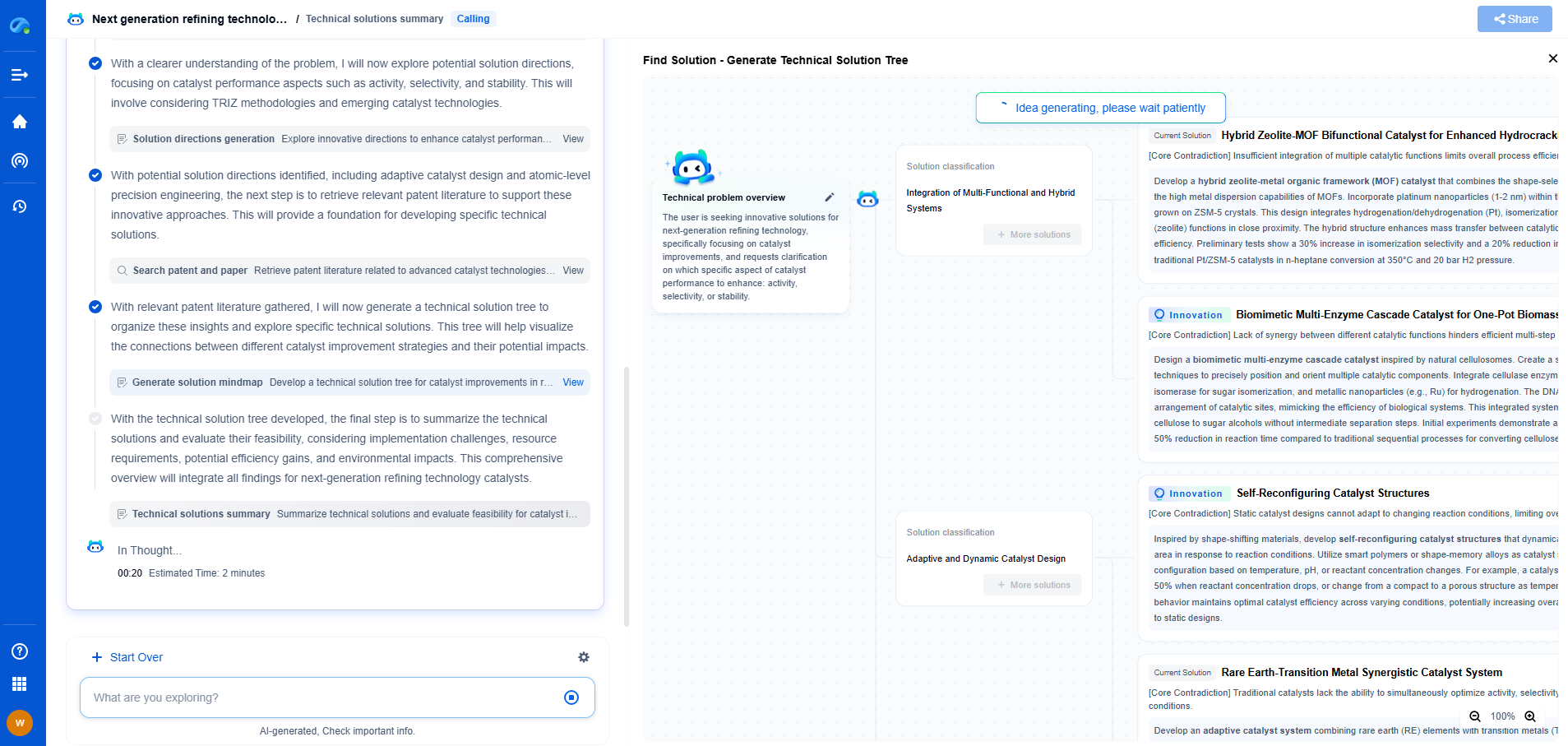

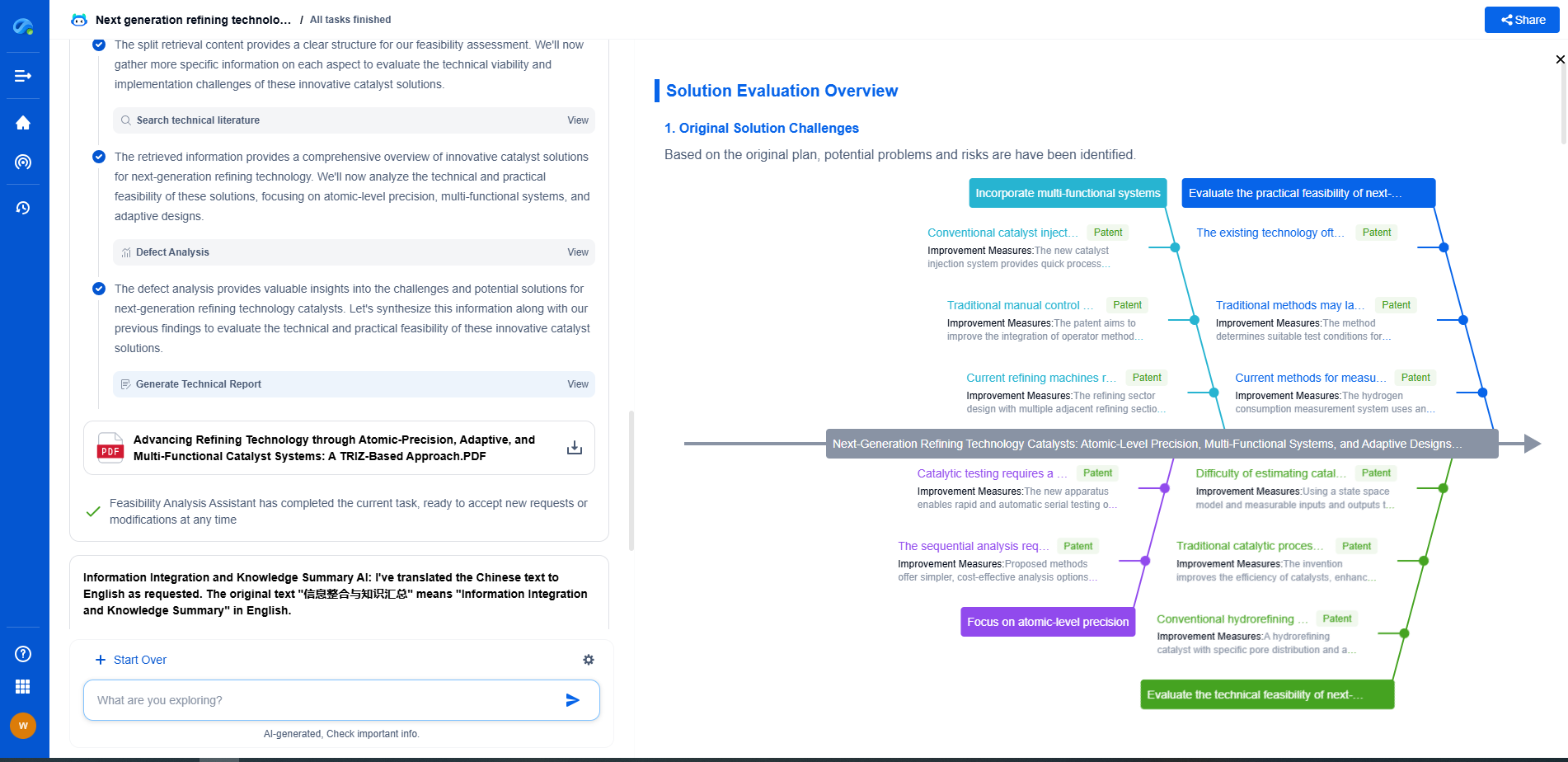

Designing, analyzing, and optimizing control systems involves complex decision-making, from selecting the right sensor configurations to ensuring robust fault tolerance and interoperability. If you’re spending countless hours digging through documentation, standards, patents, or simulation results — it's time for a smarter way to work.

Patsnap Eureka is your intelligent AI Agent, purpose-built for R&D and IP professionals in high-tech industries. Whether you're developing next-gen motion controllers, debugging signal integrity issues, or navigating complex regulatory and patent landscapes in industrial automation, Eureka helps you cut through technical noise and surface the insights that matter—faster.

👉 Experience Patsnap Eureka today — Power up your Control Systems innovation with AI intelligence built for engineers and IP minds.