How cyclic redundancy check (CRC-32 vs CRC-16) is implemented in hardware

JUL 14, 2025 |

Understanding CRC Basics

Before delving into the specifics of CRC-32 and CRC-16, it’s essential to understand how CRC functions fundamentally. CRC is based on polynomial division, where the data is treated as a polynomial and divided by a generator polynomial. The remainder of this division is the CRC code, which is appended to the data. On receiving the data, the same division process is conducted, and if the remainder is zero, the data is considered intact.

Hardware Implementation of CRC

The hardware implementation of CRC is preferred in scenarios requiring high-speed data processing. This implementation leverages shift registers and exclusive OR (XOR) gates to perform polynomial division efficiently.

1. Shift Registers and XOR Gates

The core of CRC hardware involves shift registers that handle the bit-by-bit operations on data. When data is fed into the CRC hardware, each bit is shifted into the register. XOR gates are placed in such a manner that they implement the feedback logic corresponding to the generator polynomial. As each bit enters, the shift register shifts the existing bits and performs XOR operations with the new bit according to the polynomial, computing the CRC remainder in real time.

CRC-16 vs. CRC-32

While the basic operation of CRC is consistent across different variants, the size of the CRC (16-bits for CRC-16 and 32-bits for CRC-32) and their generator polynomials are notably different, which impacts their hardware implementations.

1. CRC-16

CRC-16 is commonly used in smaller data sets, where quick error-checking suffices, and resources are limited. The CRC-16 generator polynomial is typically 0x8005 or 0x1021. In hardware, CRC-16 requires a 16-bit shift register. The XOR gates are connected according to the chosen polynomial. This smaller configuration allows for a compact implementation, making it suitable for embedded systems.

2. CRC-32

CRC-32 is widely used in larger applications like Ethernet and ZIP file compression, where more robust error-checking is necessary. It utilizes a 32-bit shift register, and the common generator polynomial is 0x04C11DB7. The increased number of bits and a more complex polynomial mean that more XOR gates are involved in the feedback configuration. Despite being larger, CRC-32 hardware is optimized for rapid processing in environments where data integrity is paramount.

Advantages and Considerations

One key advantage of hardware CRC is its speed. Since the operations are conducted in parallel and directly on the data stream, it significantly outperforms software implementations, particularly for large volumes of data. This speed is crucial in applications where real-time data processing is needed.

However, designing CRC hardware requires careful consideration of factors like power consumption, especially in mobile or embedded applications. Balancing the speed of CRC hardware with the space and power constraints is a critical aspect of the implementation.

Applications and Use Cases

CRC-16 and CRC-32 find their uses in various fields. CRC-16 is prevalent in smaller-sized communication protocols like Bluetooth, where quick error detection is necessary. On the other hand, CRC-32 serves in systems demanding higher reliability, such as file storage formats and networking protocols.

Conclusion

Implementing CRC-16 and CRC-32 in hardware is a sophisticated process that offers fast and efficient error detection essential for maintaining data integrity. Through the use of shift registers and XOR gates, these CRCs perform polynomial division directly on incoming data streams, ensuring robustness in various applications. By understanding the nuances of their implementation, developers can make informed decisions about which CRC variant best suits their needs.

From 5G NR to SDN and quantum-safe encryption, the digital communication landscape is evolving faster than ever. For R&D teams and IP professionals, tracking protocol shifts, understanding standards like 3GPP and IEEE 802, and monitoring the global patent race are now mission-critical.

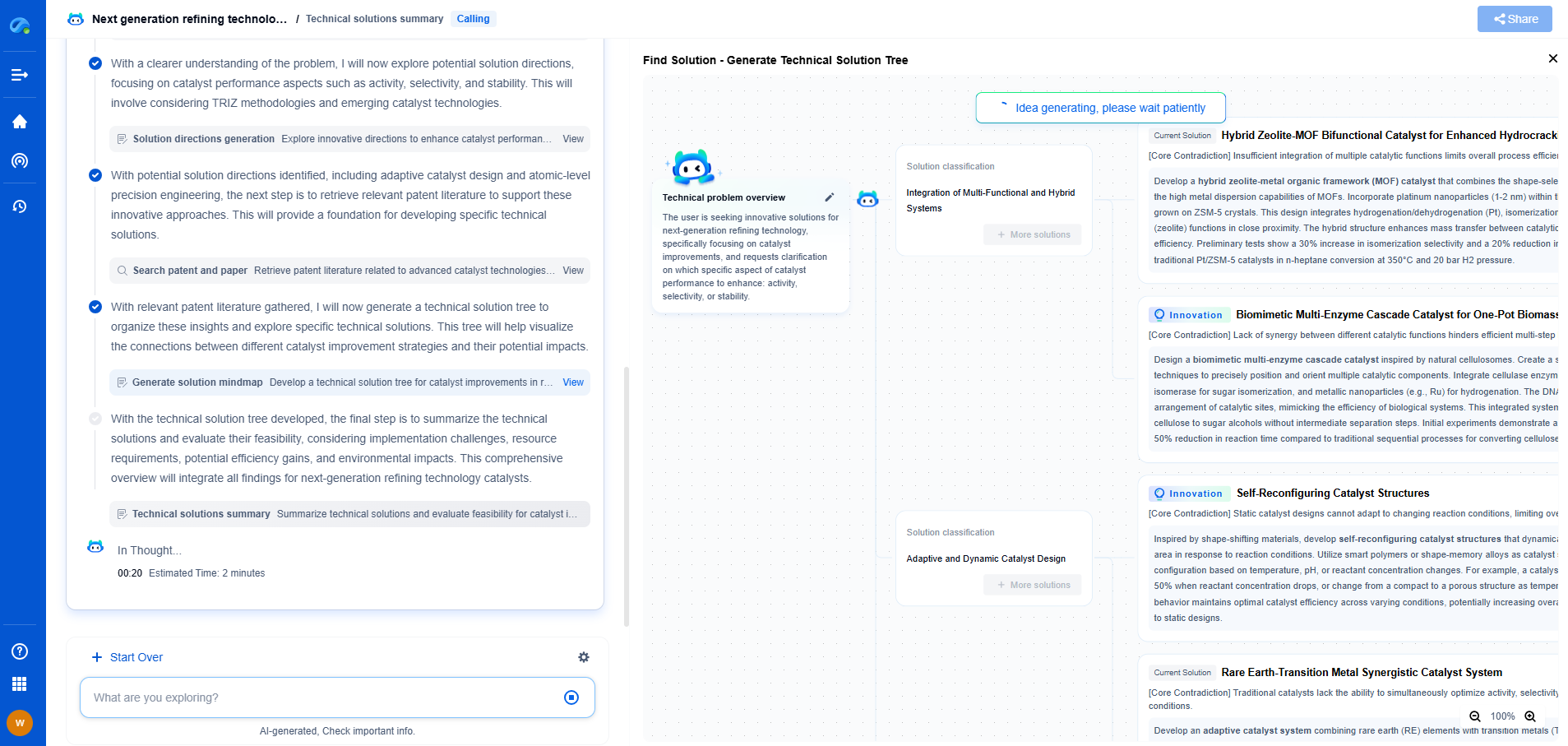

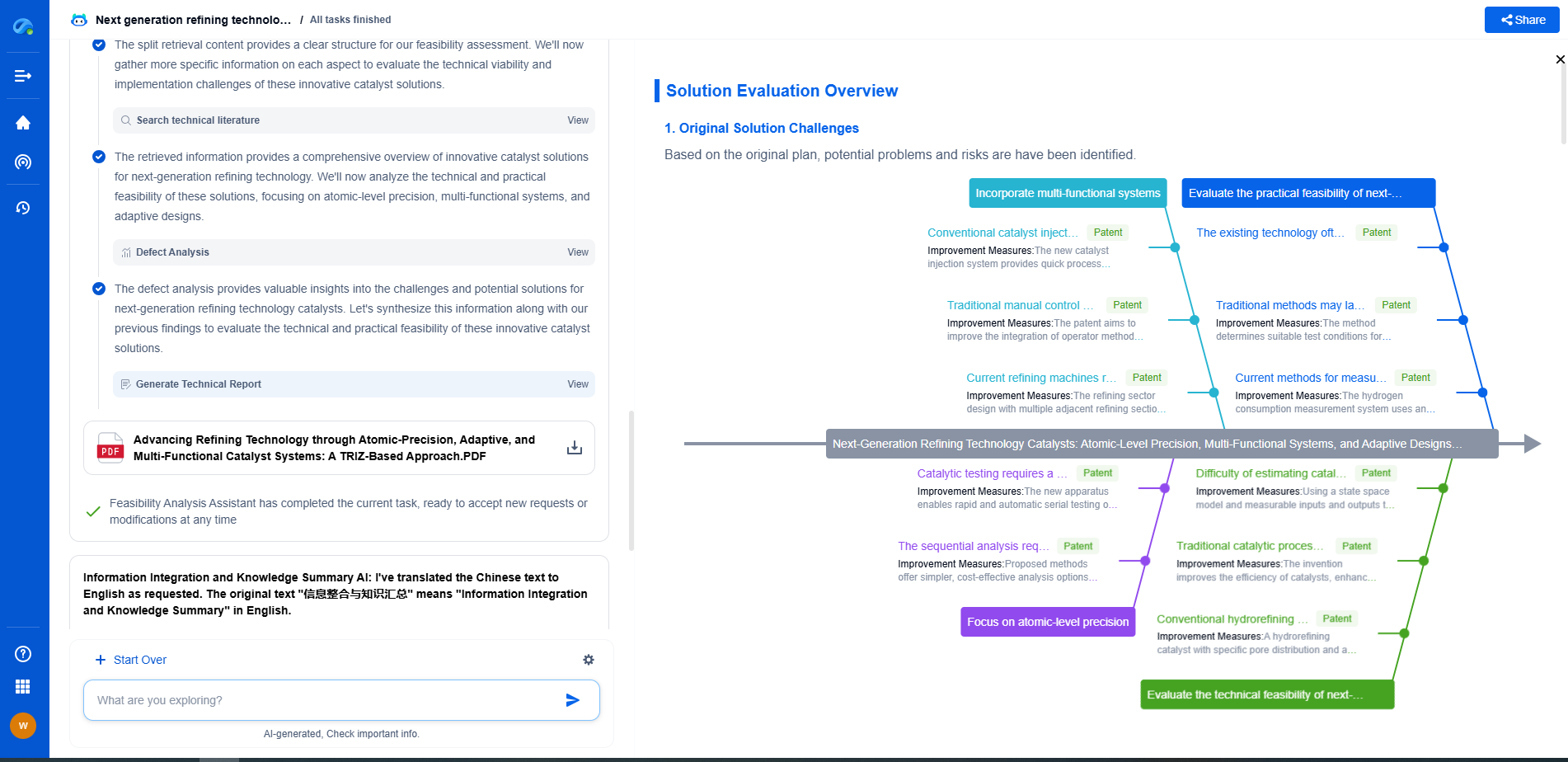

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

📡 Experience Patsnap Eureka today and unlock next-gen insights into digital communication infrastructure, before your competitors do.

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com