How Does 3D Packaging Improve Semiconductor Performance and Efficiency?

JUN 27, 2025 |

As the demand for smaller, faster, and more efficient electronic devices continues to grow, the semiconductor industry is constantly seeking innovative solutions to enhance performance and efficiency. One such breakthrough is 3D packaging, a technology that has revolutionized the way semiconductor devices are designed and manufactured. By stacking multiple layers of integrated circuits (ICs) vertically, 3D packaging provides a new dimension to chip design, promising significant improvements in performance and energy efficiency.

Understanding 3D Packaging

3D packaging refers to the integration of multiple semiconductor dies in a single package. Unlike traditional 2D packaging, where chips are placed side by side on a substrate, 3D packaging allows for vertical stacking, connecting chips through vertical interconnects known as through-silicon vias (TSVs). This vertical integration not only reduces the footprint of the device but also shortens the interconnect length between chips, resulting in lower power consumption and faster data transfer.

Enhancing Performance Through 3D Packaging

The performance gains achieved through 3D packaging are primarily due to reduced signal delay and improved bandwidth. By minimizing the distance that electrical signals must travel between chips, 3D packaging significantly reduces signal latency, thereby increasing the overall speed of the device. Additionally, the increased bandwidth provided by the shorter interconnects allows for higher data throughput, enhancing the performance of applications that require rapid data processing.

Another aspect of performance improvement is the ability to integrate heterogeneous chips within a single package. This means that different types of ICs, such as processors, memory, and sensors, can be combined in a 3D stack. Heterogeneous integration enables optimized communication between different components, further boosting performance. For example, placing memory closer to the processor reduces access time, which is critical for applications such as artificial intelligence and high-performance computing.

Improving Energy Efficiency

Energy efficiency is another key advantage of 3D packaging. By reducing the length of interconnects and minimizing signal delay, 3D packaging decreases power consumption. The shorter interconnects require less energy to transmit signals, leading to a reduction in overall power usage. This is particularly beneficial for mobile and wearable devices, where battery life is a critical factor.

Moreover, 3D packaging facilitates better thermal management. In traditional 2D configurations, heat dissipation can be a challenge due to the limited surface area available for cooling. 3D packaging allows for more effective heat dissipation through the use of thermal vias and advanced cooling techniques, preventing overheating and enhancing device longevity. Efficient thermal management not only contributes to energy savings but also ensures reliable performance under demanding conditions.

Challenges and Future Prospects

While 3D packaging offers numerous advantages, it is not without its challenges. The complexity of manufacturing and the need for precise alignment and bonding of stacked dies pose significant technical hurdles. Additionally, the cost of implementing 3D packaging can be higher compared to traditional methods, which may limit its adoption in cost-sensitive markets.

However, ongoing research and development efforts are focused on addressing these challenges. Advances in materials, processes, and design tools are paving the way for more efficient and cost-effective 3D packaging solutions. As these technologies mature, it is expected that 3D packaging will become more widespread, driving the next wave of innovation in the semiconductor industry.

Conclusion

3D packaging represents a transformative approach to semiconductor design, offering substantial improvements in performance and energy efficiency. By enabling vertical integration and reducing interconnect lengths, this technology addresses the limitations of traditional 2D packaging, paving the way for more powerful and efficient electronic devices. As the semiconductor industry continues to evolve, 3D packaging is poised to play a crucial role in meeting the demands of future applications, from mobile devices to data centers and beyond.

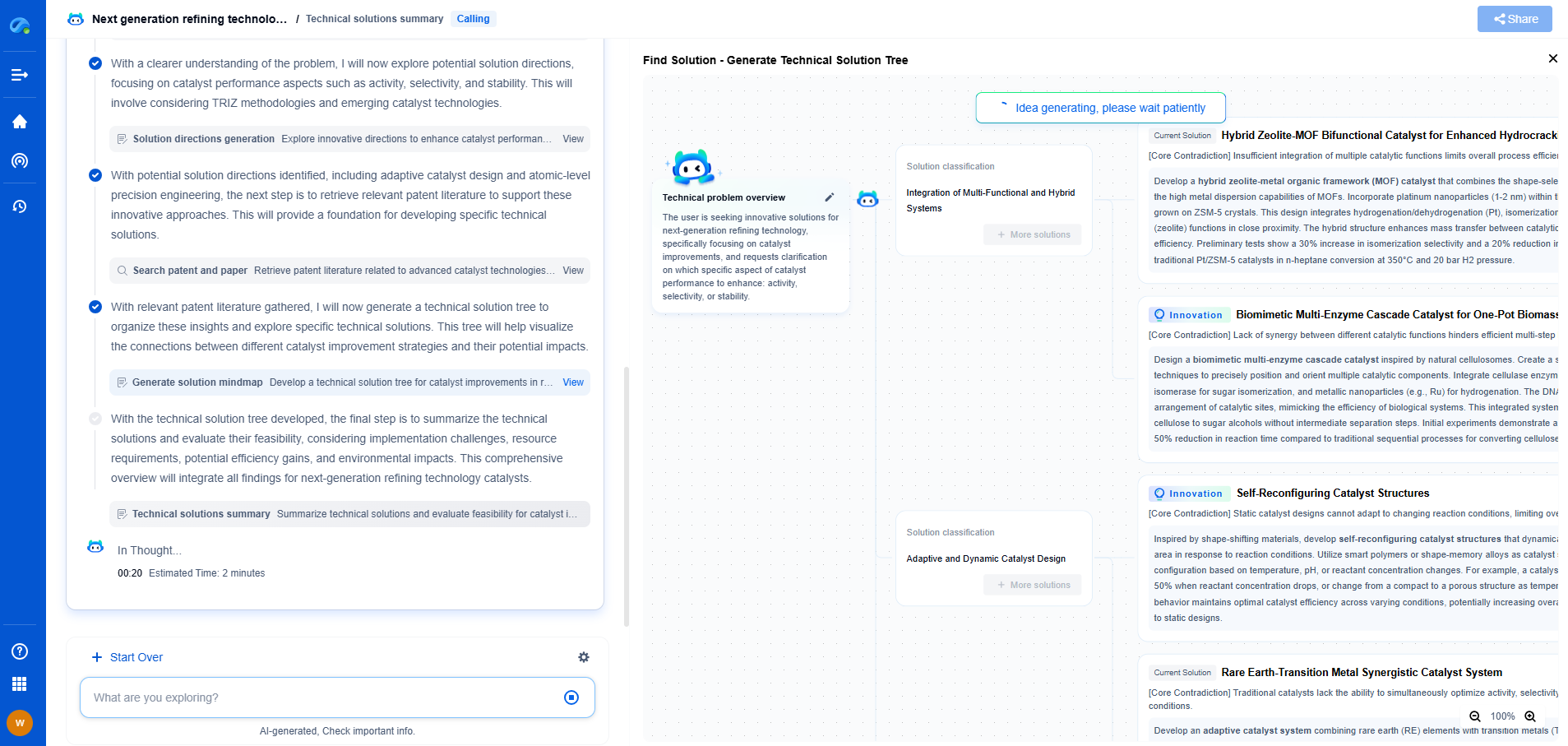

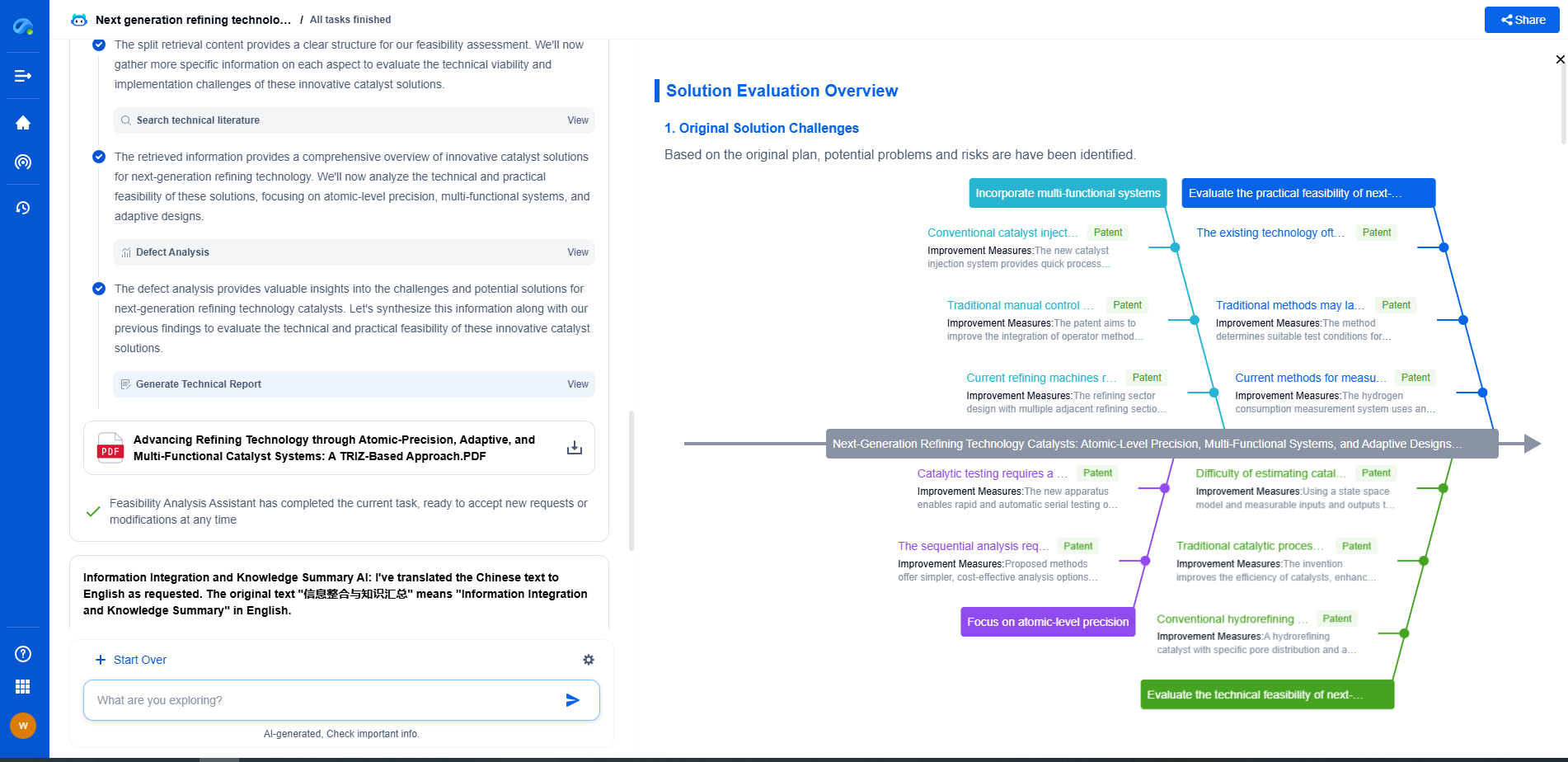

Empower Your Breakthroughs in Basic Electric Components with Patsnap Eureka

From resistors, capacitors, and inductors to fuses, connectors, superconductors, and nano-scale materials—basic electric elements may be the building blocks of modern electronics, but the innovation behind them is anything but simple. As device miniaturization accelerates and materials science pushes new frontiers, R&D and IP teams face increasing complexity in staying on top of technical advancements, patent activity, and competitive landscapes.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

🔧 Whether you’re optimizing energy storage, improving thermal resistance, or creating the next leap in circuit efficiency, Patsnap Eureka is your AI copilot for high-efficiency, high-precision R&D and IP strategy.

👉 Experience how Patsnap Eureka can revolutionize your R&D and IP strategy. Request a demo today and power up your next breakthrough.