Line Edge Roughness (LER): Measurement Techniques and Impact on Yield

JUL 28, 2025 |

Line Edge Roughness (LER) is a critical parameter in the semiconductor manufacturing process. As the industry continues to push the limits of miniaturization, the importance of LER in determining the performance and yield of integrated circuits (ICs) cannot be understated. In essence, LER refers to the deviation of the edge of a line from its ideal path, which can lead to variability in the electrical performance of the components.

Measurement Techniques for LER

Accurately measuring LER is essential for controlling and minimizing its impact. Various techniques have been developed and refined over the years to quantify this critical parameter.

Optical Methods

Optical methods are widely used due to their non-destructive nature and ability to provide rapid measurements. Scatterometry, for instance, analyzes the scattered light from a structured surface to determine LER. While optical methods are beneficial for their speed, they may lack the resolution required for advanced nodes.

Electron Beam Lithography

Electron beam lithography offers high-resolution imaging capabilities, making it a valuable tool for LER measurement in nanoscale features. By scanning a focused electron beam across a sample, precise edge contours can be captured. However, this method can be time-consuming and is often best suited for detailed analysis rather than production-line monitoring.

Atomic Force Microscopy

Atomic Force Microscopy (AFM) provides surface topography at the nanoscale, allowing for accurate LER quantification. AFM is particularly useful for research and development settings, where high precision is required. Nonetheless, its slow throughput limits its application in high-volume manufacturing environments.

Impact of LER on Semiconductor Yield

LER can significantly affect the yield of semiconductor devices. As the dimensions of ICs shrink, the relative impact of roughness becomes more pronounced. Here are some key ways in which LER impacts yield:

Device Variability

LER introduces variability in transistor dimensions, which can lead to fluctuations in electrical characteristics such as threshold voltage and drive current. This variability can result in devices that do not meet specification, thereby reducing yield.

Leakage Currents

Increased LER can lead to higher leakage currents due to enhanced electric field effects at the roughened edges. This phenomenon is particularly concerning for power-sensitive applications where leakage can lead to excessive power consumption and reduced reliability.

Short Channel Effects

LER exacerbates short channel effects, particularly in advanced technology nodes. The roughness can cause unintended doping variations, leading to poorer control over the channel and increased susceptibility to short channel effects, ultimately impacting device performance.

Strategies to Minimize LER

Given the significance of LER in semiconductor manufacturing, efforts to minimize its impact are paramount. Some strategies include optimizing the lithography process, employing advanced materials that are less prone to roughness, and refining etch processes to produce smoother line edges.

Conclusion

Line Edge Roughness remains a critical concern in the semiconductor industry, with its impact becoming more pronounced as device dimensions continue to shrink. By understanding and effectively measuring LER, and implementing strategies to minimize its effects, manufacturers can enhance yield and improve the reliability and performance of their semiconductor devices. As technology advances, ongoing research and development will be essential in addressing the challenges posed by LER.

As photolithography continues to push the boundaries of nanoscale patterning, from EUV and DUV advancements to multi-patterning and maskless lithography, innovation cycles are accelerating—and the IP landscape is becoming more complex than ever.

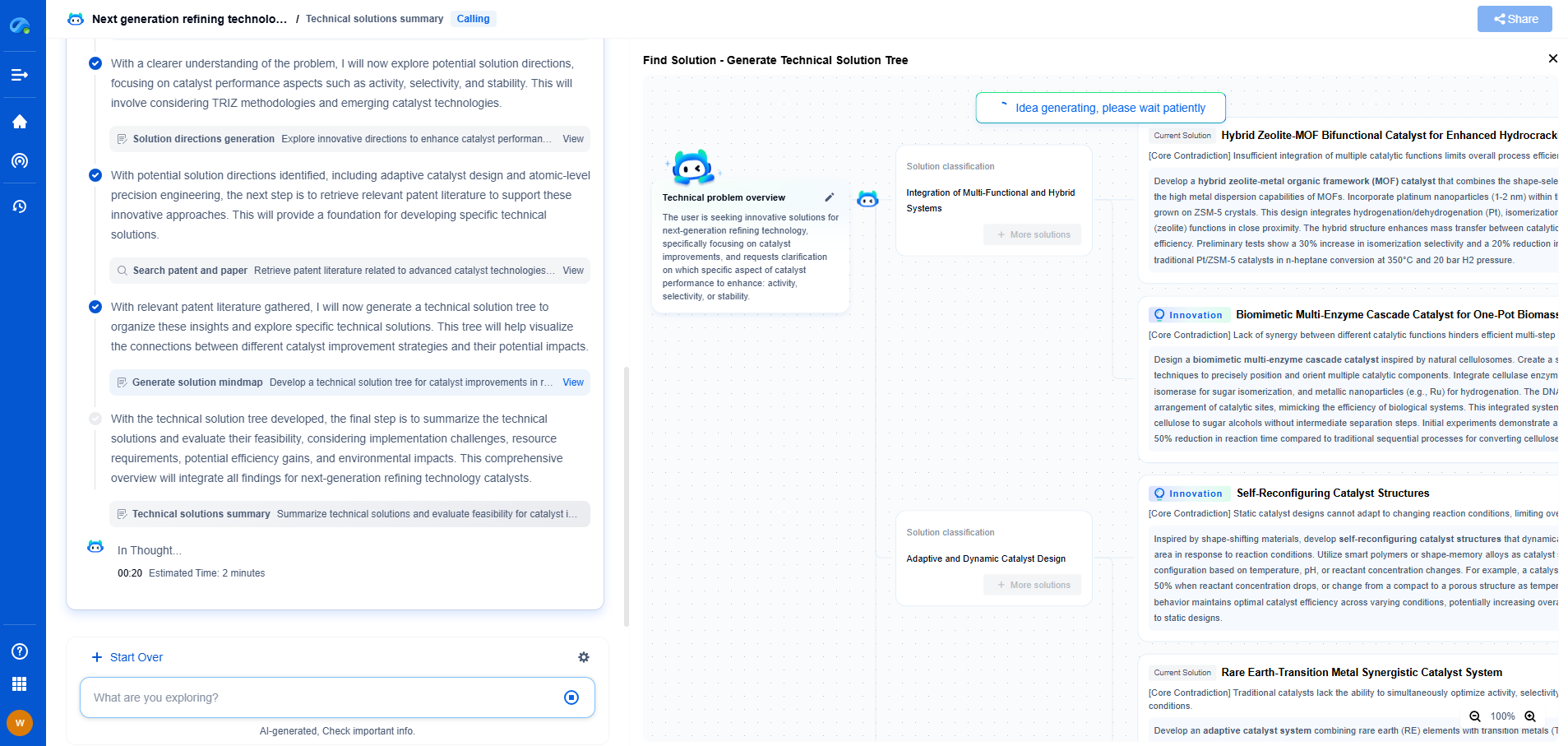

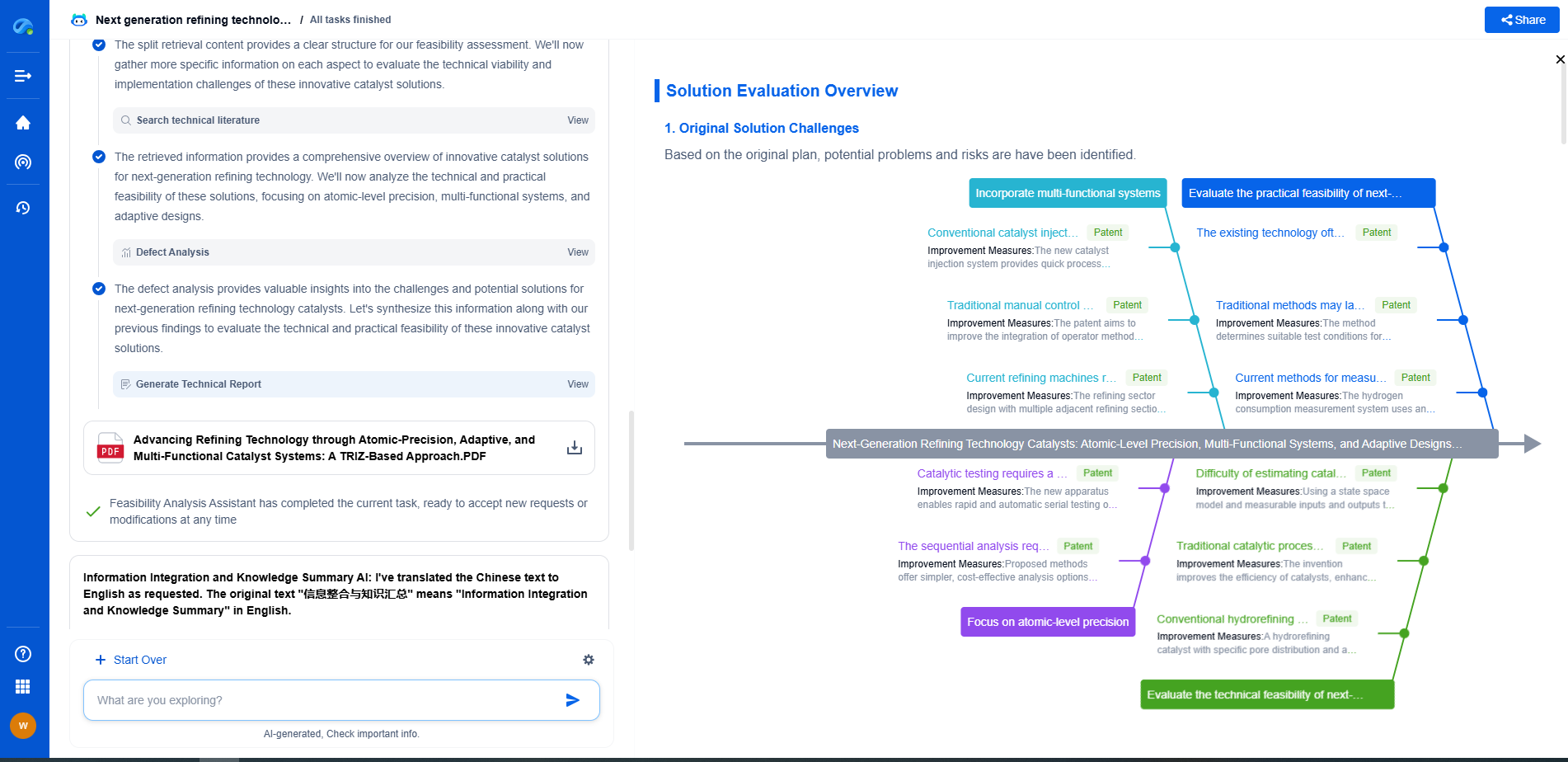

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Whether you're optimizing lithography depth of focus or exploring new materials for sub-3nm nodes, Patsnap Eureka empowers you to make smarter decisions, faster—combining AI efficiency with domain-specific insight.

💡 Start your free trial today and see how Eureka transforms how you discover, evaluate, and act on innovation in photolithography—from idea to impact.

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com