Lithography defect types linked to improper development time

JUL 28, 2025 |

In the world of semiconductor manufacturing, lithography stands as a critical process that dictates the precision and efficacy of chip production. A key aspect of lithography is the development stage, where photoresist material is selectively removed to reveal the underlying substrate. Proper development time is crucial to achieving accurate patterns, and deviations can lead to various defects that compromise the functionality of the final product. This blog delves into the lithography defect types associated with improper development time, highlighting their causes and potential solutions.

Understanding Lithography Development

The development process in lithography involves the use of a chemical developer to dissolve the exposed or unexposed regions of the photoresist, depending on whether a positive or negative resist is used. The development time must be precisely controlled to ensure that the desired pattern is accurately transferred to the substrate. Deviations from the optimal development time can lead to partial or over-development, each introducing specific defects that impact the integrity of the semiconductor device.

Defects Due to Under-Development

1. Incomplete Pattern Transfer

Under-development occurs when the development time is insufficient to fully dissolve the intended regions of the photoresist. This results in incomplete pattern transfer, where some areas of the photoresist remain on the substrate, leading to defective circuits or features. Such defects can cause short-circuits or discontinuities in electrical pathways, severely affecting the performance of the semiconductor device.

2. Residual Photoresist

Residual photoresist left on the substrate due to under-development can create additional layers that were not part of the intended design. These unwanted layers may lead to increased resistance and capacitance within the circuit, degrading the overall performance and reliability of the chip.

Defects Due to Over-Development

1. Pattern Erosion

Over-development, on the other hand, occurs when the development time exceeds the optimum duration, resulting in excessive removal of the photoresist. This can lead to pattern erosion, where the edges of the developed features are eroded, causing a loss of dimensional control. Eroded patterns may lead to increased variability in device performance and reduced yield in the production process.

2. Critical Dimension Variability

The critical dimension (CD) refers to the smallest width of a patterned feature on a chip. Over-development can lead to CD variability, where the actual dimensions of the patterns deviate from the intended design. This variability can significantly impact the electrical properties of the semiconductor device, leading to functional failures and reduced yield.

Strategies for Optimizing Development Time

1. Process Monitoring and Control

To minimize defects associated with improper development time, semiconductor manufacturers employ rigorous process monitoring and control strategies. Real-time monitoring of development processes using advanced metrology tools helps in maintaining optimal development conditions and identifying deviations promptly.

2. Development Time Calibration

Regular calibration of development time is essential to accommodate variations in photoresist formulations, developer concentrations, and environmental conditions. By fine-tuning the development process parameters, manufacturers can achieve consistent and accurate pattern transfer, minimizing defects associated with under or over-development.

Conclusion

The development stage in lithography is a pivotal point in semiconductor manufacturing, where precise control over development time is paramount. Defects arising from improper development time, such as incomplete pattern transfer, residual photoresist, pattern erosion, and critical dimension variability, underscore the importance of stringent process control and optimization. By implementing robust monitoring systems and calibration techniques, manufacturers can mitigate these defects, ensuring the production of high-quality semiconductor devices. Understanding and addressing these defect types is a critical step toward advancing lithography processes and enhancing the performance and reliability of electronic components in an increasingly demanding market.

As photolithography continues to push the boundaries of nanoscale patterning, from EUV and DUV advancements to multi-patterning and maskless lithography, innovation cycles are accelerating—and the IP landscape is becoming more complex than ever.

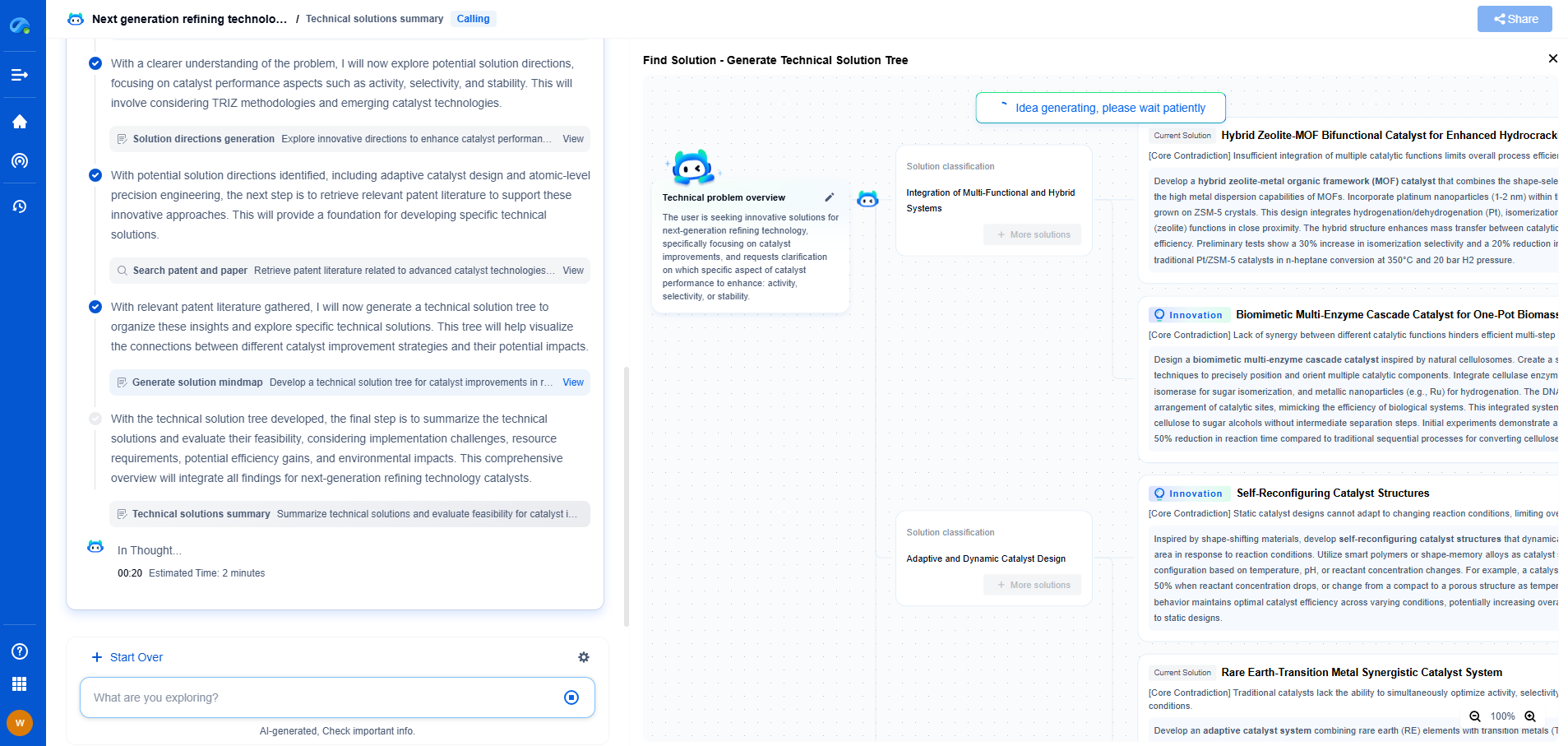

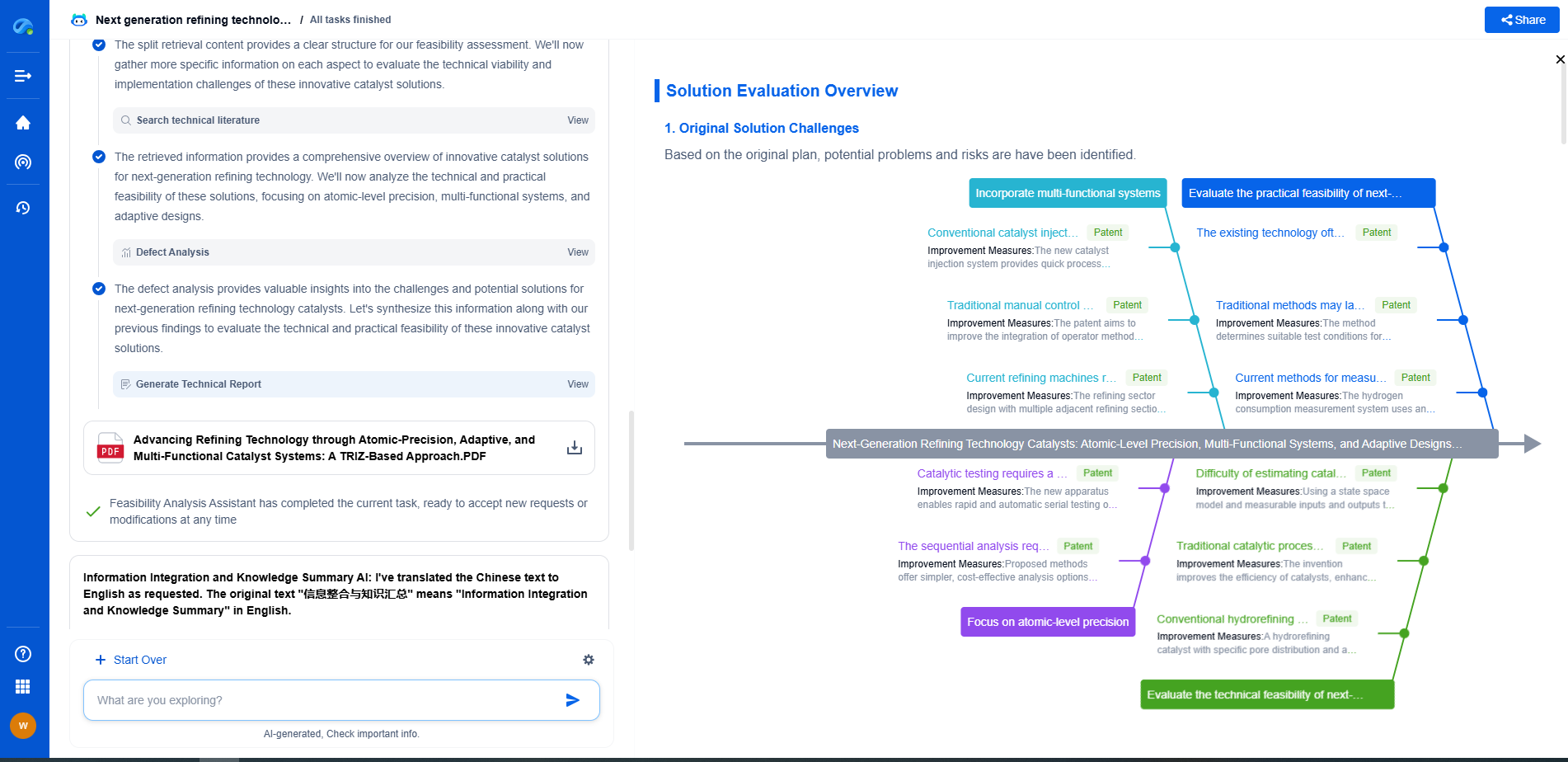

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Whether you're optimizing lithography depth of focus or exploring new materials for sub-3nm nodes, Patsnap Eureka empowers you to make smarter decisions, faster—combining AI efficiency with domain-specific insight.

💡 Start your free trial today and see how Eureka transforms how you discover, evaluate, and act on innovation in photolithography—from idea to impact.