Lithography Process Simulators 101: From Hopkins Equation to Full-Chip Prediction

JUL 28, 2025 |

Lithography process simulation is an essential aspect of modern semiconductor manufacturing, as it plays a critical role in ensuring the accuracy and efficiency of chip production. As semiconductor devices continue to shrink in size, the demand for precise and reliable lithography techniques has never been higher. Process simulators serve as powerful tools that help engineers predict and optimize the intricate details involved in creating integrated circuits.

The Hopkins Equation: Foundation of Optical Lithography

At the heart of lithography process simulation lies the Hopkins equation, a mathematical model that describes the interaction of light with photomasks and photoresists. Named after its developer, Howard Hopkins, this equation provides a comprehensive framework for understanding the diffraction patterns produced when light passes through a mask. The Hopkins equation is particularly important in the context of optical lithography, where the wavelength of the light used is comparable to the size of the features being printed.

The equation helps engineers analyze how different mask patterns affect the distribution of light intensity on the photoresist, which in turn determines the quality and accuracy of the printed features. By simulating these interactions, engineers can optimize mask designs, enhance resolution, and minimize defects.

Advancements in Simulation Techniques

Over the years, lithography process simulators have evolved significantly, incorporating more sophisticated algorithms and computational power to handle the increasing complexity of semiconductor manufacturing. One such advancement is the introduction of rigorous electromagnetic field solvers, which provide a more accurate representation of light-matter interactions at nanometer scales. These solvers are crucial for simulating the effects of polarization, phase, and coherence, which are increasingly relevant as feature sizes shrink.

Additionally, modern simulators integrate computational lithography techniques, such as source-mask optimization (SMO) and inverse lithography technology (ILT). These techniques allow engineers to explore a vast space of potential solutions for improving pattern fidelity and process windows, ultimately leading to better-performing chips.

From Models to Full-Chip Simulation

While early lithography simulators focused on small-scale, localized models, the demand for full-chip simulation has grown as semiconductor designs become more complex. Full-chip simulation involves predicting the performance of an entire integrated circuit, considering factors such as process variability, layout dependencies, and multi-patterning techniques.

Achieving accurate full-chip simulation requires a combination of detailed physical models and scalable computational frameworks. Engineers must account for a multitude of variables, including optical proximity effects, line-edge roughness, and stochastic variations in the photoresist. Advanced simulation tools leverage machine learning and artificial intelligence to efficiently tackle these challenges, providing designers with actionable insights for improving yield and performance.

The Role of Simulation in Design for Manufacturability

Simulation plays a pivotal role in the concept of design for manufacturability (DFM), a methodology aimed at optimizing chip designs to ensure they are robust and manufacturable at scale. By integrating lithography process simulators into the design workflow, engineers can identify potential issues early in the design phase, reducing costly iterations and improving time-to-market.

Simulation enables the exploration of various design trade-offs, such as the balance between resolution and depth of focus, or the impact of different patterning strategies on process stability. By providing a virtual environment for testing and validation, simulators help bridge the gap between design intent and manufacturing reality.

Conclusion

Lithography process simulators have become indispensable tools in the semiconductor industry, enabling the precise prediction and optimization of complex chip designs. From the foundational Hopkins equation to advanced full-chip simulation, these tools empower engineers to overcome the challenges of modern lithography and push the boundaries of what is possible in integrated circuit manufacturing. As technology continues to advance, the role of simulation in ensuring the success of semiconductor innovations will only become more vital.

As photolithography continues to push the boundaries of nanoscale patterning, from EUV and DUV advancements to multi-patterning and maskless lithography, innovation cycles are accelerating—and the IP landscape is becoming more complex than ever.

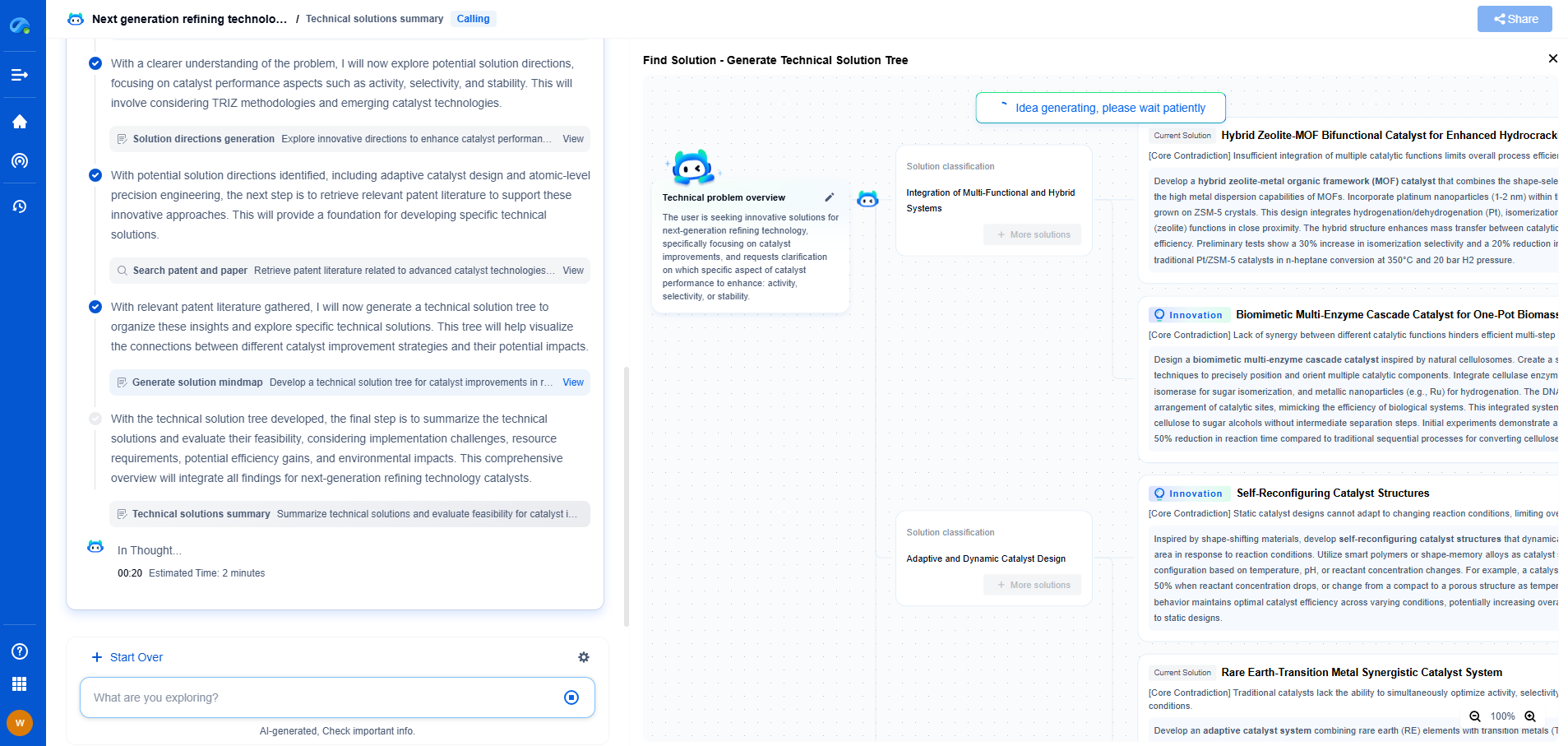

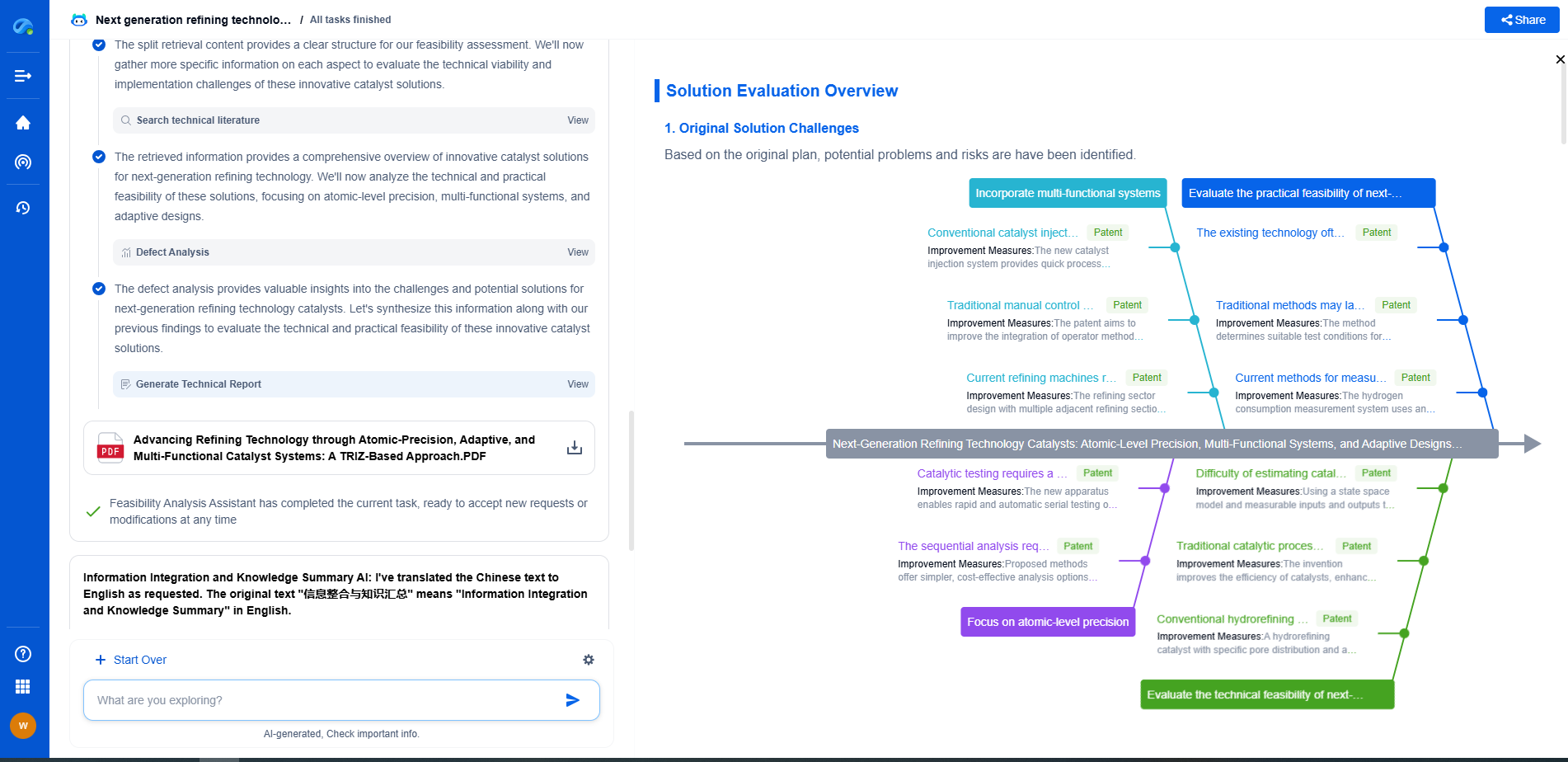

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Whether you're optimizing lithography depth of focus or exploring new materials for sub-3nm nodes, Patsnap Eureka empowers you to make smarter decisions, faster—combining AI efficiency with domain-specific insight.

💡 Start your free trial today and see how Eureka transforms how you discover, evaluate, and act on innovation in photolithography—from idea to impact.

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com