Minimizing Parasitics in Embedded Capacitor Architectures

JUL 9, 2025 |

In the world of electronics, embedded capacitors are integral to the performance of various devices. As technology advances, the demand for miniaturized and high-performance components grows. One critical challenge in this domain is minimizing parasitic effects in embedded capacitor architectures. Parasitics, including parasitic capacitance, resistance, and inductance, can degrade the performance of circuits, leading to signal loss and reduced efficiency. In this article, we delve into strategies to minimize these parasitic effects, thereby improving the performance and reliability of embedded capacitors in electronic devices.

Understanding Parasitics in Embedded Capacitors

Parasitics refer to the unintended physical properties that arise from the electronic component's structure and material. In embedded capacitors, parasitics can manifest due to nearby conductive paths, dielectric materials, and the physical layout of the components. These parasitic elements can introduce unwanted reactance, leading to phase shifts, signal attenuation, and power loss. Understanding the sources of parasitics is the first step in developing strategies to minimize their impact.

Material Selection

The choice of materials plays a crucial role in the performance of embedded capacitors. Using high-dielectric-constant materials can increase capacitance without increasing the physical size of the capacitor. However, these materials should be chosen carefully to minimize losses associated with dielectric absorption and leakage currents. Low-loss dielectric materials can significantly reduce parasitic capacitance and resistance, enhancing the overall performance of the capacitor.

Optimizing Design Layout

The physical layout of embedded capacitors is another critical factor in minimizing parasitics. By carefully designing the geometry and placement of components, engineers can reduce parasitic inductance and resistance. Techniques such as reducing the loop area, using ground planes, and ensuring proper spacing between traces and components can help minimize these unwanted effects. Additionally, symmetrical design can help in balancing parasitic inductances, leading to more stable and predictable circuit behavior.

Advanced Fabrication Techniques

Innovative fabrication techniques can play a significant role in reducing parasitics in embedded capacitor architectures. Methods such as laser trimming, precision etching, and advanced deposition techniques enable the creation of capacitors with tighter tolerances and better control over their parasitic parameters. These techniques help in reducing variations in component properties, leading to improved performance consistency across different units.

Simulation and Modeling

Incorporating simulation and modeling tools early in the design process can help predict and mitigate parasitic effects. Software tools that model electromagnetic interactions and signal integrity can provide valuable insights into potential parasitic issues. By simulating different design approaches and material choices, engineers can optimize their designs before physical prototypes are manufactured, saving time and resources in the development process.

Testing and Measurement

Once the capacitors are fabricated, rigorous testing and measurement are essential to ensure that parasitics are minimized. Techniques such as vector network analysis, time-domain reflectometry, and impedance spectroscopy can be used to measure parasitic capacitance, resistance, and inductance. These measurements enable engineers to verify design assumptions and make necessary adjustments to the manufacturing process if needed.

Conclusion

Minimizing parasitics in embedded capacitor architectures is crucial for enhancing the performance and reliability of electronic devices. By understanding the sources of parasitics and employing strategies such as careful material selection, optimizing design layouts, utilizing advanced fabrication techniques, and incorporating simulation tools, engineers can significantly reduce these unwanted effects. As technology continues to evolve, ongoing research and innovation will be essential to further minimize parasitics and unlock the full potential of embedded capacitors in modern electronic systems.

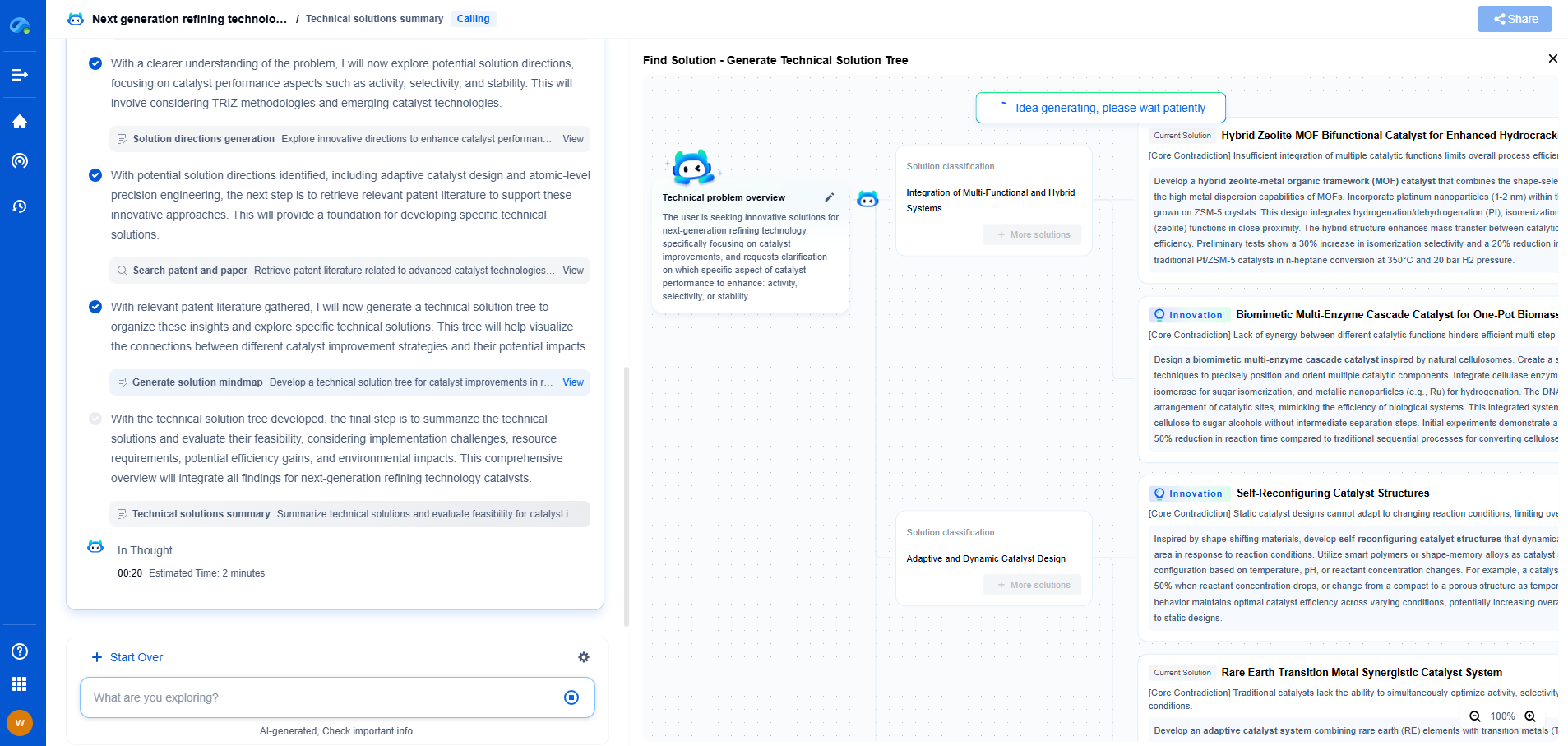

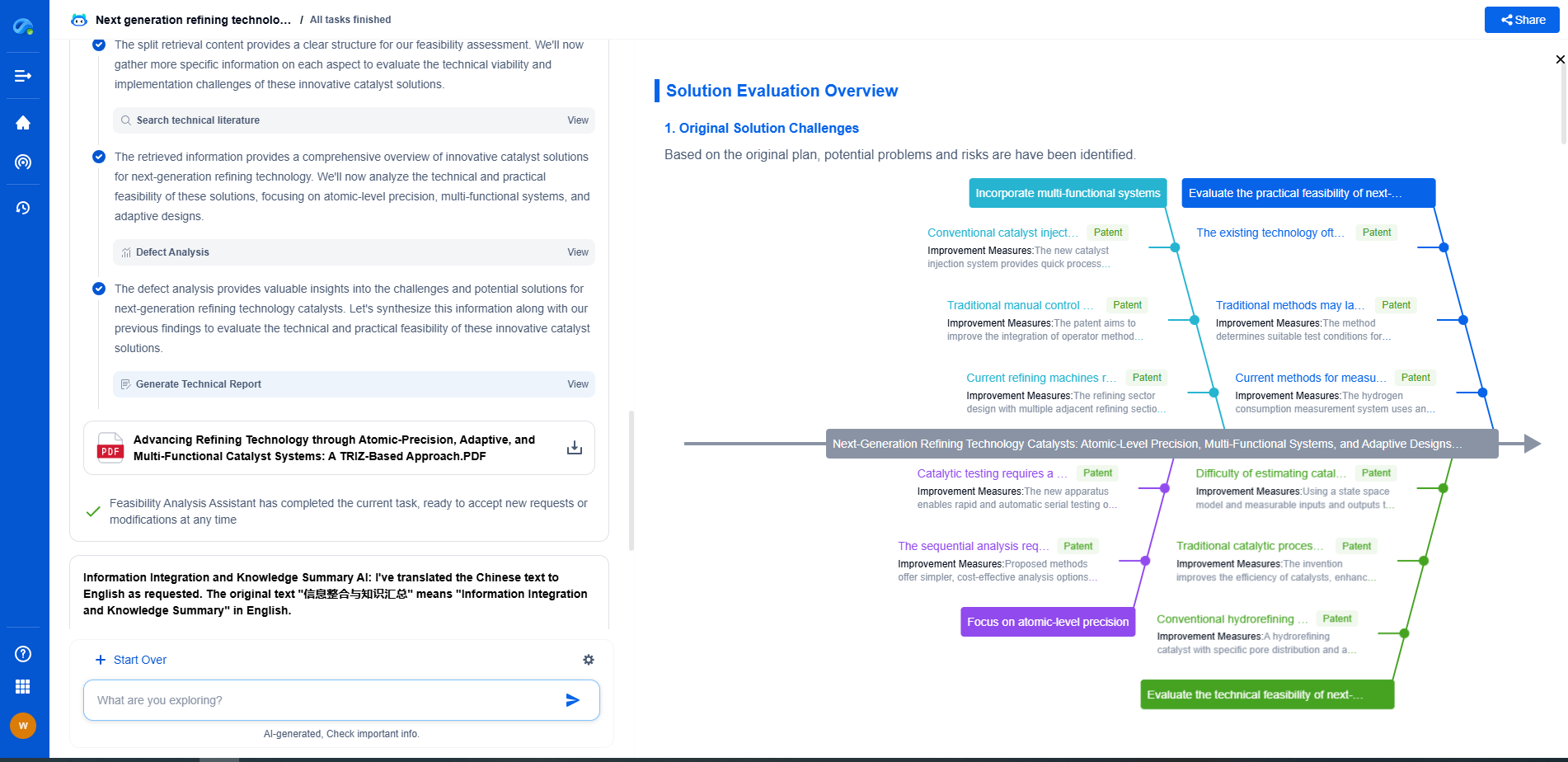

Looking to accelerate your capacitor innovation pipeline?

As capacitor technologies evolve—from miniaturized MLCCs for smartphones to grid-scale energy storage devices—so must the way your team accesses critical knowledge.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Try Patsnap Eureka now and discover a faster, smarter way to research and innovate in capacitor technology.

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com